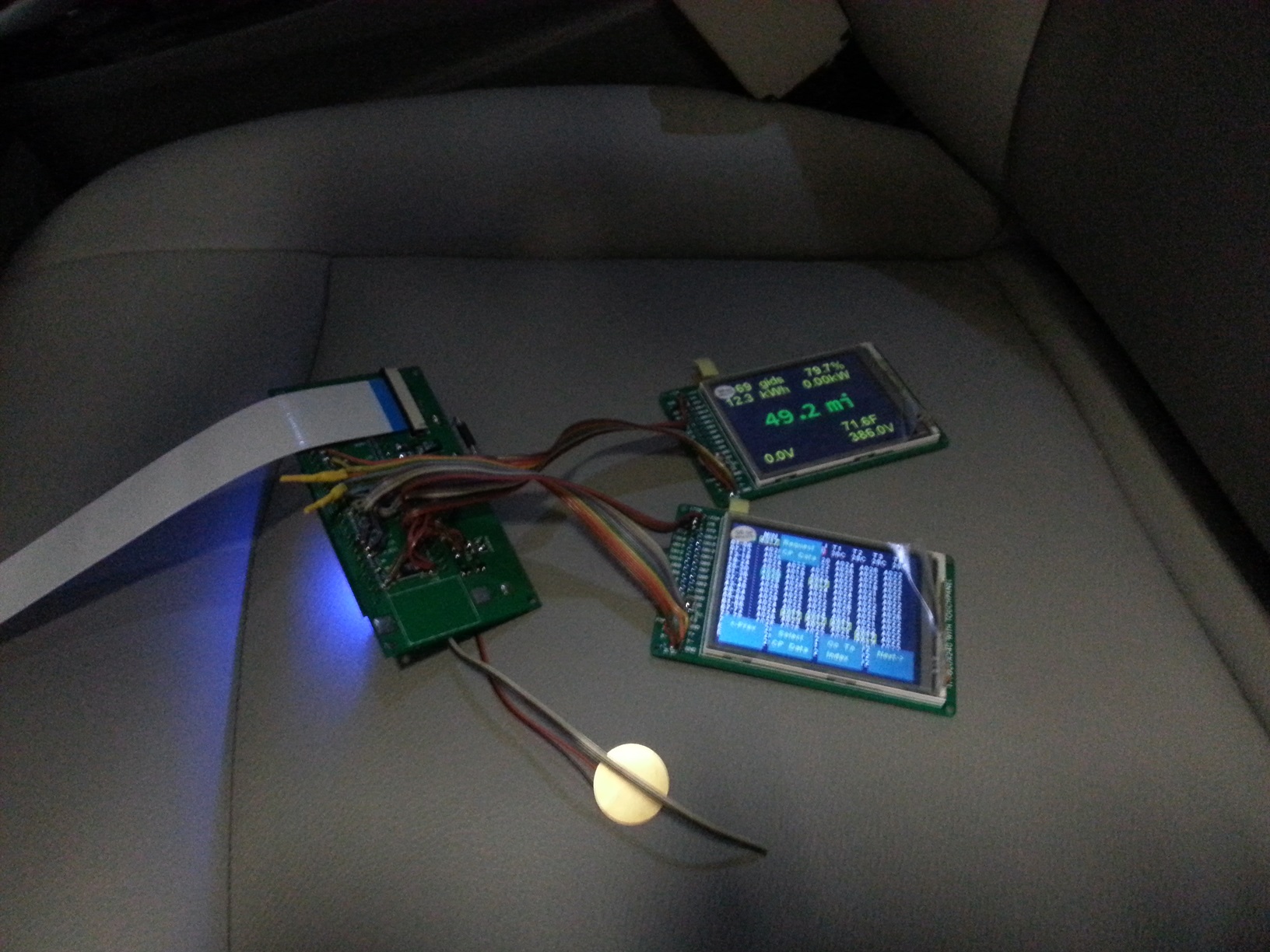

Dual CANbus monitor and instrumentation cluster. Presently tuned for the Nissan Leaf EV.

Dependencies: SPI_TFTx2_ILI9341 TFT_fonts TOUCH_TFTx2_ILI9341 mbed

Fork of CANary_corrupt by

After adding the LPC1768 platform, import as a program and do not select the "update to latest revision" box

User Guide

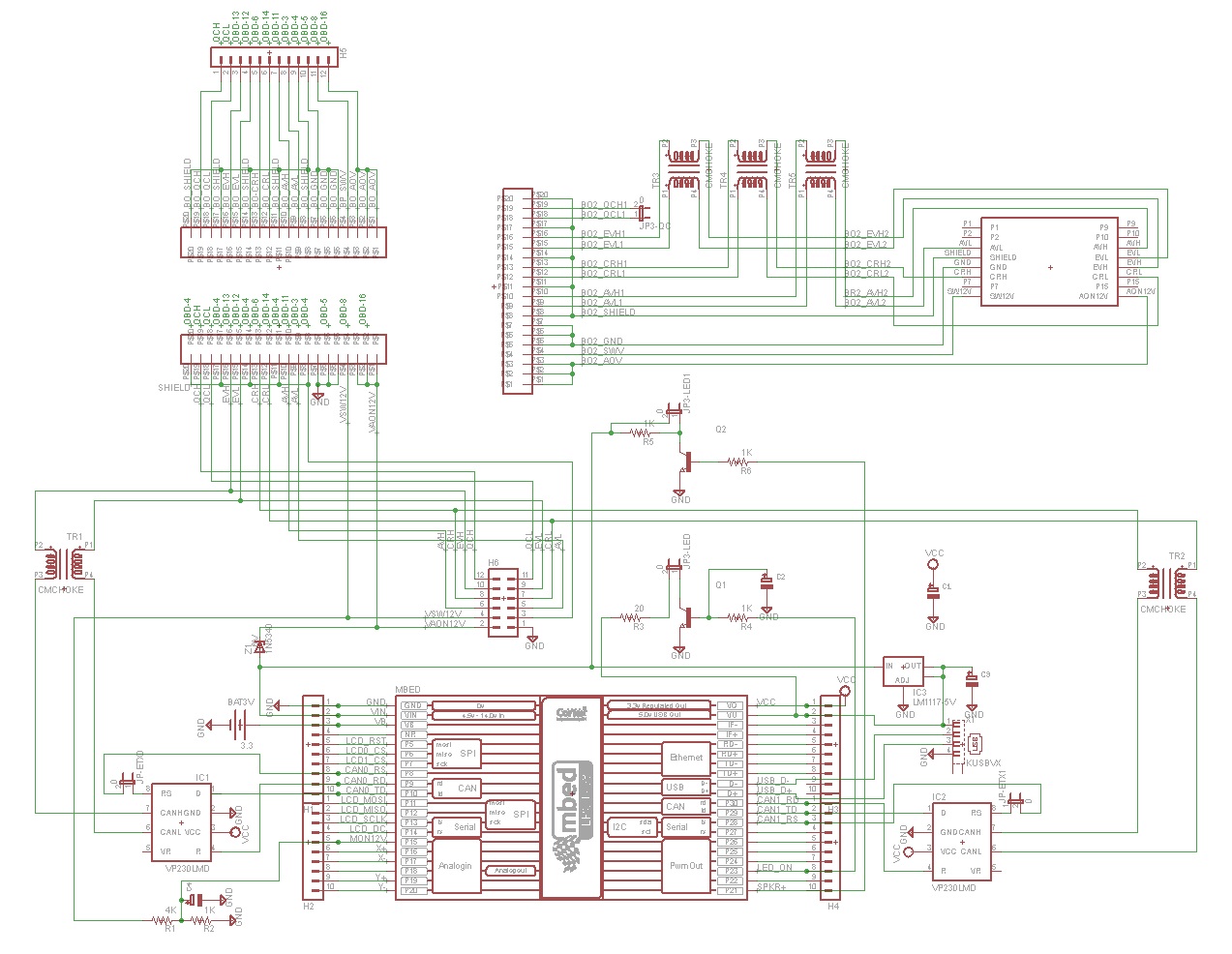

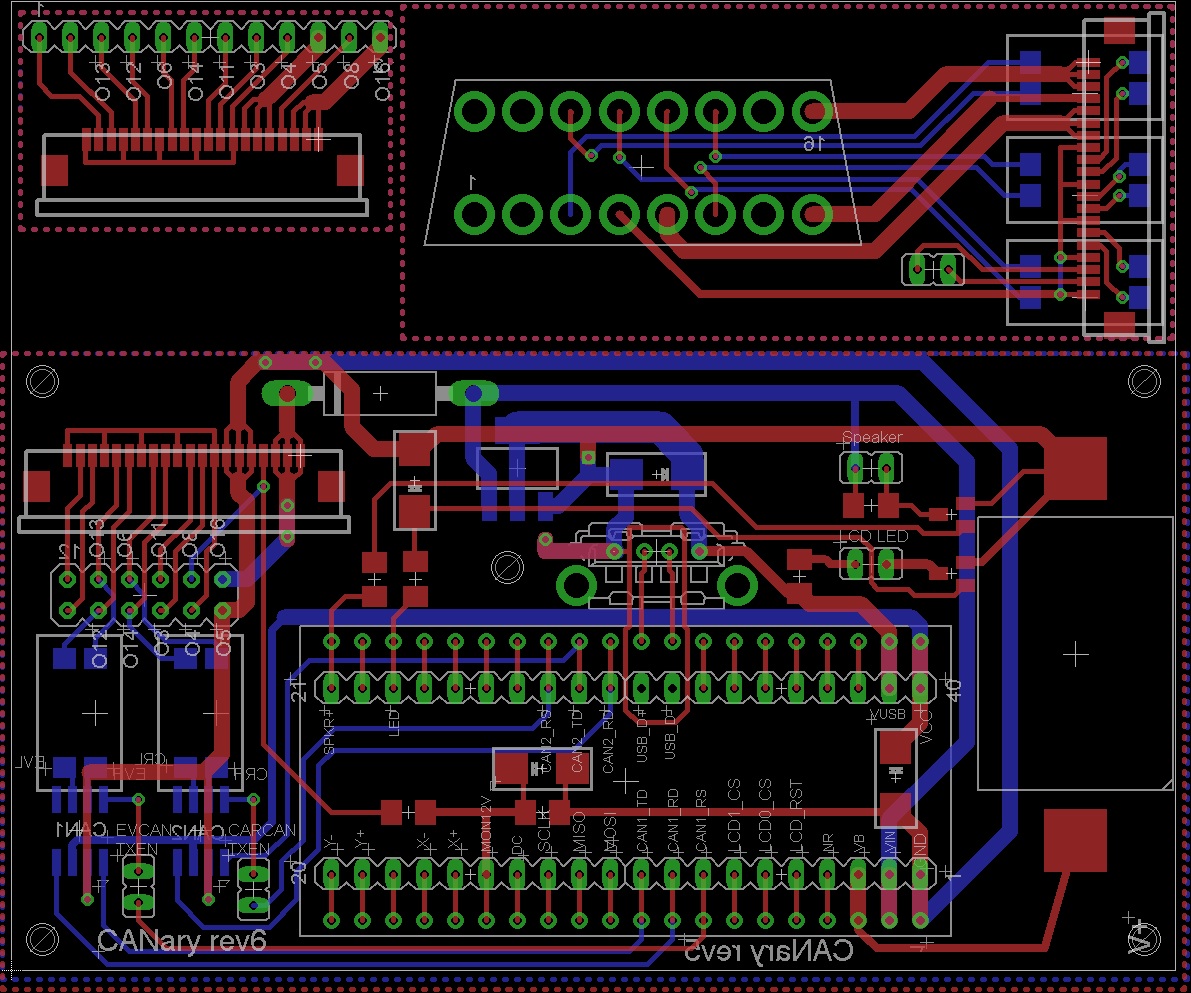

Eagle Schematic and Board design

/media/uploads/TickTock/canaryr6.zip

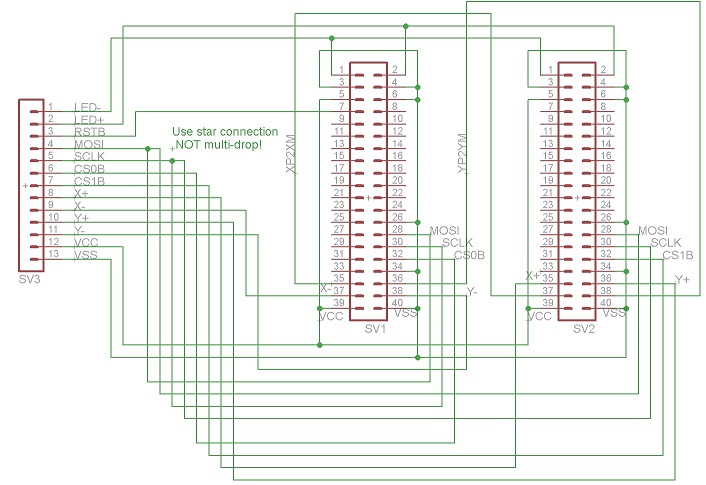

For LCD Rev 1.01:

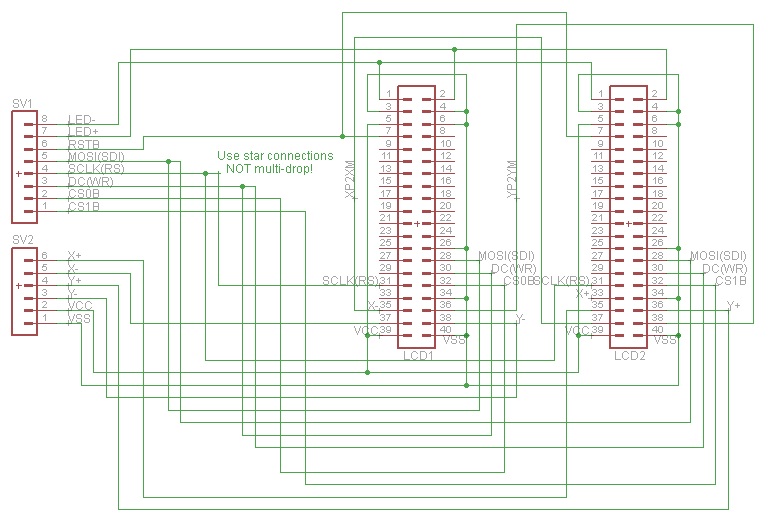

For VCD Rev 2.00:

Parts List

Assembly

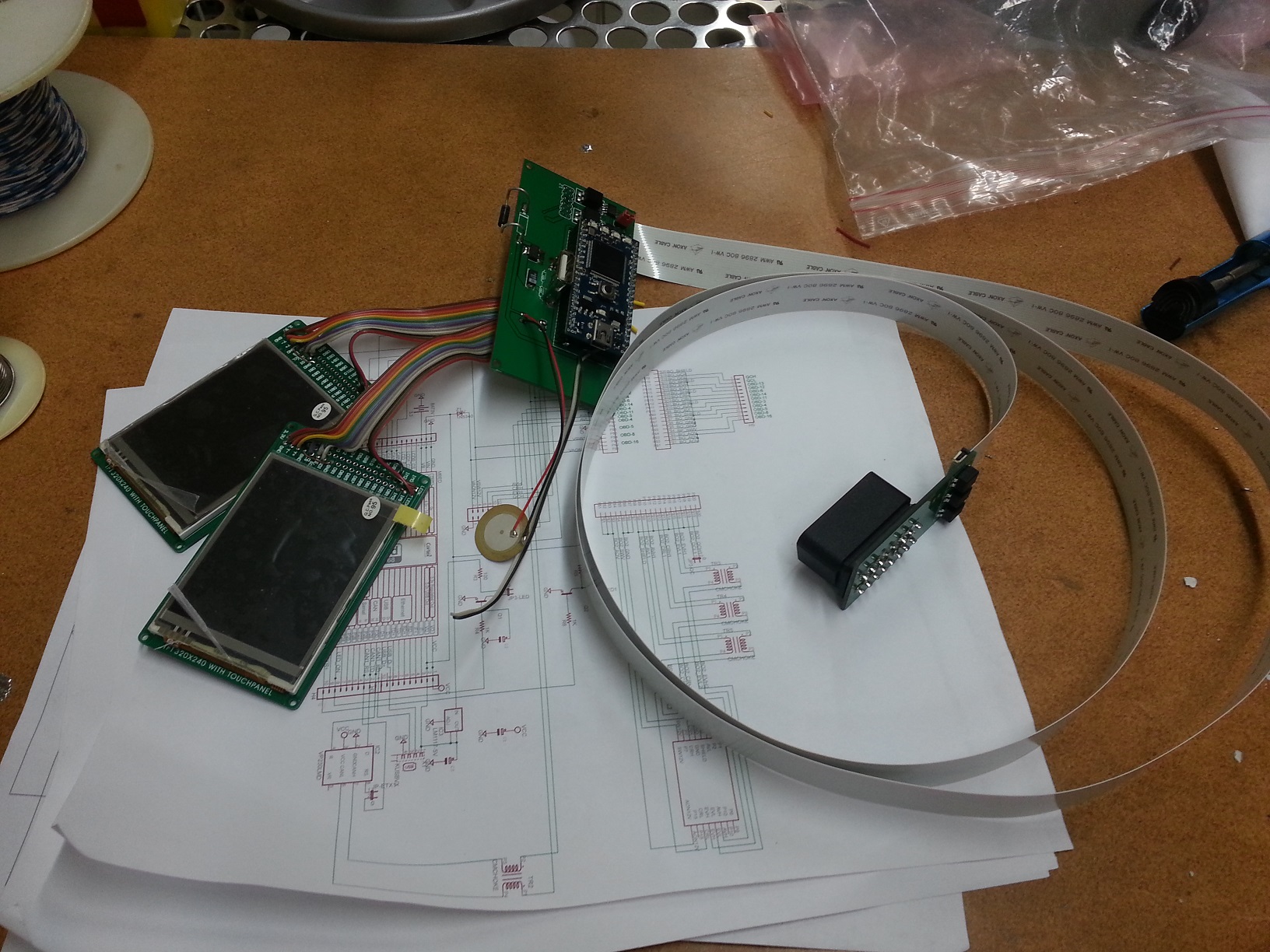

1) LCD Displays

I found ribbon cable is a nice way to organize the wires to the displays. There are two versions of the display and each must be wired differently. The original project used HW REV. 1.01. For that version, you'll need 12 conductors and I connected them in the following order:

| 1 | LED+ |

| 2 | LED- |

| 3 | RST |

| 4 | SDI |

| 5 | WR/SCLK |

| 6 | CS |

| 7 | X+ |

| 8 | X- |

| 9 | Y+ |

| 10 | Y- |

| 11 | VDD |

| 12 | GND |

If, instead, you have HW REV 2.0, you will need 13 conductors with the following order:

| 1 | LED+ |

| 2 | LED- |

| 3 | RST |

| 4 | SDI |

| 5 | RS (SCLK) |

| 6 | WR (DC) |

| 7 | CS |

| 8 | X+ |

| 9 | X- |

| 10 | Y+ |

| 11 | Y- |

| 12 | VDD |

| 13 | GND |

First I connected all the GND connections (2 GND & IM0, IM1, IM3 for REV1.01 or 2 GND, RD, & IM0 for REV2.00). Do not connect the bottom GND until you have the ribbon cable connected. After making all the ribbon cable connections (connecting the GND of the ribbon cable to the bottom GND pad), solder the GND bar from the previous step to the back of the bottom GND connection. Finally, make a connection from the back side 3.3V pin to IM2 for REV1.01 or to IM1,IM2,&IM3 for REV2.00. Take a break and repeat for the second display.

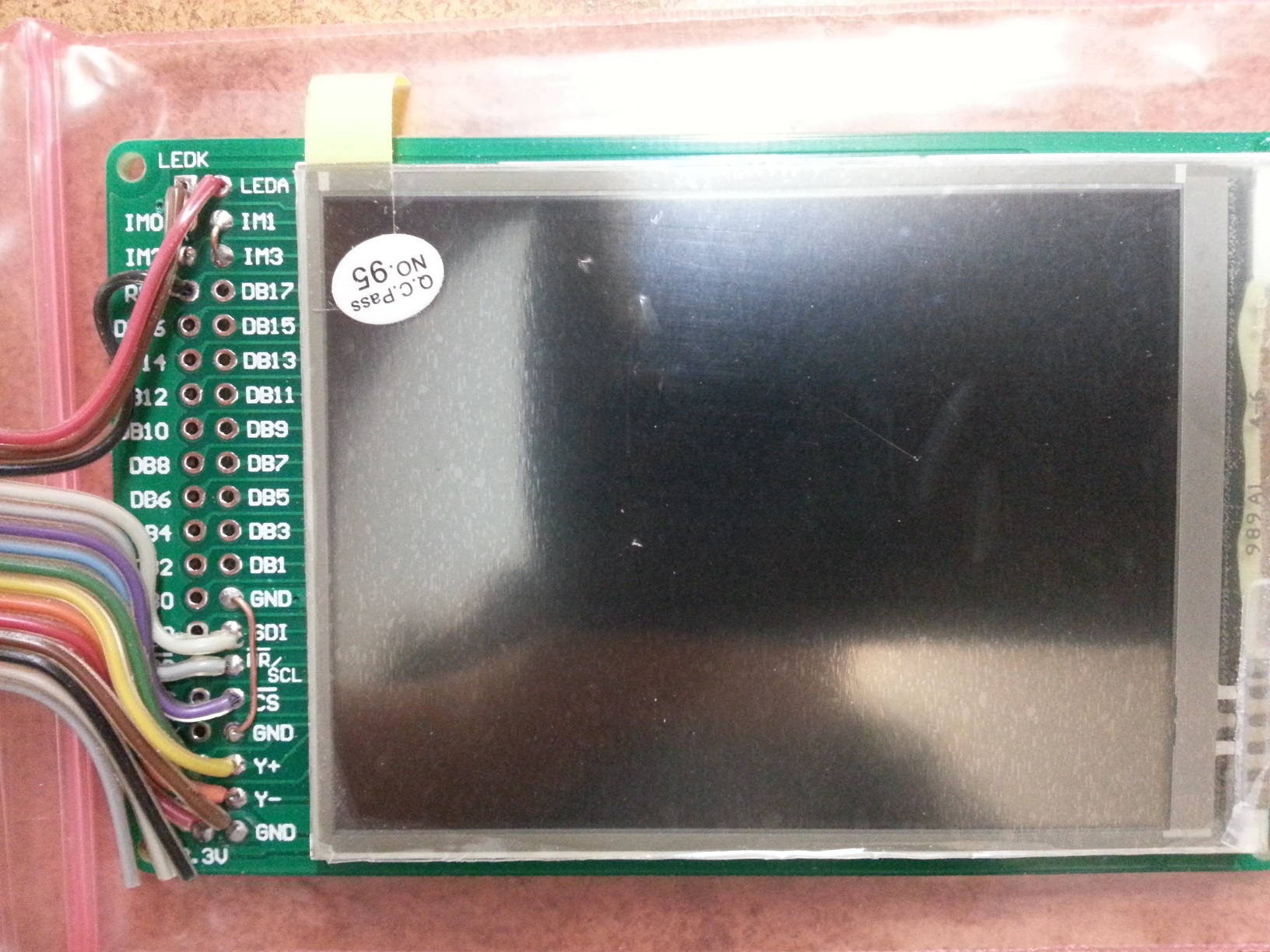

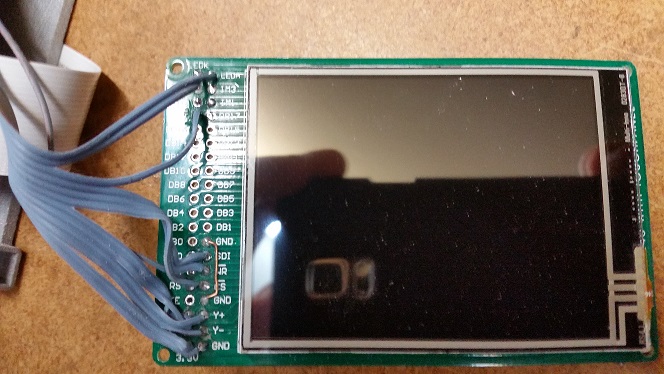

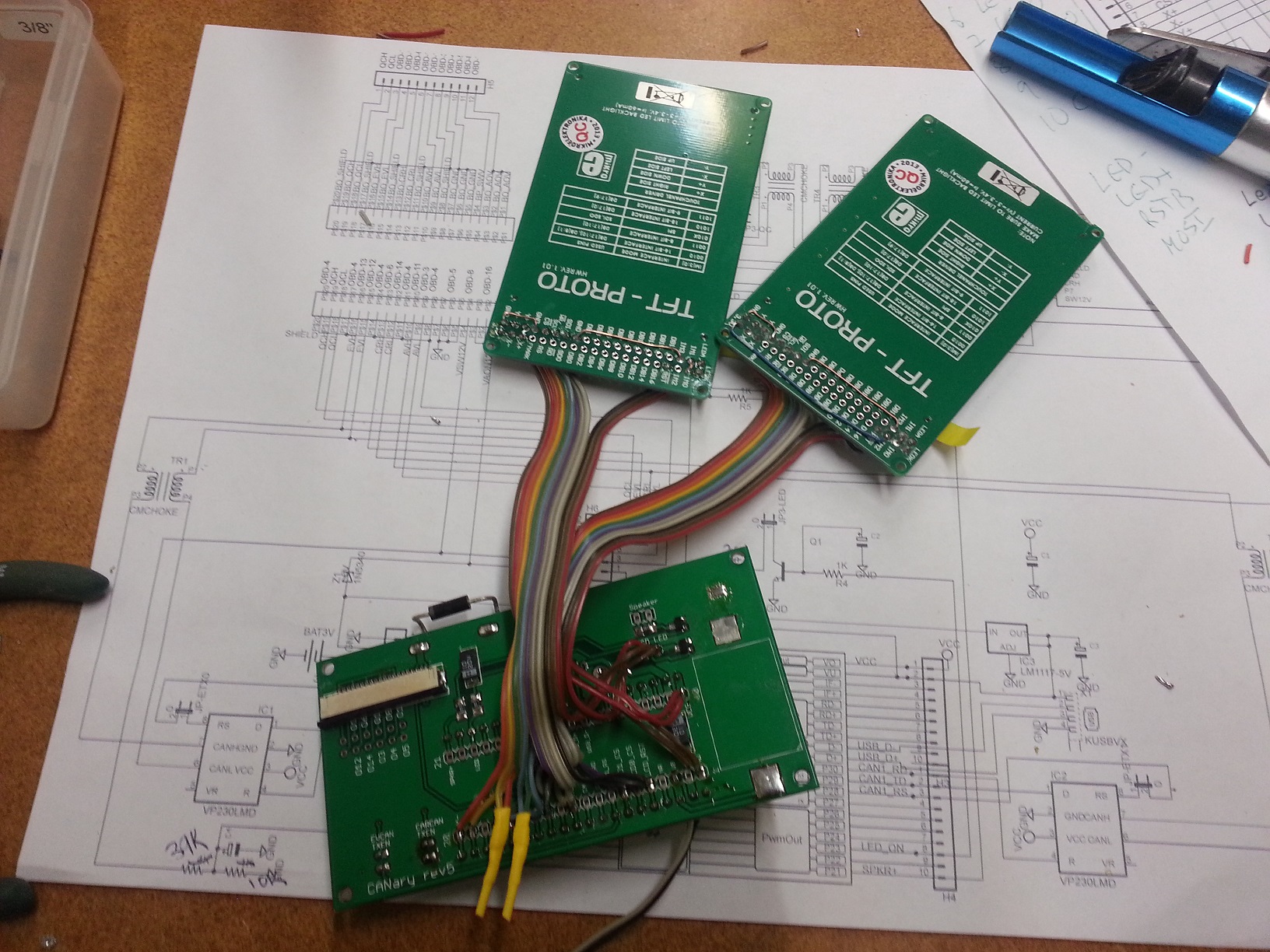

Examples of REV1.01 boards:

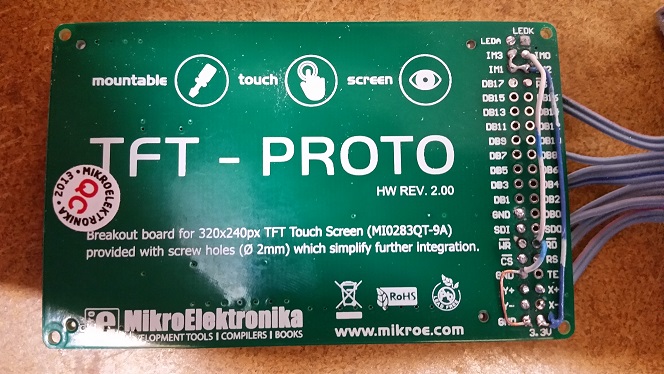

Examples of REV2.00:

Once the two displays are complete combine all wires except CS0, CS1, X+, X-, Y+, and Y-. Connect X- of the left display to X+ of the right. Similarly connect Y- of the left display to Y+ of the right. Insulate any exposed wires.

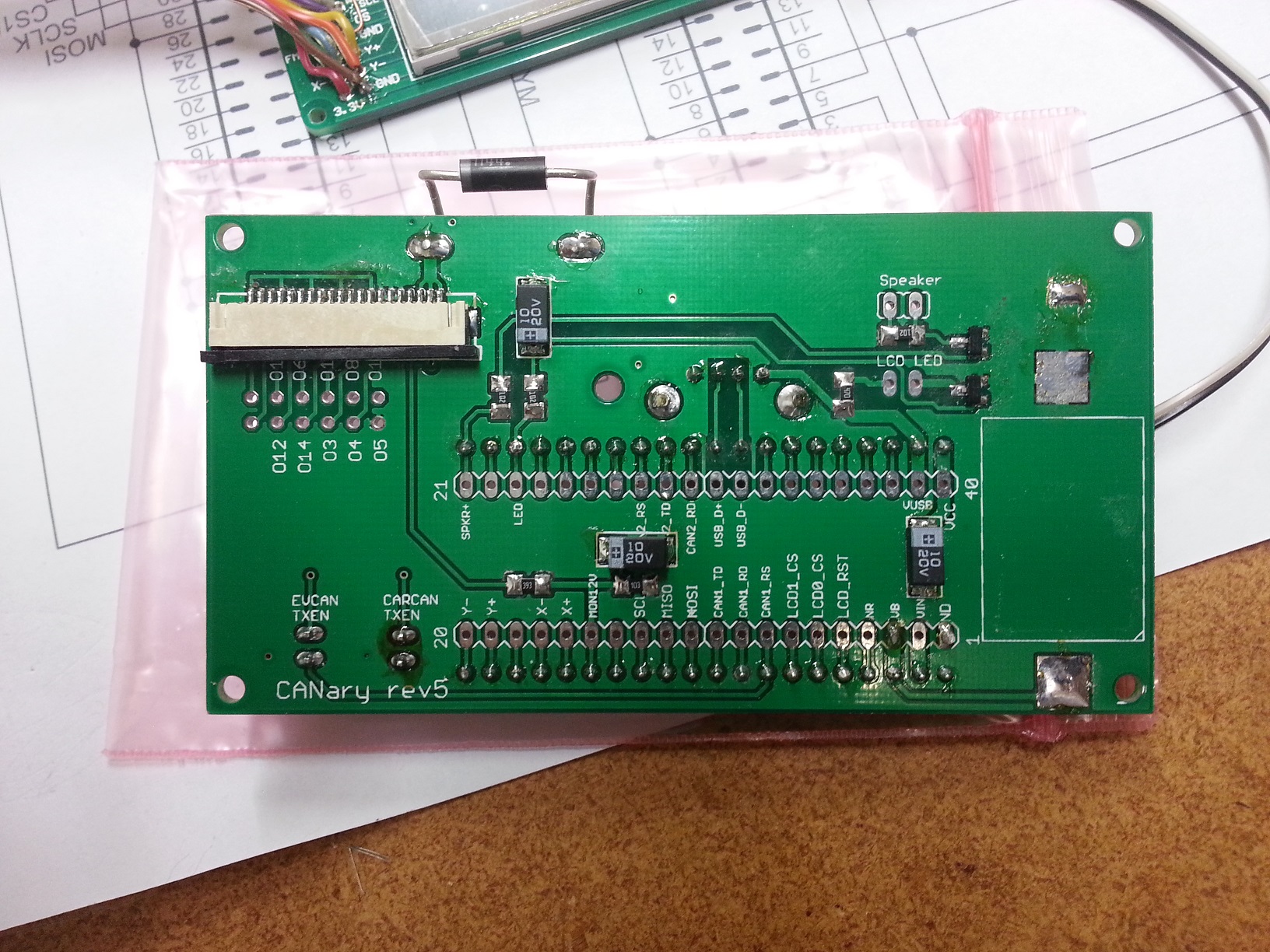

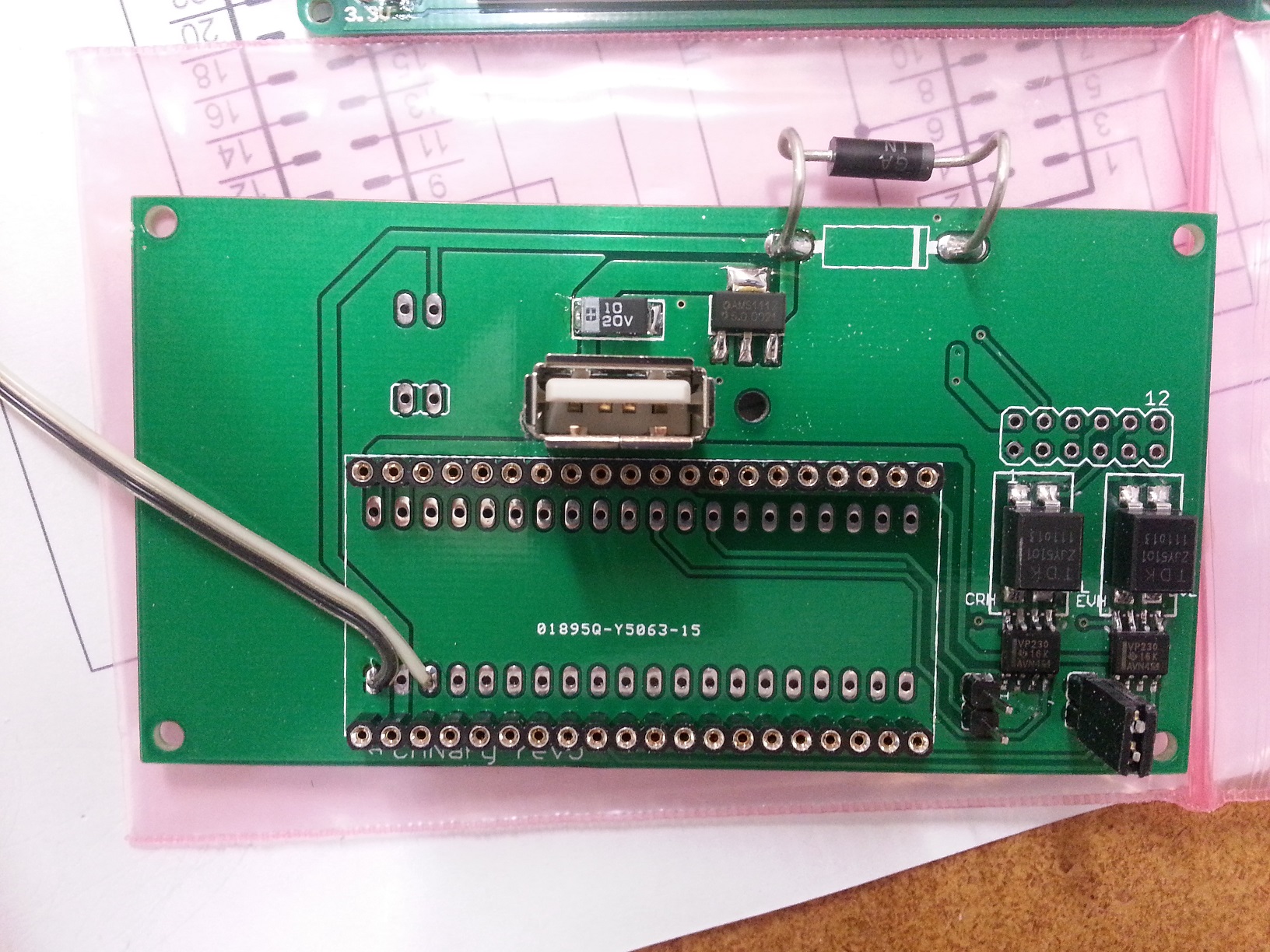

2) PCB

Refer to the schematics to place all the components on the board. If you plan to install into the CANary 3D enclosure, DO NOT install the battery holder or the socket for the mbed and, instead, connect two wires to the VB and GND pads nearby. You will have to install the battery holder against the back wall to avoid interfering with the right-hand display and the mbed will have to be directly soldered. I have not found a socket with a low enough profile to fit in the space provided (depth of enclosure is limited by the space behind the center console). Also, I recommend keeping as much lead as possible on the Zener diode (bending it as shown to clear the back wall). Although it is operating well within parameters, the Zener gets quite hot during extended operation and the leads help dissipate the heat and keep it away from the PCB and other components.Update: Several Zeners have failed resulting in damage to some users boards so I recommend using a DC-DC converter instead to bring the 12V down to 7V.

Once the PCB is populated, solder the LCDs to the PCB. CS0 connects to the right display and CS1 connects to the left.

Update:

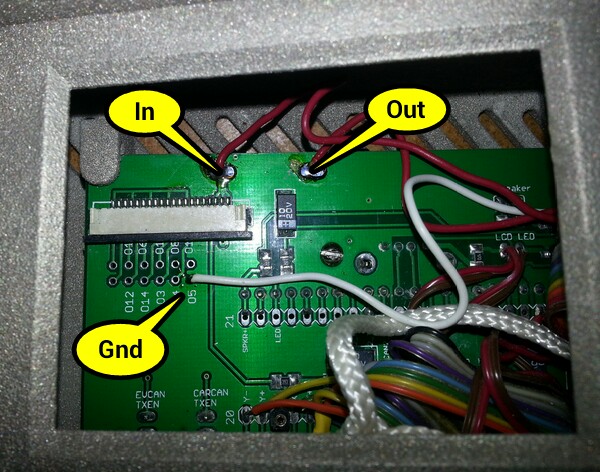

The Zener diodes tended to fail after a few months so I am recommending removing them and replacing with a DC-DC converter. This will run cooler and waste less energy, too. To install, remove the left display panel to gain access to the Zener. From there, the Zener can be removed and it's pads used to connect to the DC-DC converter. I recommend setting the output voltage on the bench before installing since the trim pot is tricky to reach once installed. Set it to 7V. The input can be connected to the left pad previously occupied by the zener and the output can connect to the right. GND(-) can be connected to the bottom right pad on the 2x6 header below the flex cable connector. Make sure the GND wire lies flat so it doesn't interfere with the connection of the flex cable.

Once soldered in place, the DC-DC converter can easily be mounted to the back wall with double sided tape above the battery holder.

3) Testing

| 1) | First step is to buzz out all connections from the LCDs to the pins in the main board |

| 2) | Next check the touch screen connections. On the main board, place an Ohm meter across X+ and X-. You should read 700 Ohms. Repeat for Y+ and Y-. Then test the resistance from X+ to Y+. With nothing touching the screens, it should read >100K Ohms and <1K when touching either screen. |

| 3) | When all connections are checked, solder in the mbed. Download and install the touch2 program http://mbed.org/users/TickTock/code/touch2/ to test the basic operation of the mbed and touch screens. |

| tips: | |

| Touch screen is sensitive - excess flux on X+,X-,Y+,Y- connection on mbed can result in flakey operation | |

| If touch is not working, double-check the LCD0_CS and LCD1_CS are not swapped. LCD0_CS must connect to the CS of the LCD that has X- & Y- connected to the mbed. LCD1_CS must connect to the CS of the LCD that has X+ & Y+ connected to the mbed. | |

| 4) | Once touch2 works, it is time to connect to the OBD connector. I highly recommend double checking all connections from the OBD to the PCB with the cable in place before connecting to the Leaf. Buzz out all the pins in the OBS to make sure none are shorting to each other, Check that the 12V goes to the Zener (and nothing else) and the switched 12V to the resistor divider (and nothing else). Test the ground connection properly connects to ground and nothing else. |

| 5) | Once you are confident there are no shorts or wrong connections from the OBD connector, take a deep breath and plug it into your leaf. Touch2 program should come up and function. Unplug and install the latest CANary firmware. If you have the REV2.00 LCD boards, you will need to edit the precompile.h file in the TOUCH_TFTx2_w9341 library and set USE_ILI9341 to 1. Test all features before installing into the enclosure (gids, cellpair, menu system, logging) since installing and removing from the enclosure is a PITA. |

4) Enclosure

The 3D printer leaves a lot of powder behind - I used a strong spray of water to get it out of all the cracks. The enclosure comes with a rather rough finish. I recommend convincing yourself you like it, then simply lightly sand then paint before assembly. Sanding is very difficult - the nylon is very nicely fused and doesn't want to sand. I tried sandblasting and that didn't work either. I had some limited success with filler and then sanding, but only on the outside - it is too difficult to sand the face.

5) Final Assembly

Make sure you are well rested with lots of patience before attempting assembly. It is a puzzle figuring out how to get both displays and the PCB in place. Enclosure was too expensive for me to keep iterating to optimize for assembly. I ended up snipping the thin display posts shorter and using various tools to push the displays into place. Also, some USB connectors are taller than others. If you have one of the taller ones, you will have to deflect the back wall a bit while inserting the PCB (being careful not to bend the housing) to get it to it's opening in the back wall. Do use a screw in the provided post to secure the PCB as USB insertion will otherwise dislodge it.

I added an additional safety line which wraps around the center post to prevent the enclosure from becoming a projectile in the event of an accident.

Installed:

Installed:

PowerControl/EthernetPowerControl.h

- Committer:

- TickTock

- Date:

- 2015-07-01

- Revision:

- 208:bfb6b68d1677

- Parent:

- 4:8d7759f4fe7a

File content as of revision 208:bfb6b68d1677:

/* mbed PowerControl Library

* Copyright (c) 2010 Michael Wei

*/

#ifndef MBED_POWERCONTROL_ETH_H

#define MBED_POWERCONTROL_ETH_H

#include "mbed.h"

#include "PowerControl.h"

#define PHY_REG_BMCR_POWERDOWN 0xB

#define PHY_REG_EDCR_ENABLE 0xF

void EMAC_Init();

static unsigned short read_PHY (unsigned int PhyReg);

static void write_PHY (unsigned int PhyReg, unsigned short Value);

void PHY_PowerDown(void);

void PHY_PowerUp(void);

void PHY_EnergyDetect_Enable(void);

void PHY_EnergyDetect_Disable(void);

//From NXP Sample Code .... Probably from KEIL sample code

/* EMAC Memory Buffer configuration for 16K Ethernet RAM. */

#define NUM_RX_FRAG 4 /* Num.of RX Fragments 4*1536= 6.0kB */

#define NUM_TX_FRAG 3 /* Num.of TX Fragments 3*1536= 4.6kB */

#define ETH_FRAG_SIZE 1536 /* Packet Fragment size 1536 Bytes */

#define ETH_MAX_FLEN 1536 /* Max. Ethernet Frame Size */

/* EMAC variables located in 16K Ethernet SRAM */

#define RX_DESC_BASE 0x20080000

#define RX_STAT_BASE (RX_DESC_BASE + NUM_RX_FRAG*8)

#define TX_DESC_BASE (RX_STAT_BASE + NUM_RX_FRAG*8)

#define TX_STAT_BASE (TX_DESC_BASE + NUM_TX_FRAG*8)

#define RX_BUF_BASE (TX_STAT_BASE + NUM_TX_FRAG*4)

#define TX_BUF_BASE (RX_BUF_BASE + NUM_RX_FRAG*ETH_FRAG_SIZE)

/* RX and TX descriptor and status definitions. */

#define RX_DESC_PACKET(i) (*(unsigned int *)(RX_DESC_BASE + 8*i))

#define RX_DESC_CTRL(i) (*(unsigned int *)(RX_DESC_BASE+4 + 8*i))

#define RX_STAT_INFO(i) (*(unsigned int *)(RX_STAT_BASE + 8*i))

#define RX_STAT_HASHCRC(i) (*(unsigned int *)(RX_STAT_BASE+4 + 8*i))

#define TX_DESC_PACKET(i) (*(unsigned int *)(TX_DESC_BASE + 8*i))

#define TX_DESC_CTRL(i) (*(unsigned int *)(TX_DESC_BASE+4 + 8*i))

#define TX_STAT_INFO(i) (*(unsigned int *)(TX_STAT_BASE + 4*i))

#define RX_BUF(i) (RX_BUF_BASE + ETH_FRAG_SIZE*i)

#define TX_BUF(i) (TX_BUF_BASE + ETH_FRAG_SIZE*i)

/* MAC Configuration Register 1 */

#define MAC1_REC_EN 0x00000001 /* Receive Enable */

#define MAC1_PASS_ALL 0x00000002 /* Pass All Receive Frames */

#define MAC1_RX_FLOWC 0x00000004 /* RX Flow Control */

#define MAC1_TX_FLOWC 0x00000008 /* TX Flow Control */

#define MAC1_LOOPB 0x00000010 /* Loop Back Mode */

#define MAC1_RES_TX 0x00000100 /* Reset TX Logic */

#define MAC1_RES_MCS_TX 0x00000200 /* Reset MAC TX Control Sublayer */

#define MAC1_RES_RX 0x00000400 /* Reset RX Logic */

#define MAC1_RES_MCS_RX 0x00000800 /* Reset MAC RX Control Sublayer */

#define MAC1_SIM_RES 0x00004000 /* Simulation Reset */

#define MAC1_SOFT_RES 0x00008000 /* Soft Reset MAC */

/* MAC Configuration Register 2 */

#define MAC2_FULL_DUP 0x00000001 /* Full Duplex Mode */

#define MAC2_FRM_LEN_CHK 0x00000002 /* Frame Length Checking */

#define MAC2_HUGE_FRM_EN 0x00000004 /* Huge Frame Enable */

#define MAC2_DLY_CRC 0x00000008 /* Delayed CRC Mode */

#define MAC2_CRC_EN 0x00000010 /* Append CRC to every Frame */

#define MAC2_PAD_EN 0x00000020 /* Pad all Short Frames */

#define MAC2_VLAN_PAD_EN 0x00000040 /* VLAN Pad Enable */

#define MAC2_ADET_PAD_EN 0x00000080 /* Auto Detect Pad Enable */

#define MAC2_PPREAM_ENF 0x00000100 /* Pure Preamble Enforcement */

#define MAC2_LPREAM_ENF 0x00000200 /* Long Preamble Enforcement */

#define MAC2_NO_BACKOFF 0x00001000 /* No Backoff Algorithm */

#define MAC2_BACK_PRESSURE 0x00002000 /* Backoff Presurre / No Backoff */

#define MAC2_EXCESS_DEF 0x00004000 /* Excess Defer */

/* Back-to-Back Inter-Packet-Gap Register */

#define IPGT_FULL_DUP 0x00000015 /* Recommended value for Full Duplex */

#define IPGT_HALF_DUP 0x00000012 /* Recommended value for Half Duplex */

/* Non Back-to-Back Inter-Packet-Gap Register */

#define IPGR_DEF 0x00000012 /* Recommended value */

/* Collision Window/Retry Register */

#define CLRT_DEF 0x0000370F /* Default value */

/* PHY Support Register */

#define SUPP_SPEED 0x00000100 /* Reduced MII Logic Current Speed */

#define SUPP_RES_RMII 0x00000800 /* Reset Reduced MII Logic */

/* Test Register */

#define TEST_SHCUT_PQUANTA 0x00000001 /* Shortcut Pause Quanta */

#define TEST_TST_PAUSE 0x00000002 /* Test Pause */

#define TEST_TST_BACKP 0x00000004 /* Test Back Pressure */

/* MII Management Configuration Register */

#define MCFG_SCAN_INC 0x00000001 /* Scan Increment PHY Address */

#define MCFG_SUPP_PREAM 0x00000002 /* Suppress Preamble */

#define MCFG_CLK_SEL 0x0000001C /* Clock Select Mask */

#define MCFG_RES_MII 0x00008000 /* Reset MII Management Hardware */

/* MII Management Command Register */

#define MCMD_READ 0x00000001 /* MII Read */

#define MCMD_SCAN 0x00000002 /* MII Scan continuously */

#define MII_WR_TOUT 0x00050000 /* MII Write timeout count */

#define MII_RD_TOUT 0x00050000 /* MII Read timeout count */

/* MII Management Address Register */

#define MADR_REG_ADR 0x0000001F /* MII Register Address Mask */

#define MADR_PHY_ADR 0x00001F00 /* PHY Address Mask */

/* MII Management Indicators Register */

#define MIND_BUSY 0x00000001 /* MII is Busy */

#define MIND_SCAN 0x00000002 /* MII Scanning in Progress */

#define MIND_NOT_VAL 0x00000004 /* MII Read Data not valid */

#define MIND_MII_LINK_FAIL 0x00000008 /* MII Link Failed */

/* Command Register */

#define CR_RX_EN 0x00000001 /* Enable Receive */

#define CR_TX_EN 0x00000002 /* Enable Transmit */

#define CR_REG_RES 0x00000008 /* Reset Host Registers */

#define CR_TX_RES 0x00000010 /* Reset Transmit Datapath */

#define CR_RX_RES 0x00000020 /* Reset Receive Datapath */

#define CR_PASS_RUNT_FRM 0x00000040 /* Pass Runt Frames */

#define CR_PASS_RX_FILT 0x00000080 /* Pass RX Filter */

#define CR_TX_FLOW_CTRL 0x00000100 /* TX Flow Control */

#define CR_RMII 0x00000200 /* Reduced MII Interface */

#define CR_FULL_DUP 0x00000400 /* Full Duplex */

/* Status Register */

#define SR_RX_EN 0x00000001 /* Enable Receive */

#define SR_TX_EN 0x00000002 /* Enable Transmit */

/* Transmit Status Vector 0 Register */

#define TSV0_CRC_ERR 0x00000001 /* CRC error */

#define TSV0_LEN_CHKERR 0x00000002 /* Length Check Error */

#define TSV0_LEN_OUTRNG 0x00000004 /* Length Out of Range */

#define TSV0_DONE 0x00000008 /* Tramsmission Completed */

#define TSV0_MCAST 0x00000010 /* Multicast Destination */

#define TSV0_BCAST 0x00000020 /* Broadcast Destination */

#define TSV0_PKT_DEFER 0x00000040 /* Packet Deferred */

#define TSV0_EXC_DEFER 0x00000080 /* Excessive Packet Deferral */

#define TSV0_EXC_COLL 0x00000100 /* Excessive Collision */

#define TSV0_LATE_COLL 0x00000200 /* Late Collision Occured */

#define TSV0_GIANT 0x00000400 /* Giant Frame */

#define TSV0_UNDERRUN 0x00000800 /* Buffer Underrun */

#define TSV0_BYTES 0x0FFFF000 /* Total Bytes Transferred */

#define TSV0_CTRL_FRAME 0x10000000 /* Control Frame */

#define TSV0_PAUSE 0x20000000 /* Pause Frame */

#define TSV0_BACK_PRESS 0x40000000 /* Backpressure Method Applied */

#define TSV0_VLAN 0x80000000 /* VLAN Frame */

/* Transmit Status Vector 1 Register */

#define TSV1_BYTE_CNT 0x0000FFFF /* Transmit Byte Count */

#define TSV1_COLL_CNT 0x000F0000 /* Transmit Collision Count */

/* Receive Status Vector Register */

#define RSV_BYTE_CNT 0x0000FFFF /* Receive Byte Count */

#define RSV_PKT_IGNORED 0x00010000 /* Packet Previously Ignored */

#define RSV_RXDV_SEEN 0x00020000 /* RXDV Event Previously Seen */

#define RSV_CARR_SEEN 0x00040000 /* Carrier Event Previously Seen */

#define RSV_REC_CODEV 0x00080000 /* Receive Code Violation */

#define RSV_CRC_ERR 0x00100000 /* CRC Error */

#define RSV_LEN_CHKERR 0x00200000 /* Length Check Error */

#define RSV_LEN_OUTRNG 0x00400000 /* Length Out of Range */

#define RSV_REC_OK 0x00800000 /* Frame Received OK */

#define RSV_MCAST 0x01000000 /* Multicast Frame */

#define RSV_BCAST 0x02000000 /* Broadcast Frame */

#define RSV_DRIB_NIBB 0x04000000 /* Dribble Nibble */

#define RSV_CTRL_FRAME 0x08000000 /* Control Frame */

#define RSV_PAUSE 0x10000000 /* Pause Frame */

#define RSV_UNSUPP_OPC 0x20000000 /* Unsupported Opcode */

#define RSV_VLAN 0x40000000 /* VLAN Frame */

/* Flow Control Counter Register */

#define FCC_MIRR_CNT 0x0000FFFF /* Mirror Counter */

#define FCC_PAUSE_TIM 0xFFFF0000 /* Pause Timer */

/* Flow Control Status Register */

#define FCS_MIRR_CNT 0x0000FFFF /* Mirror Counter Current */

/* Receive Filter Control Register */

#define RFC_UCAST_EN 0x00000001 /* Accept Unicast Frames Enable */

#define RFC_BCAST_EN 0x00000002 /* Accept Broadcast Frames Enable */

#define RFC_MCAST_EN 0x00000004 /* Accept Multicast Frames Enable */

#define RFC_UCAST_HASH_EN 0x00000008 /* Accept Unicast Hash Filter Frames */

#define RFC_MCAST_HASH_EN 0x00000010 /* Accept Multicast Hash Filter Fram.*/

#define RFC_PERFECT_EN 0x00000020 /* Accept Perfect Match Enable */

#define RFC_MAGP_WOL_EN 0x00001000 /* Magic Packet Filter WoL Enable */

#define RFC_PFILT_WOL_EN 0x00002000 /* Perfect Filter WoL Enable */

/* Receive Filter WoL Status/Clear Registers */

#define WOL_UCAST 0x00000001 /* Unicast Frame caused WoL */

#define WOL_BCAST 0x00000002 /* Broadcast Frame caused WoL */

#define WOL_MCAST 0x00000004 /* Multicast Frame caused WoL */

#define WOL_UCAST_HASH 0x00000008 /* Unicast Hash Filter Frame WoL */

#define WOL_MCAST_HASH 0x00000010 /* Multicast Hash Filter Frame WoL */

#define WOL_PERFECT 0x00000020 /* Perfect Filter WoL */

#define WOL_RX_FILTER 0x00000080 /* RX Filter caused WoL */

#define WOL_MAG_PACKET 0x00000100 /* Magic Packet Filter caused WoL */

/* Interrupt Status/Enable/Clear/Set Registers */

#define INT_RX_OVERRUN 0x00000001 /* Overrun Error in RX Queue */

#define INT_RX_ERR 0x00000002 /* Receive Error */

#define INT_RX_FIN 0x00000004 /* RX Finished Process Descriptors */

#define INT_RX_DONE 0x00000008 /* Receive Done */

#define INT_TX_UNDERRUN 0x00000010 /* Transmit Underrun */

#define INT_TX_ERR 0x00000020 /* Transmit Error */

#define INT_TX_FIN 0x00000040 /* TX Finished Process Descriptors */

#define INT_TX_DONE 0x00000080 /* Transmit Done */

#define INT_SOFT_INT 0x00001000 /* Software Triggered Interrupt */

#define INT_WAKEUP 0x00002000 /* Wakeup Event Interrupt */

/* Power Down Register */

#define PD_POWER_DOWN 0x80000000 /* Power Down MAC */

/* RX Descriptor Control Word */

#define RCTRL_SIZE 0x000007FF /* Buffer size mask */

#define RCTRL_INT 0x80000000 /* Generate RxDone Interrupt */

/* RX Status Hash CRC Word */

#define RHASH_SA 0x000001FF /* Hash CRC for Source Address */

#define RHASH_DA 0x001FF000 /* Hash CRC for Destination Address */

/* RX Status Information Word */

#define RINFO_SIZE 0x000007FF /* Data size in bytes */

#define RINFO_CTRL_FRAME 0x00040000 /* Control Frame */

#define RINFO_VLAN 0x00080000 /* VLAN Frame */

#define RINFO_FAIL_FILT 0x00100000 /* RX Filter Failed */

#define RINFO_MCAST 0x00200000 /* Multicast Frame */

#define RINFO_BCAST 0x00400000 /* Broadcast Frame */

#define RINFO_CRC_ERR 0x00800000 /* CRC Error in Frame */

#define RINFO_SYM_ERR 0x01000000 /* Symbol Error from PHY */

#define RINFO_LEN_ERR 0x02000000 /* Length Error */

#define RINFO_RANGE_ERR 0x04000000 /* Range Error (exceeded max. size) */

#define RINFO_ALIGN_ERR 0x08000000 /* Alignment Error */

#define RINFO_OVERRUN 0x10000000 /* Receive overrun */

#define RINFO_NO_DESCR 0x20000000 /* No new Descriptor available */

#define RINFO_LAST_FLAG 0x40000000 /* Last Fragment in Frame */

#define RINFO_ERR 0x80000000 /* Error Occured (OR of all errors) */

#define RINFO_ERR_MASK (RINFO_FAIL_FILT | RINFO_CRC_ERR | RINFO_SYM_ERR | \

RINFO_LEN_ERR | RINFO_ALIGN_ERR | RINFO_OVERRUN)

/* TX Descriptor Control Word */

#define TCTRL_SIZE 0x000007FF /* Size of data buffer in bytes */

#define TCTRL_OVERRIDE 0x04000000 /* Override Default MAC Registers */

#define TCTRL_HUGE 0x08000000 /* Enable Huge Frame */

#define TCTRL_PAD 0x10000000 /* Pad short Frames to 64 bytes */

#define TCTRL_CRC 0x20000000 /* Append a hardware CRC to Frame */

#define TCTRL_LAST 0x40000000 /* Last Descriptor for TX Frame */

#define TCTRL_INT 0x80000000 /* Generate TxDone Interrupt */

/* TX Status Information Word */

#define TINFO_COL_CNT 0x01E00000 /* Collision Count */

#define TINFO_DEFER 0x02000000 /* Packet Deferred (not an error) */

#define TINFO_EXCESS_DEF 0x04000000 /* Excessive Deferral */

#define TINFO_EXCESS_COL 0x08000000 /* Excessive Collision */

#define TINFO_LATE_COL 0x10000000 /* Late Collision Occured */

#define TINFO_UNDERRUN 0x20000000 /* Transmit Underrun */

#define TINFO_NO_DESCR 0x40000000 /* No new Descriptor available */

#define TINFO_ERR 0x80000000 /* Error Occured (OR of all errors) */

/* DP83848C PHY Registers */

#define PHY_REG_BMCR 0x00 /* Basic Mode Control Register */

#define PHY_REG_BMSR 0x01 /* Basic Mode Status Register */

#define PHY_REG_IDR1 0x02 /* PHY Identifier 1 */

#define PHY_REG_IDR2 0x03 /* PHY Identifier 2 */

#define PHY_REG_ANAR 0x04 /* Auto-Negotiation Advertisement */

#define PHY_REG_ANLPAR 0x05 /* Auto-Neg. Link Partner Abitily */

#define PHY_REG_ANER 0x06 /* Auto-Neg. Expansion Register */

#define PHY_REG_ANNPTR 0x07 /* Auto-Neg. Next Page TX */

/* PHY Extended Registers */

#define PHY_REG_STS 0x10 /* Status Register */

#define PHY_REG_MICR 0x11 /* MII Interrupt Control Register */

#define PHY_REG_MISR 0x12 /* MII Interrupt Status Register */

#define PHY_REG_FCSCR 0x14 /* False Carrier Sense Counter */

#define PHY_REG_RECR 0x15 /* Receive Error Counter */

#define PHY_REG_PCSR 0x16 /* PCS Sublayer Config. and Status */

#define PHY_REG_RBR 0x17 /* RMII and Bypass Register */

#define PHY_REG_LEDCR 0x18 /* LED Direct Control Register */

#define PHY_REG_PHYCR 0x19 /* PHY Control Register */

#define PHY_REG_10BTSCR 0x1A /* 10Base-T Status/Control Register */

#define PHY_REG_CDCTRL1 0x1B /* CD Test Control and BIST Extens. */

#define PHY_REG_EDCR 0x1D /* Energy Detect Control Register */

#define PHY_FULLD_100M 0x2100 /* Full Duplex 100Mbit */

#define PHY_HALFD_100M 0x2000 /* Half Duplex 100Mbit */

#define PHY_FULLD_10M 0x0100 /* Full Duplex 10Mbit */

#define PHY_HALFD_10M 0x0000 /* Half Duplex 10MBit */

#define PHY_AUTO_NEG 0x3000 /* Select Auto Negotiation */

#define DP83848C_DEF_ADR 0x0100 /* Default PHY device address */

#define DP83848C_ID 0x20005C90 /* PHY Identifier */

#endif