Lib for FTDI FT800 graphic controller "EVE" The API is changed from the FTDI original names. It use smaller names now. DL() will add something to the display list instead of Ft_App_WrCoCmd_Buffer ... The FTDI programmer Guide is also using this commands.

Dependents: FT800_RGB_demo FT800_RGB_demo2 FT800_demo_for_habr Temp_&_RH_at_TFT-demo ... more

Fork of FT800 by

The mbed is talking thru the SPI interface with the graphic engine. We have to set up a list of Commands and send them to the FT800 to get graphics.

Hardware

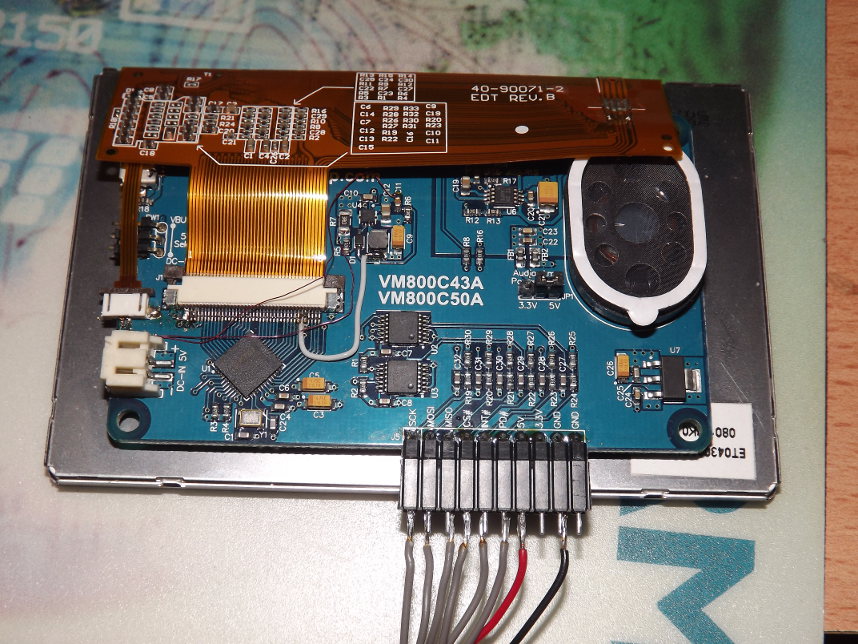

1. VM800C development modules from FTDI : http://www.ftdichip.com/Products/Modules/VM800C.html

The modules come with different size lcd. 3.5", 4.3" or 5" or without.

The picture shows a modified board, because my lcd had a different pinout. The mbed is connected to the pin header on the bottom.

The picture shows a modified board, because my lcd had a different pinout. The mbed is connected to the pin header on the bottom.

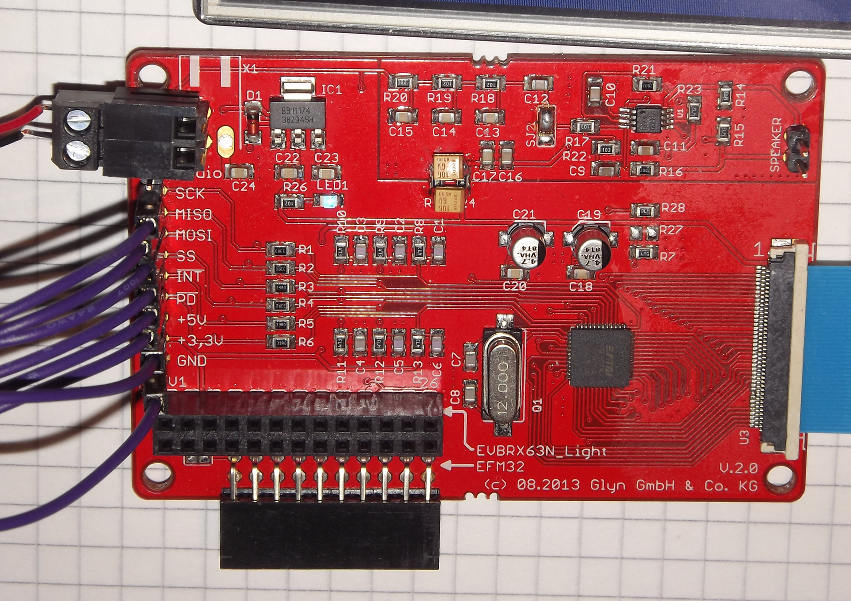

2. EVBEVE-FT800 board from GLYN: http://www.glyn.com/News-Events/Newsletter/Newsletter-2013/October-2013/A-quick-start-for-EVE-Requires-no-basic-knowledge-graphics-sound-and-touch-can-all-be-learned-in-minutes

The module has a 40 pin flex cable connector to connect a display out of the EDT series.

The mbed is connected via the pin header on the left. If you use this board with a EDT display you have to uncomment the #define Inv_Backlite in FT_LCD_Type.h, because the backlight dimming is inverted.

3. ConnectEVE board from MikroElektronika http://www.mikroe.com/add-on-boards/display/connecteve/#headers_10 The board has also a pin header to connect the mbed. - not tested, but it looks like the other boards.

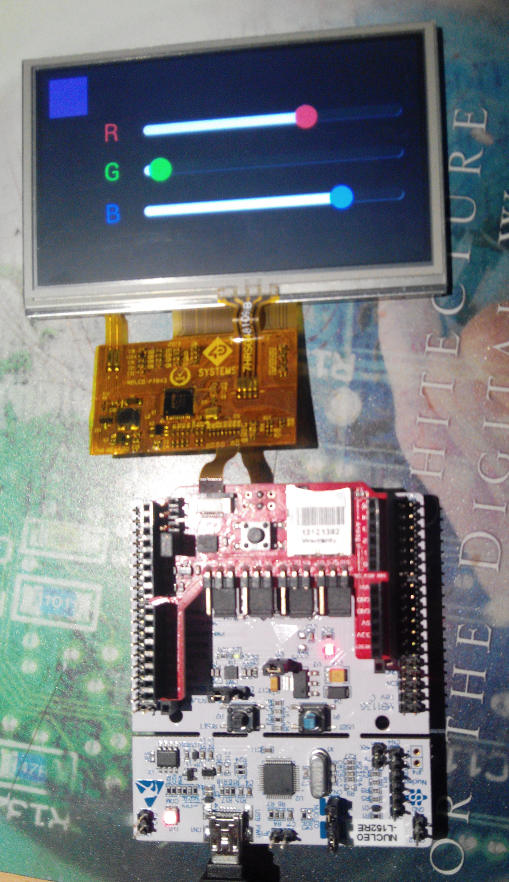

4. ADAM arduino shield http://www.4dsystems.com.au/product/4DLCD_FT843/ Component page : http://mbed.org/components/ADAM/

Works with the NUCLEO boards, but you have to patch three wires.

Connection

We need 5 signals to connect to the mbed. SCK, MOSI and MISO are connected to a SPI channel. SS is the chip select signal and PD work as powerdown. The additional INT signal is not used at the moment. It is possible to generate a interrupt signal, but at the moment you have to poll the status register of the FT800 to see if a command is finished.

Software

This lib is based on the demo code from FTDI. If you want to use it, you have to read the programming manual : http://www.ftdichip.com/Support/Documents/ProgramGuides/FT800%20Programmers%20Guide.pdf

See my demo : http://mbed.org/users/dreschpe/code/FT800_RGB_demo/

FT_Gpu_Hal.cpp@2:ab74a9a05970, 2014-01-04 (annotated)

- Committer:

- dreschpe

- Date:

- Sat Jan 04 13:56:38 2014 +0000

- Revision:

- 2:ab74a9a05970

- Parent:

- 1:bd671a31e765

- Child:

- 3:392d2c733c68

add doku

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| dreschpe | 2:ab74a9a05970 | 1 | /* mbed Library for FTDI FT800 Enbedded Video Engine "EVE" |

| dreschpe | 2:ab74a9a05970 | 2 | * based on Original Code Sample from FTDI |

| dreschpe | 2:ab74a9a05970 | 3 | * ported to mbed by Peter Drescher, DC2PD 2014 |

| dreschpe | 2:ab74a9a05970 | 4 | * Released under the MIT License: http://mbed.org/license/mit */ |

| dreschpe | 2:ab74a9a05970 | 5 | |

| dreschpe | 0:5e013296b353 | 6 | #include "FT_Platform.h" |

| dreschpe | 0:5e013296b353 | 7 | #include "mbed.h" |

| dreschpe | 0:5e013296b353 | 8 | #include "FT_LCD_Type.h" |

| dreschpe | 0:5e013296b353 | 9 | |

| dreschpe | 0:5e013296b353 | 10 | FT800::FT800(PinName mosi, |

| dreschpe | 0:5e013296b353 | 11 | PinName miso, |

| dreschpe | 0:5e013296b353 | 12 | PinName sck, |

| dreschpe | 0:5e013296b353 | 13 | PinName ss, |

| dreschpe | 0:5e013296b353 | 14 | PinName intr, |

| dreschpe | 0:5e013296b353 | 15 | PinName pd) |

| dreschpe | 0:5e013296b353 | 16 | :_spi(mosi, miso, sck), |

| dreschpe | 0:5e013296b353 | 17 | _ss(ss), |

| dreschpe | 0:5e013296b353 | 18 | _f800_isr(InterruptIn(intr)), |

| dreschpe | 0:5e013296b353 | 19 | _pd(pd) |

| dreschpe | 0:5e013296b353 | 20 | { |

| dreschpe | 0:5e013296b353 | 21 | _spi.format(8,0); // 8 bit spi mode 0 |

| dreschpe | 0:5e013296b353 | 22 | _spi.frequency(10000000); // start with 10 Mhz SPI clock |

| dreschpe | 0:5e013296b353 | 23 | _ss = 1; // cs high |

| dreschpe | 0:5e013296b353 | 24 | _pd = 1; // PD high |

| dreschpe | 0:5e013296b353 | 25 | Bootup(); |

| dreschpe | 0:5e013296b353 | 26 | } |

| dreschpe | 0:5e013296b353 | 27 | |

| dreschpe | 0:5e013296b353 | 28 | |

| dreschpe | 0:5e013296b353 | 29 | ft_bool_t FT800::Bootup(void){ |

| dreschpe | 0:5e013296b353 | 30 | Ft_Gpu_Hal_Open(); |

| dreschpe | 0:5e013296b353 | 31 | BootupConfig(); |

| dreschpe | 0:5e013296b353 | 32 | |

| dreschpe | 0:5e013296b353 | 33 | return(1); |

| dreschpe | 0:5e013296b353 | 34 | } |

| dreschpe | 0:5e013296b353 | 35 | |

| dreschpe | 0:5e013296b353 | 36 | |

| dreschpe | 0:5e013296b353 | 37 | ft_void_t FT800::BootupConfig(void){ |

| dreschpe | 0:5e013296b353 | 38 | ft_uint8_t chipid; |

| dreschpe | 0:5e013296b353 | 39 | /* Do a power cycle for safer side */ |

| dreschpe | 0:5e013296b353 | 40 | Ft_Gpu_Hal_Powercycle( FT_TRUE); |

| dreschpe | 0:5e013296b353 | 41 | |

| dreschpe | 0:5e013296b353 | 42 | /* Access address 0 to wake up the FT800 */ |

| dreschpe | 0:5e013296b353 | 43 | Ft_Gpu_HostCommand( FT_GPU_ACTIVE_M); |

| dreschpe | 0:5e013296b353 | 44 | Ft_Gpu_Hal_Sleep(20); |

| dreschpe | 0:5e013296b353 | 45 | |

| dreschpe | 0:5e013296b353 | 46 | /* Set the clk to external clock */ |

| dreschpe | 0:5e013296b353 | 47 | Ft_Gpu_HostCommand( FT_GPU_EXTERNAL_OSC); |

| dreschpe | 0:5e013296b353 | 48 | Ft_Gpu_Hal_Sleep(10); |

| dreschpe | 0:5e013296b353 | 49 | |

| dreschpe | 0:5e013296b353 | 50 | |

| dreschpe | 0:5e013296b353 | 51 | /* Switch PLL output to 48MHz */ |

| dreschpe | 0:5e013296b353 | 52 | Ft_Gpu_HostCommand( FT_GPU_PLL_48M); |

| dreschpe | 0:5e013296b353 | 53 | Ft_Gpu_Hal_Sleep(10); |

| dreschpe | 0:5e013296b353 | 54 | |

| dreschpe | 0:5e013296b353 | 55 | /* Do a core reset for safer side */ |

| dreschpe | 0:5e013296b353 | 56 | Ft_Gpu_HostCommand( FT_GPU_CORE_RESET); |

| dreschpe | 0:5e013296b353 | 57 | |

| dreschpe | 0:5e013296b353 | 58 | //Read Register ID to check if FT800 is ready. |

| dreschpe | 0:5e013296b353 | 59 | chipid = Ft_Gpu_Hal_Rd8( REG_ID); |

| dreschpe | 0:5e013296b353 | 60 | while(chipid != 0x7C) |

| dreschpe | 0:5e013296b353 | 61 | chipid = Ft_Gpu_Hal_Rd8( REG_ID); |

| dreschpe | 0:5e013296b353 | 62 | |

| dreschpe | 0:5e013296b353 | 63 | |

| dreschpe | 0:5e013296b353 | 64 | // Speed up |

| dreschpe | 2:ab74a9a05970 | 65 | _spi.frequency(16000000); // 20 Mhz SPI clock |

| dreschpe | 0:5e013296b353 | 66 | |

| dreschpe | 0:5e013296b353 | 67 | /* Configuration of LCD display */ |

| dreschpe | 0:5e013296b353 | 68 | FT_DispHCycle = my_DispHCycle; |

| dreschpe | 0:5e013296b353 | 69 | Ft_Gpu_Hal_Wr16( REG_HCYCLE, FT_DispHCycle); |

| dreschpe | 0:5e013296b353 | 70 | FT_DispHOffset = my_DispHOffset; |

| dreschpe | 0:5e013296b353 | 71 | Ft_Gpu_Hal_Wr16( REG_HOFFSET, FT_DispHOffset); |

| dreschpe | 0:5e013296b353 | 72 | FT_DispWidth = my_DispWidth; |

| dreschpe | 0:5e013296b353 | 73 | Ft_Gpu_Hal_Wr16( REG_HSIZE, FT_DispWidth); |

| dreschpe | 0:5e013296b353 | 74 | FT_DispHSync0 = my_DispHSync0; |

| dreschpe | 0:5e013296b353 | 75 | Ft_Gpu_Hal_Wr16( REG_HSYNC0, FT_DispHSync0); |

| dreschpe | 0:5e013296b353 | 76 | FT_DispHSync1 = my_DispHSync1; |

| dreschpe | 0:5e013296b353 | 77 | Ft_Gpu_Hal_Wr16( REG_HSYNC1, FT_DispHSync1); |

| dreschpe | 0:5e013296b353 | 78 | FT_DispVCycle = my_DispVCycle; |

| dreschpe | 0:5e013296b353 | 79 | Ft_Gpu_Hal_Wr16( REG_VCYCLE, FT_DispVCycle); |

| dreschpe | 0:5e013296b353 | 80 | FT_DispVOffset = my_DispVOffset; |

| dreschpe | 0:5e013296b353 | 81 | Ft_Gpu_Hal_Wr16( REG_VOFFSET, FT_DispVOffset); |

| dreschpe | 0:5e013296b353 | 82 | FT_DispHeight = my_DispHeight; |

| dreschpe | 0:5e013296b353 | 83 | Ft_Gpu_Hal_Wr16( REG_VSIZE, FT_DispHeight); |

| dreschpe | 0:5e013296b353 | 84 | FT_DispVSync0 = my_DispVSync0; |

| dreschpe | 0:5e013296b353 | 85 | Ft_Gpu_Hal_Wr16( REG_VSYNC0, FT_DispVSync0); |

| dreschpe | 0:5e013296b353 | 86 | FT_DispVSync1 = my_DispVSync1; |

| dreschpe | 0:5e013296b353 | 87 | Ft_Gpu_Hal_Wr16( REG_VSYNC1, FT_DispVSync1); |

| dreschpe | 0:5e013296b353 | 88 | FT_DispSwizzle = my_DispSwizzle; |

| dreschpe | 0:5e013296b353 | 89 | //Ft_Gpu_Hal_Wr8( REG_SWIZZLE, FT_DispSwizzle); |

| dreschpe | 0:5e013296b353 | 90 | FT_DispPCLKPol = my_DispPCLKPol; |

| dreschpe | 0:5e013296b353 | 91 | //Ft_Gpu_Hal_Wr8( REG_PCLK_POL, FT_DispPCLKPol); |

| dreschpe | 0:5e013296b353 | 92 | FT_DispPCLK = my_DispPCLK; |

| dreschpe | 0:5e013296b353 | 93 | //Ft_Gpu_Hal_Wr8( REG_PCLK,FT_DispPCLK);//after this display is visible on the LCD |

| dreschpe | 0:5e013296b353 | 94 | |

| dreschpe | 0:5e013296b353 | 95 | Ft_Gpu_Hal_Wr16( REG_PWM_HZ, 1000); |

| dreschpe | 0:5e013296b353 | 96 | |

| dreschpe | 0:5e013296b353 | 97 | #ifdef Inv_Backlite |

| dreschpe | 0:5e013296b353 | 98 | Ft_Gpu_Hal_Wr16( REG_PWM_DUTY, 0); |

| dreschpe | 0:5e013296b353 | 99 | #else |

| dreschpe | 0:5e013296b353 | 100 | Ft_Gpu_Hal_Wr16( REG_PWM_DUTY, 100); |

| dreschpe | 0:5e013296b353 | 101 | #endif |

| dreschpe | 0:5e013296b353 | 102 | |

| dreschpe | 1:bd671a31e765 | 103 | Ft_Gpu_Hal_Wr8( REG_GPIO_DIR,0x82); //| Ft_Gpu_Hal_Rd8( REG_GPIO_DIR)); |

| dreschpe | 0:5e013296b353 | 104 | Ft_Gpu_Hal_Wr8( REG_GPIO,0x080); //| Ft_Gpu_Hal_Rd8( REG_GPIO)); |

| dreschpe | 0:5e013296b353 | 105 | |

| dreschpe | 0:5e013296b353 | 106 | Ft_Gpu_Hal_Wr32( RAM_DL, CLEAR(1,1,1)); |

| dreschpe | 0:5e013296b353 | 107 | Ft_Gpu_Hal_Wr32( RAM_DL+4, DISPLAY()); |

| dreschpe | 0:5e013296b353 | 108 | Ft_Gpu_Hal_Wr32( REG_DLSWAP,1); |

| dreschpe | 0:5e013296b353 | 109 | |

| dreschpe | 0:5e013296b353 | 110 | Ft_Gpu_Hal_Wr16( REG_PCLK, FT_DispPCLK); |

| dreschpe | 0:5e013296b353 | 111 | |

| dreschpe | 0:5e013296b353 | 112 | /* Touch configuration - configure the resistance value to 1200 - this value is specific to customer requirement and derived by experiment */ |

| dreschpe | 0:5e013296b353 | 113 | Ft_Gpu_Hal_Wr16( REG_TOUCH_RZTHRESH,1200); |

| dreschpe | 0:5e013296b353 | 114 | |

| dreschpe | 0:5e013296b353 | 115 | } |

| dreschpe | 0:5e013296b353 | 116 | |

| dreschpe | 0:5e013296b353 | 117 | |

| dreschpe | 0:5e013296b353 | 118 | |

| dreschpe | 0:5e013296b353 | 119 | /* API to initialize the SPI interface */ |

| dreschpe | 0:5e013296b353 | 120 | ft_bool_t FT800::Ft_Gpu_Hal_Init() |

| dreschpe | 0:5e013296b353 | 121 | { |

| dreschpe | 0:5e013296b353 | 122 | // is done in constructor |

| dreschpe | 0:5e013296b353 | 123 | return 1; |

| dreschpe | 0:5e013296b353 | 124 | } |

| dreschpe | 0:5e013296b353 | 125 | |

| dreschpe | 0:5e013296b353 | 126 | |

| dreschpe | 0:5e013296b353 | 127 | ft_bool_t FT800::Ft_Gpu_Hal_Open() |

| dreschpe | 0:5e013296b353 | 128 | { |

| dreschpe | 0:5e013296b353 | 129 | ft_cmd_fifo_wp = ft_dl_buff_wp = 0; |

| dreschpe | 0:5e013296b353 | 130 | status = FT_GPU_HAL_OPENED; |

| dreschpe | 0:5e013296b353 | 131 | return 1; |

| dreschpe | 0:5e013296b353 | 132 | } |

| dreschpe | 0:5e013296b353 | 133 | |

| dreschpe | 0:5e013296b353 | 134 | ft_void_t FT800::Ft_Gpu_Hal_Close( ) |

| dreschpe | 0:5e013296b353 | 135 | { |

| dreschpe | 0:5e013296b353 | 136 | status = FT_GPU_HAL_CLOSED; |

| dreschpe | 0:5e013296b353 | 137 | } |

| dreschpe | 0:5e013296b353 | 138 | |

| dreschpe | 0:5e013296b353 | 139 | ft_void_t FT800::Ft_Gpu_Hal_DeInit() |

| dreschpe | 0:5e013296b353 | 140 | { |

| dreschpe | 0:5e013296b353 | 141 | |

| dreschpe | 0:5e013296b353 | 142 | } |

| dreschpe | 0:5e013296b353 | 143 | |

| dreschpe | 0:5e013296b353 | 144 | /*The APIs for reading/writing transfer continuously only with small buffer system*/ |

| dreschpe | 0:5e013296b353 | 145 | ft_void_t FT800::Ft_Gpu_Hal_StartTransfer( FT_GPU_TRANSFERDIR_T rw,ft_uint32_t addr) |

| dreschpe | 0:5e013296b353 | 146 | { |

| dreschpe | 0:5e013296b353 | 147 | if (FT_GPU_READ == rw){ |

| dreschpe | 0:5e013296b353 | 148 | _ss = 0; // cs low |

| dreschpe | 0:5e013296b353 | 149 | _spi.write(addr >> 16); |

| dreschpe | 0:5e013296b353 | 150 | _spi.write(addr >> 8); |

| dreschpe | 0:5e013296b353 | 151 | _spi.write(addr & 0xff); |

| dreschpe | 0:5e013296b353 | 152 | _spi.write(0); //Dummy Read Byte |

| dreschpe | 0:5e013296b353 | 153 | status = FT_GPU_HAL_READING; |

| dreschpe | 0:5e013296b353 | 154 | }else{ |

| dreschpe | 0:5e013296b353 | 155 | _ss = 0; // cs low |

| dreschpe | 0:5e013296b353 | 156 | _spi.write(0x80 | (addr >> 16)); |

| dreschpe | 0:5e013296b353 | 157 | _spi.write(addr >> 8); |

| dreschpe | 0:5e013296b353 | 158 | _spi.write(addr & 0xff); |

| dreschpe | 0:5e013296b353 | 159 | status = FT_GPU_HAL_WRITING; |

| dreschpe | 0:5e013296b353 | 160 | } |

| dreschpe | 0:5e013296b353 | 161 | } |

| dreschpe | 0:5e013296b353 | 162 | |

| dreschpe | 0:5e013296b353 | 163 | |

| dreschpe | 0:5e013296b353 | 164 | /*The APIs for writing transfer continuously only*/ |

| dreschpe | 0:5e013296b353 | 165 | ft_void_t FT800::Ft_Gpu_Hal_StartCmdTransfer( FT_GPU_TRANSFERDIR_T rw, ft_uint16_t count) |

| dreschpe | 0:5e013296b353 | 166 | { |

| dreschpe | 0:5e013296b353 | 167 | Ft_Gpu_Hal_StartTransfer( rw, ft_cmd_fifo_wp + RAM_CMD); |

| dreschpe | 0:5e013296b353 | 168 | } |

| dreschpe | 0:5e013296b353 | 169 | |

| dreschpe | 0:5e013296b353 | 170 | ft_uint8_t FT800::Ft_Gpu_Hal_TransferString( const ft_char8_t *string) |

| dreschpe | 0:5e013296b353 | 171 | { |

| dreschpe | 0:5e013296b353 | 172 | ft_uint16_t length = strlen(string); |

| dreschpe | 0:5e013296b353 | 173 | while(length --){ |

| dreschpe | 0:5e013296b353 | 174 | Ft_Gpu_Hal_Transfer8( *string); |

| dreschpe | 0:5e013296b353 | 175 | string ++; |

| dreschpe | 0:5e013296b353 | 176 | } |

| dreschpe | 0:5e013296b353 | 177 | //Append one null as ending flag |

| dreschpe | 0:5e013296b353 | 178 | Ft_Gpu_Hal_Transfer8( 0); |

| dreschpe | 0:5e013296b353 | 179 | } |

| dreschpe | 0:5e013296b353 | 180 | |

| dreschpe | 0:5e013296b353 | 181 | |

| dreschpe | 0:5e013296b353 | 182 | ft_uint8_t FT800::Ft_Gpu_Hal_Transfer8( ft_uint8_t value) |

| dreschpe | 0:5e013296b353 | 183 | { |

| dreschpe | 0:5e013296b353 | 184 | return _spi.write(value); |

| dreschpe | 0:5e013296b353 | 185 | } |

| dreschpe | 0:5e013296b353 | 186 | |

| dreschpe | 0:5e013296b353 | 187 | |

| dreschpe | 0:5e013296b353 | 188 | ft_uint16_t FT800::Ft_Gpu_Hal_Transfer16( ft_uint16_t value) |

| dreschpe | 0:5e013296b353 | 189 | { |

| dreschpe | 0:5e013296b353 | 190 | ft_uint16_t retVal = 0; |

| dreschpe | 0:5e013296b353 | 191 | |

| dreschpe | 0:5e013296b353 | 192 | if (status == FT_GPU_HAL_WRITING){ |

| dreschpe | 0:5e013296b353 | 193 | Ft_Gpu_Hal_Transfer8( value & 0xFF);//LSB first |

| dreschpe | 0:5e013296b353 | 194 | Ft_Gpu_Hal_Transfer8( (value >> 8) & 0xFF); |

| dreschpe | 0:5e013296b353 | 195 | }else{ |

| dreschpe | 0:5e013296b353 | 196 | retVal = Ft_Gpu_Hal_Transfer8( 0); |

| dreschpe | 0:5e013296b353 | 197 | retVal |= (ft_uint16_t)Ft_Gpu_Hal_Transfer8( 0) << 8; |

| dreschpe | 0:5e013296b353 | 198 | } |

| dreschpe | 0:5e013296b353 | 199 | |

| dreschpe | 0:5e013296b353 | 200 | return retVal; |

| dreschpe | 0:5e013296b353 | 201 | } |

| dreschpe | 0:5e013296b353 | 202 | |

| dreschpe | 0:5e013296b353 | 203 | ft_uint32_t FT800::Ft_Gpu_Hal_Transfer32( ft_uint32_t value) |

| dreschpe | 0:5e013296b353 | 204 | { |

| dreschpe | 0:5e013296b353 | 205 | ft_uint32_t retVal = 0; |

| dreschpe | 0:5e013296b353 | 206 | if (status == FT_GPU_HAL_WRITING){ |

| dreschpe | 0:5e013296b353 | 207 | Ft_Gpu_Hal_Transfer16( value & 0xFFFF);//LSB first |

| dreschpe | 0:5e013296b353 | 208 | Ft_Gpu_Hal_Transfer16( (value >> 16) & 0xFFFF); |

| dreschpe | 0:5e013296b353 | 209 | }else{ |

| dreschpe | 0:5e013296b353 | 210 | retVal = Ft_Gpu_Hal_Transfer16( 0); |

| dreschpe | 0:5e013296b353 | 211 | retVal |= (ft_uint32_t)Ft_Gpu_Hal_Transfer16( 0) << 16; |

| dreschpe | 0:5e013296b353 | 212 | } |

| dreschpe | 0:5e013296b353 | 213 | return retVal; |

| dreschpe | 0:5e013296b353 | 214 | } |

| dreschpe | 0:5e013296b353 | 215 | |

| dreschpe | 0:5e013296b353 | 216 | ft_void_t FT800::Ft_Gpu_Hal_EndTransfer( ) |

| dreschpe | 0:5e013296b353 | 217 | { |

| dreschpe | 0:5e013296b353 | 218 | _ss = 1; |

| dreschpe | 0:5e013296b353 | 219 | status = FT_GPU_HAL_OPENED; |

| dreschpe | 0:5e013296b353 | 220 | } |

| dreschpe | 0:5e013296b353 | 221 | |

| dreschpe | 0:5e013296b353 | 222 | |

| dreschpe | 0:5e013296b353 | 223 | ft_uint8_t FT800::Ft_Gpu_Hal_Rd8( ft_uint32_t addr) |

| dreschpe | 0:5e013296b353 | 224 | { |

| dreschpe | 0:5e013296b353 | 225 | ft_uint8_t value; |

| dreschpe | 0:5e013296b353 | 226 | Ft_Gpu_Hal_StartTransfer( FT_GPU_READ,addr); |

| dreschpe | 0:5e013296b353 | 227 | value = Ft_Gpu_Hal_Transfer8( 0); |

| dreschpe | 0:5e013296b353 | 228 | Ft_Gpu_Hal_EndTransfer( ); |

| dreschpe | 0:5e013296b353 | 229 | return value; |

| dreschpe | 0:5e013296b353 | 230 | } |

| dreschpe | 0:5e013296b353 | 231 | ft_uint16_t FT800::Ft_Gpu_Hal_Rd16( ft_uint32_t addr) |

| dreschpe | 0:5e013296b353 | 232 | { |

| dreschpe | 0:5e013296b353 | 233 | ft_uint16_t value; |

| dreschpe | 0:5e013296b353 | 234 | Ft_Gpu_Hal_StartTransfer( FT_GPU_READ,addr); |

| dreschpe | 0:5e013296b353 | 235 | value = Ft_Gpu_Hal_Transfer16( 0); |

| dreschpe | 0:5e013296b353 | 236 | Ft_Gpu_Hal_EndTransfer( ); |

| dreschpe | 0:5e013296b353 | 237 | return value; |

| dreschpe | 0:5e013296b353 | 238 | } |

| dreschpe | 0:5e013296b353 | 239 | ft_uint32_t FT800::Ft_Gpu_Hal_Rd32( ft_uint32_t addr) |

| dreschpe | 0:5e013296b353 | 240 | { |

| dreschpe | 0:5e013296b353 | 241 | ft_uint32_t value; |

| dreschpe | 0:5e013296b353 | 242 | Ft_Gpu_Hal_StartTransfer( FT_GPU_READ,addr); |

| dreschpe | 0:5e013296b353 | 243 | value = Ft_Gpu_Hal_Transfer32( 0); |

| dreschpe | 0:5e013296b353 | 244 | Ft_Gpu_Hal_EndTransfer( ); |

| dreschpe | 0:5e013296b353 | 245 | return value; |

| dreschpe | 0:5e013296b353 | 246 | } |

| dreschpe | 0:5e013296b353 | 247 | |

| dreschpe | 0:5e013296b353 | 248 | ft_void_t FT800::Ft_Gpu_Hal_Wr8( ft_uint32_t addr, ft_uint8_t v) |

| dreschpe | 0:5e013296b353 | 249 | { |

| dreschpe | 0:5e013296b353 | 250 | Ft_Gpu_Hal_StartTransfer( FT_GPU_WRITE,addr); |

| dreschpe | 0:5e013296b353 | 251 | Ft_Gpu_Hal_Transfer8( v); |

| dreschpe | 0:5e013296b353 | 252 | Ft_Gpu_Hal_EndTransfer( ); |

| dreschpe | 0:5e013296b353 | 253 | } |

| dreschpe | 0:5e013296b353 | 254 | ft_void_t FT800::Ft_Gpu_Hal_Wr16( ft_uint32_t addr, ft_uint16_t v) |

| dreschpe | 0:5e013296b353 | 255 | { |

| dreschpe | 0:5e013296b353 | 256 | Ft_Gpu_Hal_StartTransfer( FT_GPU_WRITE,addr); |

| dreschpe | 0:5e013296b353 | 257 | Ft_Gpu_Hal_Transfer16( v); |

| dreschpe | 0:5e013296b353 | 258 | Ft_Gpu_Hal_EndTransfer( ); |

| dreschpe | 0:5e013296b353 | 259 | } |

| dreschpe | 0:5e013296b353 | 260 | ft_void_t FT800::Ft_Gpu_Hal_Wr32( ft_uint32_t addr, ft_uint32_t v) |

| dreschpe | 0:5e013296b353 | 261 | { |

| dreschpe | 0:5e013296b353 | 262 | Ft_Gpu_Hal_StartTransfer( FT_GPU_WRITE,addr); |

| dreschpe | 0:5e013296b353 | 263 | Ft_Gpu_Hal_Transfer32( v); |

| dreschpe | 0:5e013296b353 | 264 | Ft_Gpu_Hal_EndTransfer( ); |

| dreschpe | 0:5e013296b353 | 265 | } |

| dreschpe | 0:5e013296b353 | 266 | |

| dreschpe | 0:5e013296b353 | 267 | ft_void_t FT800::Ft_Gpu_HostCommand( ft_uint8_t cmd) |

| dreschpe | 0:5e013296b353 | 268 | { |

| dreschpe | 0:5e013296b353 | 269 | _ss = 0; |

| dreschpe | 0:5e013296b353 | 270 | _spi.write(cmd); |

| dreschpe | 0:5e013296b353 | 271 | _spi.write(0); |

| dreschpe | 0:5e013296b353 | 272 | _spi.write(0); |

| dreschpe | 0:5e013296b353 | 273 | _ss = 1; |

| dreschpe | 0:5e013296b353 | 274 | } |

| dreschpe | 0:5e013296b353 | 275 | |

| dreschpe | 0:5e013296b353 | 276 | ft_void_t FT800::Ft_Gpu_ClockSelect( FT_GPU_PLL_SOURCE_T pllsource) |

| dreschpe | 0:5e013296b353 | 277 | { |

| dreschpe | 0:5e013296b353 | 278 | Ft_Gpu_HostCommand( pllsource); |

| dreschpe | 0:5e013296b353 | 279 | } |

| dreschpe | 0:5e013296b353 | 280 | |

| dreschpe | 0:5e013296b353 | 281 | ft_void_t FT800::Ft_Gpu_PLL_FreqSelect( FT_GPU_PLL_FREQ_T freq) |

| dreschpe | 0:5e013296b353 | 282 | { |

| dreschpe | 0:5e013296b353 | 283 | Ft_Gpu_HostCommand( freq); |

| dreschpe | 0:5e013296b353 | 284 | } |

| dreschpe | 0:5e013296b353 | 285 | |

| dreschpe | 0:5e013296b353 | 286 | ft_void_t FT800::Ft_Gpu_PowerModeSwitch( FT_GPU_POWER_MODE_T pwrmode) |

| dreschpe | 0:5e013296b353 | 287 | { |

| dreschpe | 0:5e013296b353 | 288 | Ft_Gpu_HostCommand( pwrmode); |

| dreschpe | 0:5e013296b353 | 289 | } |

| dreschpe | 0:5e013296b353 | 290 | |

| dreschpe | 0:5e013296b353 | 291 | ft_void_t FT800::Ft_Gpu_CoreReset( ) |

| dreschpe | 0:5e013296b353 | 292 | { |

| dreschpe | 0:5e013296b353 | 293 | Ft_Gpu_HostCommand( 0x68); |

| dreschpe | 0:5e013296b353 | 294 | } |

| dreschpe | 0:5e013296b353 | 295 | |

| dreschpe | 0:5e013296b353 | 296 | |

| dreschpe | 0:5e013296b353 | 297 | ft_void_t FT800::Ft_Gpu_Hal_Updatecmdfifo( ft_uint16_t count) |

| dreschpe | 0:5e013296b353 | 298 | { |

| dreschpe | 0:5e013296b353 | 299 | ft_cmd_fifo_wp = ( ft_cmd_fifo_wp + count) & 4095; |

| dreschpe | 0:5e013296b353 | 300 | //4 byte alignment |

| dreschpe | 0:5e013296b353 | 301 | ft_cmd_fifo_wp = ( ft_cmd_fifo_wp + 3) & 0xffc; |

| dreschpe | 0:5e013296b353 | 302 | Ft_Gpu_Hal_Wr16( REG_CMD_WRITE, ft_cmd_fifo_wp); |

| dreschpe | 0:5e013296b353 | 303 | } |

| dreschpe | 0:5e013296b353 | 304 | |

| dreschpe | 0:5e013296b353 | 305 | |

| dreschpe | 0:5e013296b353 | 306 | ft_uint16_t FT800::Ft_Gpu_Cmdfifo_Freespace( ) |

| dreschpe | 0:5e013296b353 | 307 | { |

| dreschpe | 0:5e013296b353 | 308 | ft_uint16_t fullness,retval; |

| dreschpe | 0:5e013296b353 | 309 | |

| dreschpe | 0:5e013296b353 | 310 | fullness = ( ft_cmd_fifo_wp - Ft_Gpu_Hal_Rd16( REG_CMD_READ)) & 4095; |

| dreschpe | 0:5e013296b353 | 311 | retval = (FT_CMD_FIFO_SIZE - 4) - fullness; |

| dreschpe | 0:5e013296b353 | 312 | return (retval); |

| dreschpe | 0:5e013296b353 | 313 | } |

| dreschpe | 0:5e013296b353 | 314 | |

| dreschpe | 0:5e013296b353 | 315 | ft_void_t FT800::Ft_Gpu_Hal_WrCmdBuf( ft_uint8_t *buffer,ft_uint16_t count) |

| dreschpe | 0:5e013296b353 | 316 | { |

| dreschpe | 0:5e013296b353 | 317 | ft_uint32_t length =0, SizeTransfered = 0; |

| dreschpe | 0:5e013296b353 | 318 | |

| dreschpe | 0:5e013296b353 | 319 | #define MAX_CMD_FIFO_TRANSFER Ft_Gpu_Cmdfifo_Freespace( ) |

| dreschpe | 0:5e013296b353 | 320 | do { |

| dreschpe | 0:5e013296b353 | 321 | length = count; |

| dreschpe | 0:5e013296b353 | 322 | if (length > MAX_CMD_FIFO_TRANSFER){ |

| dreschpe | 0:5e013296b353 | 323 | length = MAX_CMD_FIFO_TRANSFER; |

| dreschpe | 0:5e013296b353 | 324 | } |

| dreschpe | 0:5e013296b353 | 325 | Ft_Gpu_Hal_CheckCmdBuffer( length); |

| dreschpe | 0:5e013296b353 | 326 | |

| dreschpe | 0:5e013296b353 | 327 | Ft_Gpu_Hal_StartCmdTransfer( FT_GPU_WRITE,length); |

| dreschpe | 0:5e013296b353 | 328 | |

| dreschpe | 0:5e013296b353 | 329 | SizeTransfered = 0; |

| dreschpe | 0:5e013296b353 | 330 | while (length--) { |

| dreschpe | 0:5e013296b353 | 331 | Ft_Gpu_Hal_Transfer8( *buffer); |

| dreschpe | 0:5e013296b353 | 332 | buffer++; |

| dreschpe | 0:5e013296b353 | 333 | SizeTransfered ++; |

| dreschpe | 0:5e013296b353 | 334 | } |

| dreschpe | 0:5e013296b353 | 335 | length = SizeTransfered; |

| dreschpe | 0:5e013296b353 | 336 | |

| dreschpe | 0:5e013296b353 | 337 | Ft_Gpu_Hal_EndTransfer( ); |

| dreschpe | 0:5e013296b353 | 338 | Ft_Gpu_Hal_Updatecmdfifo( length); |

| dreschpe | 0:5e013296b353 | 339 | |

| dreschpe | 0:5e013296b353 | 340 | Ft_Gpu_Hal_WaitCmdfifo_empty( ); |

| dreschpe | 0:5e013296b353 | 341 | |

| dreschpe | 0:5e013296b353 | 342 | count -= length; |

| dreschpe | 0:5e013296b353 | 343 | }while (count > 0); |

| dreschpe | 0:5e013296b353 | 344 | } |

| dreschpe | 0:5e013296b353 | 345 | |

| dreschpe | 0:5e013296b353 | 346 | |

| dreschpe | 0:5e013296b353 | 347 | ft_void_t FT800::Ft_Gpu_Hal_WrCmdBufFromFlash( FT_PROGMEM ft_prog_uchar8_t *buffer,ft_uint16_t count) |

| dreschpe | 0:5e013296b353 | 348 | { |

| dreschpe | 0:5e013296b353 | 349 | ft_uint32_t length =0, SizeTransfered = 0; |

| dreschpe | 0:5e013296b353 | 350 | |

| dreschpe | 0:5e013296b353 | 351 | #define MAX_CMD_FIFO_TRANSFER Ft_Gpu_Cmdfifo_Freespace( ) |

| dreschpe | 0:5e013296b353 | 352 | do { |

| dreschpe | 0:5e013296b353 | 353 | length = count; |

| dreschpe | 0:5e013296b353 | 354 | if (length > MAX_CMD_FIFO_TRANSFER){ |

| dreschpe | 0:5e013296b353 | 355 | length = MAX_CMD_FIFO_TRANSFER; |

| dreschpe | 0:5e013296b353 | 356 | } |

| dreschpe | 0:5e013296b353 | 357 | Ft_Gpu_Hal_CheckCmdBuffer( length); |

| dreschpe | 0:5e013296b353 | 358 | |

| dreschpe | 0:5e013296b353 | 359 | Ft_Gpu_Hal_StartCmdTransfer( FT_GPU_WRITE,length); |

| dreschpe | 0:5e013296b353 | 360 | |

| dreschpe | 0:5e013296b353 | 361 | |

| dreschpe | 0:5e013296b353 | 362 | SizeTransfered = 0; |

| dreschpe | 0:5e013296b353 | 363 | while (length--) { |

| dreschpe | 0:5e013296b353 | 364 | Ft_Gpu_Hal_Transfer8( ft_pgm_read_byte_near(buffer)); |

| dreschpe | 0:5e013296b353 | 365 | buffer++; |

| dreschpe | 0:5e013296b353 | 366 | SizeTransfered ++; |

| dreschpe | 0:5e013296b353 | 367 | } |

| dreschpe | 0:5e013296b353 | 368 | length = SizeTransfered; |

| dreschpe | 0:5e013296b353 | 369 | |

| dreschpe | 0:5e013296b353 | 370 | Ft_Gpu_Hal_EndTransfer( ); |

| dreschpe | 0:5e013296b353 | 371 | Ft_Gpu_Hal_Updatecmdfifo( length); |

| dreschpe | 0:5e013296b353 | 372 | |

| dreschpe | 0:5e013296b353 | 373 | Ft_Gpu_Hal_WaitCmdfifo_empty( ); |

| dreschpe | 0:5e013296b353 | 374 | |

| dreschpe | 0:5e013296b353 | 375 | count -= length; |

| dreschpe | 0:5e013296b353 | 376 | }while (count > 0); |

| dreschpe | 0:5e013296b353 | 377 | } |

| dreschpe | 0:5e013296b353 | 378 | |

| dreschpe | 0:5e013296b353 | 379 | |

| dreschpe | 0:5e013296b353 | 380 | ft_void_t FT800::Ft_Gpu_Hal_CheckCmdBuffer( ft_uint16_t count) |

| dreschpe | 0:5e013296b353 | 381 | { |

| dreschpe | 0:5e013296b353 | 382 | ft_uint16_t getfreespace; |

| dreschpe | 0:5e013296b353 | 383 | do{ |

| dreschpe | 0:5e013296b353 | 384 | getfreespace = Ft_Gpu_Cmdfifo_Freespace( ); |

| dreschpe | 0:5e013296b353 | 385 | }while(getfreespace < count); |

| dreschpe | 0:5e013296b353 | 386 | } |

| dreschpe | 0:5e013296b353 | 387 | |

| dreschpe | 0:5e013296b353 | 388 | ft_void_t FT800::Ft_Gpu_Hal_WaitCmdfifo_empty( ) |

| dreschpe | 0:5e013296b353 | 389 | { |

| dreschpe | 0:5e013296b353 | 390 | while(Ft_Gpu_Hal_Rd16( REG_CMD_READ) != Ft_Gpu_Hal_Rd16( REG_CMD_WRITE)); |

| dreschpe | 0:5e013296b353 | 391 | |

| dreschpe | 0:5e013296b353 | 392 | ft_cmd_fifo_wp = Ft_Gpu_Hal_Rd16( REG_CMD_WRITE); |

| dreschpe | 0:5e013296b353 | 393 | } |

| dreschpe | 0:5e013296b353 | 394 | |

| dreschpe | 0:5e013296b353 | 395 | ft_void_t FT800::Ft_Gpu_Hal_WaitLogo_Finish( ) |

| dreschpe | 0:5e013296b353 | 396 | { |

| dreschpe | 0:5e013296b353 | 397 | ft_int16_t cmdrdptr,cmdwrptr; |

| dreschpe | 0:5e013296b353 | 398 | |

| dreschpe | 0:5e013296b353 | 399 | do{ |

| dreschpe | 0:5e013296b353 | 400 | cmdrdptr = Ft_Gpu_Hal_Rd16( REG_CMD_READ); |

| dreschpe | 0:5e013296b353 | 401 | cmdwrptr = Ft_Gpu_Hal_Rd16( REG_CMD_WRITE); |

| dreschpe | 0:5e013296b353 | 402 | }while ((cmdwrptr != cmdrdptr) || (cmdrdptr != 0)); |

| dreschpe | 0:5e013296b353 | 403 | ft_cmd_fifo_wp = 0; |

| dreschpe | 0:5e013296b353 | 404 | } |

| dreschpe | 0:5e013296b353 | 405 | |

| dreschpe | 0:5e013296b353 | 406 | |

| dreschpe | 0:5e013296b353 | 407 | ft_void_t FT800::Ft_Gpu_Hal_ResetCmdFifo( ) |

| dreschpe | 0:5e013296b353 | 408 | { |

| dreschpe | 0:5e013296b353 | 409 | ft_cmd_fifo_wp = 0; |

| dreschpe | 0:5e013296b353 | 410 | } |

| dreschpe | 0:5e013296b353 | 411 | |

| dreschpe | 0:5e013296b353 | 412 | |

| dreschpe | 0:5e013296b353 | 413 | ft_void_t FT800::Ft_Gpu_Hal_WrCmd32( ft_uint32_t cmd) |

| dreschpe | 0:5e013296b353 | 414 | { |

| dreschpe | 0:5e013296b353 | 415 | Ft_Gpu_Hal_CheckCmdBuffer( sizeof(cmd)); |

| dreschpe | 0:5e013296b353 | 416 | |

| dreschpe | 0:5e013296b353 | 417 | Ft_Gpu_Hal_Wr32( RAM_CMD + ft_cmd_fifo_wp,cmd); |

| dreschpe | 0:5e013296b353 | 418 | |

| dreschpe | 0:5e013296b353 | 419 | Ft_Gpu_Hal_Updatecmdfifo( sizeof(cmd)); |

| dreschpe | 0:5e013296b353 | 420 | } |

| dreschpe | 0:5e013296b353 | 421 | |

| dreschpe | 0:5e013296b353 | 422 | |

| dreschpe | 0:5e013296b353 | 423 | ft_void_t FT800::Ft_Gpu_Hal_ResetDLBuffer( ) |

| dreschpe | 0:5e013296b353 | 424 | { |

| dreschpe | 0:5e013296b353 | 425 | ft_dl_buff_wp = 0; |

| dreschpe | 0:5e013296b353 | 426 | } |

| dreschpe | 0:5e013296b353 | 427 | |

| dreschpe | 0:5e013296b353 | 428 | /* Toggle PD_N pin of FT800 board for a power cycle*/ |

| dreschpe | 0:5e013296b353 | 429 | ft_void_t FT800::Ft_Gpu_Hal_Powercycle( ft_bool_t up) |

| dreschpe | 0:5e013296b353 | 430 | { |

| dreschpe | 0:5e013296b353 | 431 | if (up) |

| dreschpe | 0:5e013296b353 | 432 | { |

| dreschpe | 0:5e013296b353 | 433 | //Toggle PD_N from low to high for power up switch |

| dreschpe | 0:5e013296b353 | 434 | _pd = 0; |

| dreschpe | 0:5e013296b353 | 435 | Ft_Gpu_Hal_Sleep(20); |

| dreschpe | 0:5e013296b353 | 436 | |

| dreschpe | 0:5e013296b353 | 437 | _pd = 1; |

| dreschpe | 0:5e013296b353 | 438 | Ft_Gpu_Hal_Sleep(20); |

| dreschpe | 0:5e013296b353 | 439 | }else |

| dreschpe | 0:5e013296b353 | 440 | { |

| dreschpe | 0:5e013296b353 | 441 | //Toggle PD_N from high to low for power down switch |

| dreschpe | 0:5e013296b353 | 442 | _pd = 1; |

| dreschpe | 0:5e013296b353 | 443 | Ft_Gpu_Hal_Sleep(20); |

| dreschpe | 0:5e013296b353 | 444 | |

| dreschpe | 0:5e013296b353 | 445 | _pd = 0; |

| dreschpe | 0:5e013296b353 | 446 | Ft_Gpu_Hal_Sleep(20); |

| dreschpe | 0:5e013296b353 | 447 | } |

| dreschpe | 0:5e013296b353 | 448 | } |

| dreschpe | 0:5e013296b353 | 449 | |

| dreschpe | 0:5e013296b353 | 450 | ft_void_t FT800::Ft_Gpu_Hal_WrMemFromFlash( ft_uint32_t addr,const ft_prog_uchar8_t *buffer, ft_uint32_t length) |

| dreschpe | 0:5e013296b353 | 451 | { |

| dreschpe | 0:5e013296b353 | 452 | ft_uint32_t SizeTransfered = 0; |

| dreschpe | 0:5e013296b353 | 453 | |

| dreschpe | 0:5e013296b353 | 454 | Ft_Gpu_Hal_StartTransfer( FT_GPU_WRITE,addr); |

| dreschpe | 0:5e013296b353 | 455 | |

| dreschpe | 0:5e013296b353 | 456 | while (length--) { |

| dreschpe | 0:5e013296b353 | 457 | Ft_Gpu_Hal_Transfer8( ft_pgm_read_byte_near(buffer)); |

| dreschpe | 0:5e013296b353 | 458 | buffer++; |

| dreschpe | 0:5e013296b353 | 459 | } |

| dreschpe | 0:5e013296b353 | 460 | |

| dreschpe | 0:5e013296b353 | 461 | Ft_Gpu_Hal_EndTransfer( ); |

| dreschpe | 0:5e013296b353 | 462 | } |

| dreschpe | 0:5e013296b353 | 463 | |

| dreschpe | 0:5e013296b353 | 464 | ft_void_t FT800::Ft_Gpu_Hal_WrMem( ft_uint32_t addr,const ft_uint8_t *buffer, ft_uint32_t length) |

| dreschpe | 0:5e013296b353 | 465 | { |

| dreschpe | 0:5e013296b353 | 466 | ft_uint32_t SizeTransfered = 0; |

| dreschpe | 0:5e013296b353 | 467 | |

| dreschpe | 0:5e013296b353 | 468 | Ft_Gpu_Hal_StartTransfer( FT_GPU_WRITE,addr); |

| dreschpe | 0:5e013296b353 | 469 | |

| dreschpe | 0:5e013296b353 | 470 | while (length--) { |

| dreschpe | 0:5e013296b353 | 471 | Ft_Gpu_Hal_Transfer8( *buffer); |

| dreschpe | 0:5e013296b353 | 472 | buffer++; |

| dreschpe | 0:5e013296b353 | 473 | } |

| dreschpe | 0:5e013296b353 | 474 | |

| dreschpe | 0:5e013296b353 | 475 | Ft_Gpu_Hal_EndTransfer( ); |

| dreschpe | 0:5e013296b353 | 476 | } |

| dreschpe | 0:5e013296b353 | 477 | |

| dreschpe | 0:5e013296b353 | 478 | |

| dreschpe | 0:5e013296b353 | 479 | ft_void_t FT800::Ft_Gpu_Hal_RdMem( ft_uint32_t addr, ft_uint8_t *buffer, ft_uint32_t length) |

| dreschpe | 0:5e013296b353 | 480 | { |

| dreschpe | 0:5e013296b353 | 481 | ft_uint32_t SizeTransfered = 0; |

| dreschpe | 0:5e013296b353 | 482 | |

| dreschpe | 0:5e013296b353 | 483 | Ft_Gpu_Hal_StartTransfer( FT_GPU_READ,addr); |

| dreschpe | 0:5e013296b353 | 484 | |

| dreschpe | 0:5e013296b353 | 485 | while (length--) { |

| dreschpe | 0:5e013296b353 | 486 | *buffer = Ft_Gpu_Hal_Transfer8( 0); |

| dreschpe | 0:5e013296b353 | 487 | buffer++; |

| dreschpe | 0:5e013296b353 | 488 | } |

| dreschpe | 0:5e013296b353 | 489 | |

| dreschpe | 0:5e013296b353 | 490 | Ft_Gpu_Hal_EndTransfer( ); |

| dreschpe | 0:5e013296b353 | 491 | } |

| dreschpe | 0:5e013296b353 | 492 | |

| dreschpe | 0:5e013296b353 | 493 | ft_int32_t FT800::Ft_Gpu_Hal_Dec2Ascii(ft_char8_t *pSrc,ft_int32_t value) |

| dreschpe | 0:5e013296b353 | 494 | { |

| dreschpe | 0:5e013296b353 | 495 | ft_int16_t Length; |

| dreschpe | 0:5e013296b353 | 496 | ft_char8_t *pdst,charval; |

| dreschpe | 0:5e013296b353 | 497 | ft_int32_t CurrVal = value,tmpval,i; |

| dreschpe | 0:5e013296b353 | 498 | ft_char8_t tmparray[16],idx = 0; |

| dreschpe | 0:5e013296b353 | 499 | |

| dreschpe | 0:5e013296b353 | 500 | Length = strlen(pSrc); |

| dreschpe | 0:5e013296b353 | 501 | pdst = pSrc + Length; |

| dreschpe | 0:5e013296b353 | 502 | |

| dreschpe | 0:5e013296b353 | 503 | if(0 == value) |

| dreschpe | 0:5e013296b353 | 504 | { |

| dreschpe | 0:5e013296b353 | 505 | *pdst++ = '0'; |

| dreschpe | 0:5e013296b353 | 506 | *pdst++ = '\0'; |

| dreschpe | 0:5e013296b353 | 507 | return 0; |

| dreschpe | 0:5e013296b353 | 508 | } |

| dreschpe | 0:5e013296b353 | 509 | |

| dreschpe | 0:5e013296b353 | 510 | if(CurrVal < 0) |

| dreschpe | 0:5e013296b353 | 511 | { |

| dreschpe | 0:5e013296b353 | 512 | *pdst++ = '-'; |

| dreschpe | 0:5e013296b353 | 513 | CurrVal = - CurrVal; |

| dreschpe | 0:5e013296b353 | 514 | } |

| dreschpe | 0:5e013296b353 | 515 | /* insert the value */ |

| dreschpe | 0:5e013296b353 | 516 | while(CurrVal > 0){ |

| dreschpe | 0:5e013296b353 | 517 | tmpval = CurrVal; |

| dreschpe | 0:5e013296b353 | 518 | CurrVal /= 10; |

| dreschpe | 0:5e013296b353 | 519 | tmpval = tmpval - CurrVal*10; |

| dreschpe | 0:5e013296b353 | 520 | charval = '0' + tmpval; |

| dreschpe | 0:5e013296b353 | 521 | tmparray[idx++] = charval; |

| dreschpe | 0:5e013296b353 | 522 | } |

| dreschpe | 0:5e013296b353 | 523 | |

| dreschpe | 0:5e013296b353 | 524 | for(i=0;i<idx;i++) |

| dreschpe | 0:5e013296b353 | 525 | { |

| dreschpe | 0:5e013296b353 | 526 | *pdst++ = tmparray[idx - i - 1]; |

| dreschpe | 0:5e013296b353 | 527 | } |

| dreschpe | 0:5e013296b353 | 528 | *pdst++ = '\0'; |

| dreschpe | 0:5e013296b353 | 529 | |

| dreschpe | 0:5e013296b353 | 530 | return 0; |

| dreschpe | 0:5e013296b353 | 531 | } |

| dreschpe | 0:5e013296b353 | 532 | |

| dreschpe | 0:5e013296b353 | 533 | |

| dreschpe | 0:5e013296b353 | 534 | ft_void_t FT800::Ft_Gpu_Hal_Sleep(ft_uint16_t ms) |

| dreschpe | 0:5e013296b353 | 535 | { |

| dreschpe | 0:5e013296b353 | 536 | wait_ms(ms); |

| dreschpe | 0:5e013296b353 | 537 | } |

| dreschpe | 0:5e013296b353 | 538 | |

| dreschpe | 1:bd671a31e765 | 539 | ft_void_t FT800::Ft_Sound_ON(){ |

| dreschpe | 1:bd671a31e765 | 540 | Ft_Gpu_Hal_Wr8( REG_GPIO, 0x02 | Ft_Gpu_Hal_Rd8( REG_GPIO)); |

| dreschpe | 1:bd671a31e765 | 541 | } |

| dreschpe | 1:bd671a31e765 | 542 | |

| dreschpe | 1:bd671a31e765 | 543 | ft_void_t FT800::Ft_Sound_OFF(){ |

| dreschpe | 1:bd671a31e765 | 544 | Ft_Gpu_Hal_Wr8( REG_GPIO, 0xFD & Ft_Gpu_Hal_Rd8( REG_GPIO)); |

| dreschpe | 1:bd671a31e765 | 545 | } |

| dreschpe | 0:5e013296b353 | 546 | |

| dreschpe | 0:5e013296b353 | 547 | |

| dreschpe | 0:5e013296b353 | 548 | |

| dreschpe | 1:bd671a31e765 | 549 |

EVE FT800

EVE FT800

ADAM

ADAM