mbed-os-sensor-node

Getting started with mbed Client on mbed OS

Warning

This example application is not supported anymore.

Information

History project:

- 17/01/2018 - Using mbed-cli the project is compiled using the use-malloc-for-heap feature enabled

- 24/11/2017 - Added support for uvision5, here instructions

- 02/10/2017 - First Release

This is the mbed Client example for mbed OS. It demonstrates how to register a device with mbed Device Connector, how to read and write values, and how to deregister. If you are unfamiliar with mbed Device Connector, we recommend that you read the introduction to the data model first.

The application:

- Connects to network with 6LoWPAN ND connection.

- Registers with mbed Device Connector.

- Gives mbed Device Connector access to its resources (read and write).

- Sends an incremental number to mbed Device Connector.

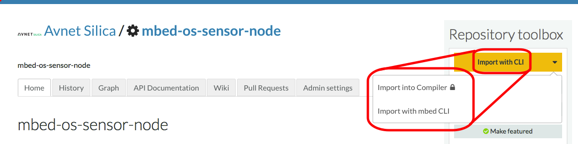

You can compile this project in three ways:

1. Using the Online compiler. Just clicking here:

Information

Learn how to use the Online compiler reading https://docs.mbed.com/docs/mbed-os-handbook/en/latest/dev_tools/online_comp/ page.

2. Using the compiler on your PC

Information

Learn how to use the mbed-cli reading https://docs.mbed.com/docs/mbed-os-handbook/en/latest/dev_tools/cli/ page.

The name of the machine is SILICA_SENSOR_NODE.

3. Exporting to 3rd party tools (IDE)

Information

Learn how to use the mbed-cli reading https://docs.mbed.com/docs/mbed-os-handbook/en/latest/dev_tools/third_party/ page. We have exported the project for you, please read here

Warning

This example requires a Border Router board. For more details please read the Border Router paragraph from this page.

Please read carefully the next pages:

- What to do before to compile the project: read here. This step is indipendent from the way you compile the project.

- How to run the client read here.

DebugConfig/mbed-os-sensor-node_STM32L476JGYx.dbgconf@7:e89dae7682f7, 2018-01-17 (annotated)

- Committer:

- rspelta

- Date:

- Wed Jan 17 13:42:55 2018 +0100

- Revision:

- 7:e89dae7682f7

- Parent:

- 3:b8f21cb512fa

fixed memory heap

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| rspelta | 3:b8f21cb512fa | 1 | // File: STM32L4x5_4x6.dbgconf |

| rspelta | 3:b8f21cb512fa | 2 | // Version: 1.0.0 |

| rspelta | 3:b8f21cb512fa | 3 | // Note: refer to STM32L4x5 and STM32L4x6 Reference manual (RM0351) |

| rspelta | 3:b8f21cb512fa | 4 | // refer to STM32L475xx, STM32L476xx, STM32L486xx, STM32L496xx and STM32L4A6xx datasheets |

| rspelta | 3:b8f21cb512fa | 5 | |

| rspelta | 3:b8f21cb512fa | 6 | // <<< Use Configuration Wizard in Context Menu >>> |

| rspelta | 3:b8f21cb512fa | 7 | |

| rspelta | 3:b8f21cb512fa | 8 | // <h> Debug MCU configuration register (DBGMCU_CR) |

| rspelta | 3:b8f21cb512fa | 9 | // <o0.2> DBG_STANDBY |

| rspelta | 3:b8f21cb512fa | 10 | // <i> Debug Standby mode |

| rspelta | 3:b8f21cb512fa | 11 | // <i> 0: (FCLK=Off, HCLK=Off) The whole digital part is unpowered. |

| rspelta | 3:b8f21cb512fa | 12 | // <i> 1: (FCLK=On, HCLK=On) The digital part is not unpowered and FCLK and HCLK are provided by the internal RC oscillator which remains active |

| rspelta | 3:b8f21cb512fa | 13 | // <o0.1> DBG_STOP |

| rspelta | 3:b8f21cb512fa | 14 | // <i> Debug Stop mode |

| rspelta | 3:b8f21cb512fa | 15 | // <i> 0: (FCLK=Off, HCLK=Off) In STOP mode, the clock controller disables all clocks (including HCLK and FCLK). |

| rspelta | 3:b8f21cb512fa | 16 | // <i> 1: (FCLK=On, HCLK=On) When entering STOP mode, FCLK and HCLK are provided by the internal RC oscillator which remains active in STOP mode. |

| rspelta | 3:b8f21cb512fa | 17 | // <o0.0> DBG_SLEEP |

| rspelta | 3:b8f21cb512fa | 18 | // <i> Debug Sleep mode |

| rspelta | 3:b8f21cb512fa | 19 | // <i> 0: (FCLK=On, HCLK=Off) In Sleep mode, FCLK is clocked by the system clock as previously configured by the software while HCLK is disabled. |

| rspelta | 3:b8f21cb512fa | 20 | // <i> 1: (FCLK=On, HCLK=On) When entering Sleep mode, HCLK is fed by the same clock that is provided to FCLK (system clock as previously configured by the software). |

| rspelta | 3:b8f21cb512fa | 21 | // </h> |

| rspelta | 3:b8f21cb512fa | 22 | DbgMCU_CR = 0x00000007; |

| rspelta | 3:b8f21cb512fa | 23 | |

| rspelta | 3:b8f21cb512fa | 24 | // <h> Debug MCU APB1 freeze register1 (DBGMCU_APB1FZR1) |

| rspelta | 3:b8f21cb512fa | 25 | // <o0.31> DBG_LPTIM1_STOP |

| rspelta | 3:b8f21cb512fa | 26 | // <i> LPTIM1 counter stopped when core is halted |

| rspelta | 3:b8f21cb512fa | 27 | // <i> 0: The counter clock of LPTIM1 is fed even if the core is halted |

| rspelta | 3:b8f21cb512fa | 28 | // <i> 1: The counter clock of LPTIM1 is stopped when the core is halted |

| rspelta | 3:b8f21cb512fa | 29 | // <o0.26> DBG_CAN2_STOP |

| rspelta | 3:b8f21cb512fa | 30 | // <i> bxCAN2 stopped when core is halted (Reserved on STM32L475xx/476xx/486xx devices) |

| rspelta | 3:b8f21cb512fa | 31 | // <i> 0: Same behavior as in normal mode |

| rspelta | 3:b8f21cb512fa | 32 | // <i> 1: The bxCAN2 receive registers are frozen |

| rspelta | 3:b8f21cb512fa | 33 | // <o0.25> DBG_CAN_STOP |

| rspelta | 3:b8f21cb512fa | 34 | // <i> bxCAN1 stopped when core is halted |

| rspelta | 3:b8f21cb512fa | 35 | // <i> 0: Same behavior as in normal mode |

| rspelta | 3:b8f21cb512fa | 36 | // <i> 1: The bxCAN1 receive registers are frozen |

| rspelta | 3:b8f21cb512fa | 37 | // <o0.23> DBG_I2C3_STOP |

| rspelta | 3:b8f21cb512fa | 38 | // <i> I2C3 SMBUS timeout counter stopped when core is halted |

| rspelta | 3:b8f21cb512fa | 39 | // <i> 0: Same behavior as in normal mode |

| rspelta | 3:b8f21cb512fa | 40 | // <i> 1: The I2C3 SMBus timeout is frozen |

| rspelta | 3:b8f21cb512fa | 41 | // <o0.22> DBG_I2C2_STOP |

| rspelta | 3:b8f21cb512fa | 42 | // <i> I2C2 SMBUS timeout counter stopped when core is halted |

| rspelta | 3:b8f21cb512fa | 43 | // <i> 0: Same behavior as in normal mode |

| rspelta | 3:b8f21cb512fa | 44 | // <i> 1: The I2C2 SMBus timeout is frozen |

| rspelta | 3:b8f21cb512fa | 45 | // <o0.21> DBG_I2C1_STOP |

| rspelta | 3:b8f21cb512fa | 46 | // <i> I2C1 SMBUS timeout counter stopped when core is halted |

| rspelta | 3:b8f21cb512fa | 47 | // <i> 0: Same behavior as in normal mode |

| rspelta | 3:b8f21cb512fa | 48 | // <i> 1: The I2C1 SMBus timeout is frozen |

| rspelta | 3:b8f21cb512fa | 49 | // <o0.12> DBG_IWDG_STOP |

| rspelta | 3:b8f21cb512fa | 50 | // <i> Independent watchdog counter stopped when core is halted |

| rspelta | 3:b8f21cb512fa | 51 | // <i> 0: The independent watchdog counter clock continues even if the core is halted |

| rspelta | 3:b8f21cb512fa | 52 | // <i> 1: The independent watchdog counter clock is stopped when the core is halted |

| rspelta | 3:b8f21cb512fa | 53 | // <o0.11> DBG_WWDG_STOP |

| rspelta | 3:b8f21cb512fa | 54 | // <i> Window watchdog counter stopped when core is halted |

| rspelta | 3:b8f21cb512fa | 55 | // <i> 0: The window watchdog counter clock continues even if the core is halted |

| rspelta | 3:b8f21cb512fa | 56 | // <i> 1: The window watchdog counter clock is stopped when the core is halted |

| rspelta | 3:b8f21cb512fa | 57 | // <o0.10> DBG_RTC_STOP |

| rspelta | 3:b8f21cb512fa | 58 | // <i> RTC counter stopped when core is halted |

| rspelta | 3:b8f21cb512fa | 59 | // <i> 0: The clock of the RTC counter is fed even if the core is halted |

| rspelta | 3:b8f21cb512fa | 60 | // <i> 1: The clock of the RTC counter is stopped when the core is halted |

| rspelta | 3:b8f21cb512fa | 61 | // <o0.5> DBG_TIM7_STOP |

| rspelta | 3:b8f21cb512fa | 62 | // <i> TIM7 counter stopped when core is halted |

| rspelta | 3:b8f21cb512fa | 63 | // <i> 0: The counter clock of TIM7 is fed even if the core is halted |

| rspelta | 3:b8f21cb512fa | 64 | // <i> 1: The counter clock of TIM7 is stopped when the core is halted |

| rspelta | 3:b8f21cb512fa | 65 | // <o0.4> DBG_TIM6_STOP |

| rspelta | 3:b8f21cb512fa | 66 | // <i> TIM6 counter stopped when core is halted |

| rspelta | 3:b8f21cb512fa | 67 | // <i> 0: The counter clock of TIM6 is fed even if the core is halted |

| rspelta | 3:b8f21cb512fa | 68 | // <i> 1: The counter clock of TIM6 is stopped when the core is halted |

| rspelta | 3:b8f21cb512fa | 69 | // <o0.3> DBG_TIM5_STOP |

| rspelta | 3:b8f21cb512fa | 70 | // <i> TIM5 counter stopped when core is halted |

| rspelta | 3:b8f21cb512fa | 71 | // <i> 0: The counter clock of TIM5 is fed even if the core is halted |

| rspelta | 3:b8f21cb512fa | 72 | // <i> 1: The counter clock of TIM5 is stopped when the core is halted |

| rspelta | 3:b8f21cb512fa | 73 | // <o0.2> DBG_TIM4_STOP |

| rspelta | 3:b8f21cb512fa | 74 | // <i> TIM4 counter stopped when core is halted |

| rspelta | 3:b8f21cb512fa | 75 | // <i> 0: The counter clock of TIM4 is fed even if the core is halted |

| rspelta | 3:b8f21cb512fa | 76 | // <i> 1: The counter clock of TIM4 is stopped when the core is halted |

| rspelta | 3:b8f21cb512fa | 77 | // <o0.1> DBG_TIM3_STOP |

| rspelta | 3:b8f21cb512fa | 78 | // <i> TIM3 counter stopped when core is halted |

| rspelta | 3:b8f21cb512fa | 79 | // <i> 0: The counter clock of TIM3 is fed even if the core is halted |

| rspelta | 3:b8f21cb512fa | 80 | // <i> 1: The counter clock of TIM3 is stopped when the core is halted |

| rspelta | 3:b8f21cb512fa | 81 | // <o0.0> DBG_TIM2_STOP |

| rspelta | 3:b8f21cb512fa | 82 | // <i> TIM2 counter stopped when core is halted |

| rspelta | 3:b8f21cb512fa | 83 | // <i> 0: The counter clock of TIM2 is fed even if the core is halted |

| rspelta | 3:b8f21cb512fa | 84 | // <i> 1: The counter clock of TIM2 is stopped when the core is halted |

| rspelta | 3:b8f21cb512fa | 85 | // </h> |

| rspelta | 3:b8f21cb512fa | 86 | DbgMCU_APB1_Fz1 = 0x00000000; |

| rspelta | 3:b8f21cb512fa | 87 | |

| rspelta | 3:b8f21cb512fa | 88 | // <h> Debug MCU APB1 freeze register 2 (DBGMCU_APB1FZR2) |

| rspelta | 3:b8f21cb512fa | 89 | // <o0.5> DBG_LPTIM2_STOP |

| rspelta | 3:b8f21cb512fa | 90 | // <i> LPTIM2 counter stopped when core is halted |

| rspelta | 3:b8f21cb512fa | 91 | // <i> 0: The counter clock of LPTIM2 is fed even if the core is halted |

| rspelta | 3:b8f21cb512fa | 92 | // <i> 1: The counter clock of LPTIM2 is stopped when the core is halted |

| rspelta | 3:b8f21cb512fa | 93 | // <o0.1> DBG_I2C4_STOP |

| rspelta | 3:b8f21cb512fa | 94 | // <i> I2C4 SMBUS timeout counter stopped when core is halted (Reserved on STM32L475xx/476xx/486xx devices) |

| rspelta | 3:b8f21cb512fa | 95 | // <i> 0: Same behavior as in normal mode |

| rspelta | 3:b8f21cb512fa | 96 | // <i> 1: The I2C4 SMBus timeout is frozen |

| rspelta | 3:b8f21cb512fa | 97 | // </h> |

| rspelta | 3:b8f21cb512fa | 98 | DbgMCU_APB1_Fz2 = 0x00000000; |

| rspelta | 3:b8f21cb512fa | 99 | |

| rspelta | 3:b8f21cb512fa | 100 | // <h> Debug MCU APB2 freeze register (DBGMCU_APB2FZR) |

| rspelta | 3:b8f21cb512fa | 101 | // <o0.18> DBG_TIM17_STOP |

| rspelta | 3:b8f21cb512fa | 102 | // <i> TIM17 counter stopped when core is halted |

| rspelta | 3:b8f21cb512fa | 103 | // <i> 0: The clock of the TIM17 counter is fed even if the core is halted |

| rspelta | 3:b8f21cb512fa | 104 | // <i> 1: The clock of the TIM17 counter is stopped when the core is halted |

| rspelta | 3:b8f21cb512fa | 105 | // <o0.17> DBG_TIM16_STOP |

| rspelta | 3:b8f21cb512fa | 106 | // <i> TIM16 counter stopped when core is halted |

| rspelta | 3:b8f21cb512fa | 107 | // <i> 0: The clock of the TIM16 counter is fed even if the core is halted |

| rspelta | 3:b8f21cb512fa | 108 | // <i> 1: The clock of the TIM16 counter is stopped when the core is halted |

| rspelta | 3:b8f21cb512fa | 109 | // <o0.16> DBG_TIM15_STOP |

| rspelta | 3:b8f21cb512fa | 110 | // <i> TIM15 counter stopped when core is halted |

| rspelta | 3:b8f21cb512fa | 111 | // <i> 0: The clock of the TIM15 counter is fed even if the core is halted |

| rspelta | 3:b8f21cb512fa | 112 | // <i> 1: The clock of the TIM15 counter is stopped when the core is halted |

| rspelta | 3:b8f21cb512fa | 113 | // <o0.13> DBG_TIM8_STOP |

| rspelta | 3:b8f21cb512fa | 114 | // <i> TIM8 counter stopped when core is halted |

| rspelta | 3:b8f21cb512fa | 115 | // <i> 0: The clock of the TIM8 counter is fed even if the core is halted |

| rspelta | 3:b8f21cb512fa | 116 | // <i> 1: The clock of the TIM8 counter is stopped when the core is halted |

| rspelta | 3:b8f21cb512fa | 117 | // <o0.11> DBG_TIM1_STOP |

| rspelta | 3:b8f21cb512fa | 118 | // <i> TIM1 counter stopped when core is halted |

| rspelta | 3:b8f21cb512fa | 119 | // <i> 0: The clock of the TIM1 counter is fed even if the core is halted |

| rspelta | 3:b8f21cb512fa | 120 | // <i> 1: The clock of the TIM1 counter is stopped when the core is halted |

| rspelta | 3:b8f21cb512fa | 121 | // </h> |

| rspelta | 3:b8f21cb512fa | 122 | DbgMCU_APB2_Fz = 0x00000000; |

| rspelta | 3:b8f21cb512fa | 123 | // </h> |

| rspelta | 3:b8f21cb512fa | 124 | |

| rspelta | 3:b8f21cb512fa | 125 | // <<< end of configuration section >>> |