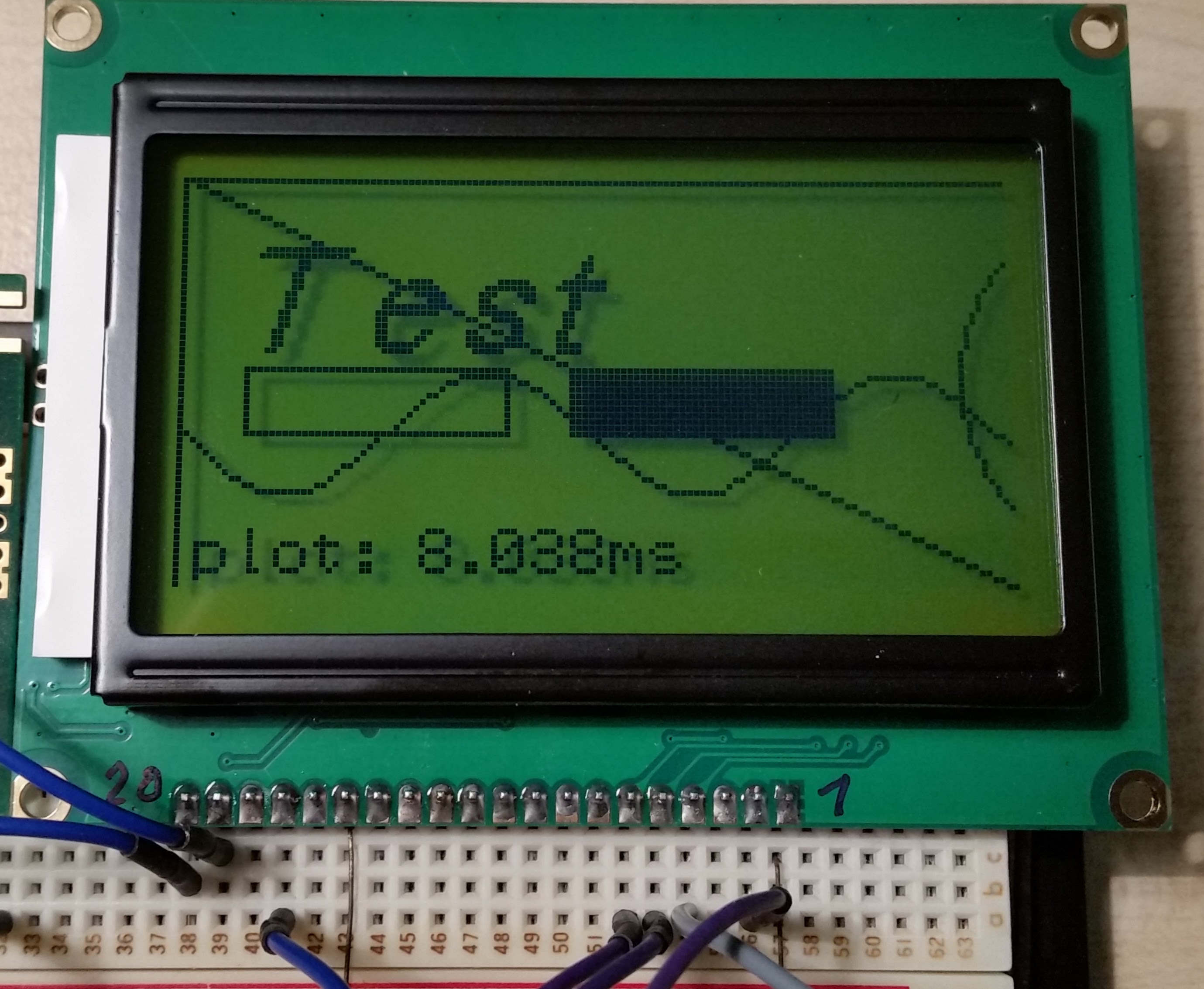

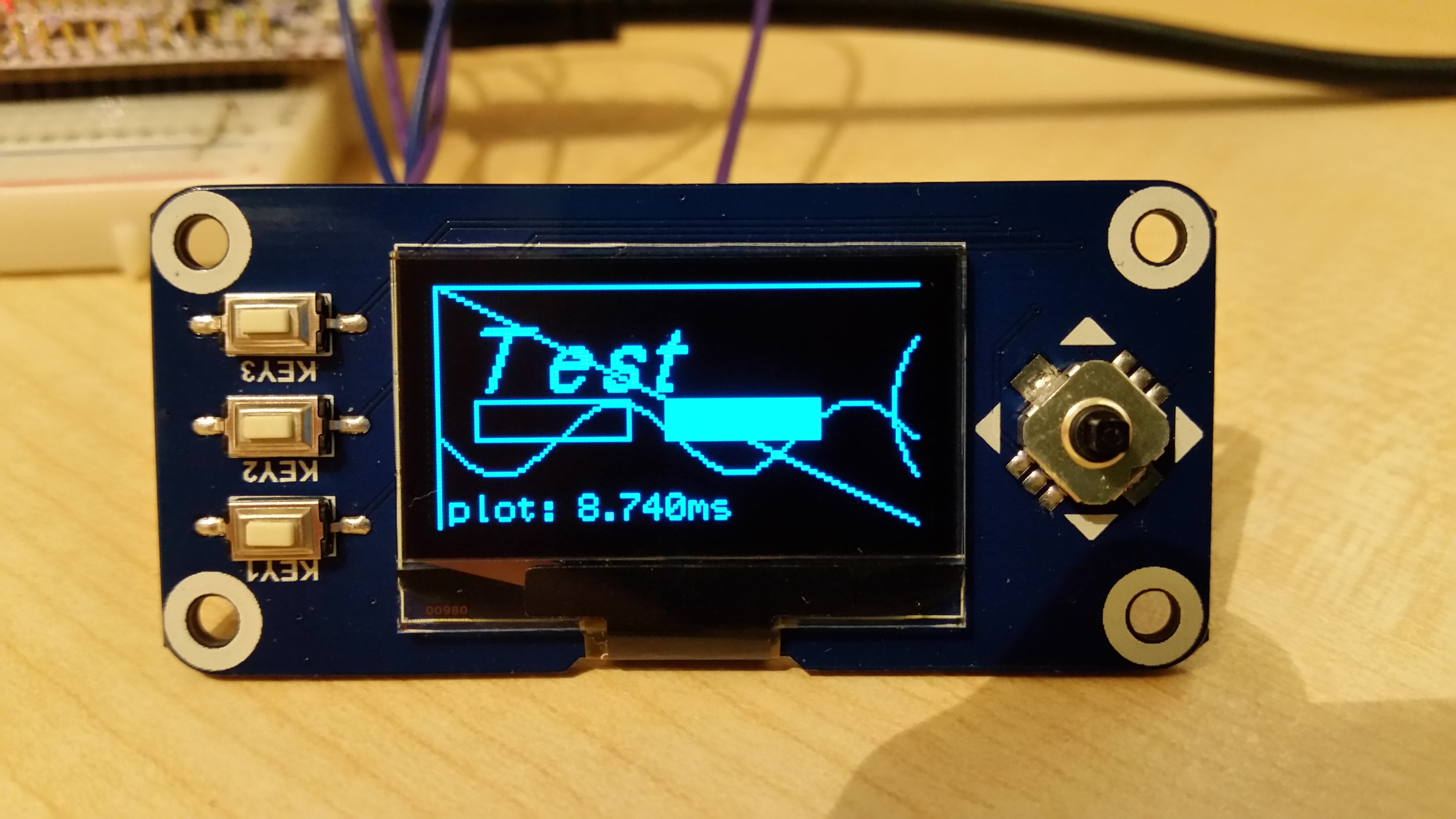

UniGraphic-Fork for ST7920-LCD-controller and SH1106. Tested with 128x64 LCD with SPI and 128x64-OLED with IIC

Dependents: UniGraphic-St7920-Test AfficheurUTILECO

Fork of UniGraphic by

Fork of the UniGraphic-Library for monochrome LCDs with ST7920 controller and 128x64-IIC-OLED-Display with SH1106-Controller

Had to adapt LCD for following reasons:

- Give access to screenbuffer buffer[] to parent class

- pixel() and pixel_read() as they are hardware-dependent

- added reset-pin to IIC-Interface

GraphicDisplay:: sends buffer to LCD when auto_update is set to true.

Testprogram for ST7920 can be found here:

https://developer.mbed.org/users/charly/code/UniGraphic-St7920-Test/

Diff: Protocols/SPI8.cpp

- Revision:

- 7:bb0383b91104

- Parent:

- 5:b222a9461d6b

- Child:

- 11:b842b8e332cb

diff -r 8356d48a07db -r bb0383b91104 Protocols/SPI8.cpp

--- a/Protocols/SPI8.cpp Mon Feb 16 01:18:29 2015 +0000

+++ b/Protocols/SPI8.cpp Tue Feb 17 11:02:06 2015 +0000

@@ -135,30 +135,6 @@

_CS = 1;

#endif

}

-unsigned int SPI8::rd_data32_wdummy()

-{

-#ifdef USE_CS

- _CS = 0;

-#endif

- unsigned int r=0;

- _DC.write(1); // 1=data

-

- r |= _spi.write(0); // we get only 7bit valid, first bit was the dummy cycle

- r <<= 8;

- r |= _spi.write(0);

- r <<= 8;

- r |= _spi.write(0);

- r <<= 8;

- r |= _spi.write(0);

- r <<= 1; // 32bits are aligned, now collecting bit_0

- r |= (_spi.write(0) >> 7);

- // we clocked 7 more bit so ILI waiting for 8th, we need to reset spi bus

- _CS = 1; // force CS HIG to interupt the cmd

-#ifndef USE_CS //if CS is not used, force fixed LOW again

- _CS = 0;

-#endif

- return r;

-}

unsigned short SPI8::rd_gram()

{

#ifdef USE_CS

@@ -181,6 +157,50 @@

r = RGB18to16((r&0xFC0000)>>16, (r&0xFC00)>>8, r&0xFC);// 18bit pixel, rrrrrr00_gggggg00_bbbbbb00, converted to 16bit

return (unsigned short)r;

}

+unsigned int SPI8::rd_reg_data32(unsigned char reg)

+{

+#ifdef USE_CS

+ _CS = 0;

+#endif

+ wr_cmd8(reg);

+ unsigned int r=0;

+ _DC.write(1); // 1=data

+

+ r |= _spi.write(0); // we get only 7bit valid, first bit was the dummy cycle

+ r <<= 8;

+ r |= _spi.write(0);

+ r <<= 8;

+ r |= _spi.write(0);

+ r <<= 8;

+ r |= _spi.write(0);

+ r <<= 1; // 32bits are aligned, now collecting bit_0

+ r |= (_spi.write(0) >> 7);

+ // we clocked 7 more bit so ILI waiting for 8th, we need to reset spi bus

+ _CS = 1; // force CS HIG to interupt the cmd

+#ifndef USE_CS //if CS is not used, force fixed LOW again

+ _CS = 0;

+#endif

+ return r;

+}

+unsigned int SPI8::rd_extcreg_data32(unsigned char reg, unsigned char SPIreadenablecmd)

+{

+ unsigned int r=0;

+ for(int regparam=1; regparam<4; regparam++) // when reading EXTC regs, first parameter is always dummy, so start with 1

+ {

+ wr_cmd8(SPIreadenablecmd); // spi-in enable cmd, 0xD9 (ili9341) or 0xFB (ili9488) or don't know

+ wr_data8(0xF0|regparam); // in low nibble specify which reg parameter we want

+ wr_cmd8(reg); // now send cmd (select register we want to read)

+ _DC.write(1); // 1=data

+ r <<= 8;

+ r |= _spi.write(0);

+ // r = _spi.write(0) >> 8; for 16bit

+ }

+_CS = 1; // force CS HIG to interupt the cmd

+#ifndef USE_CS //if CS is not used, force fixed LOW again

+ _CS = 0;

+#endif

+ return r;

+}

void SPI8::hw_reset()

{

wait_ms(15);