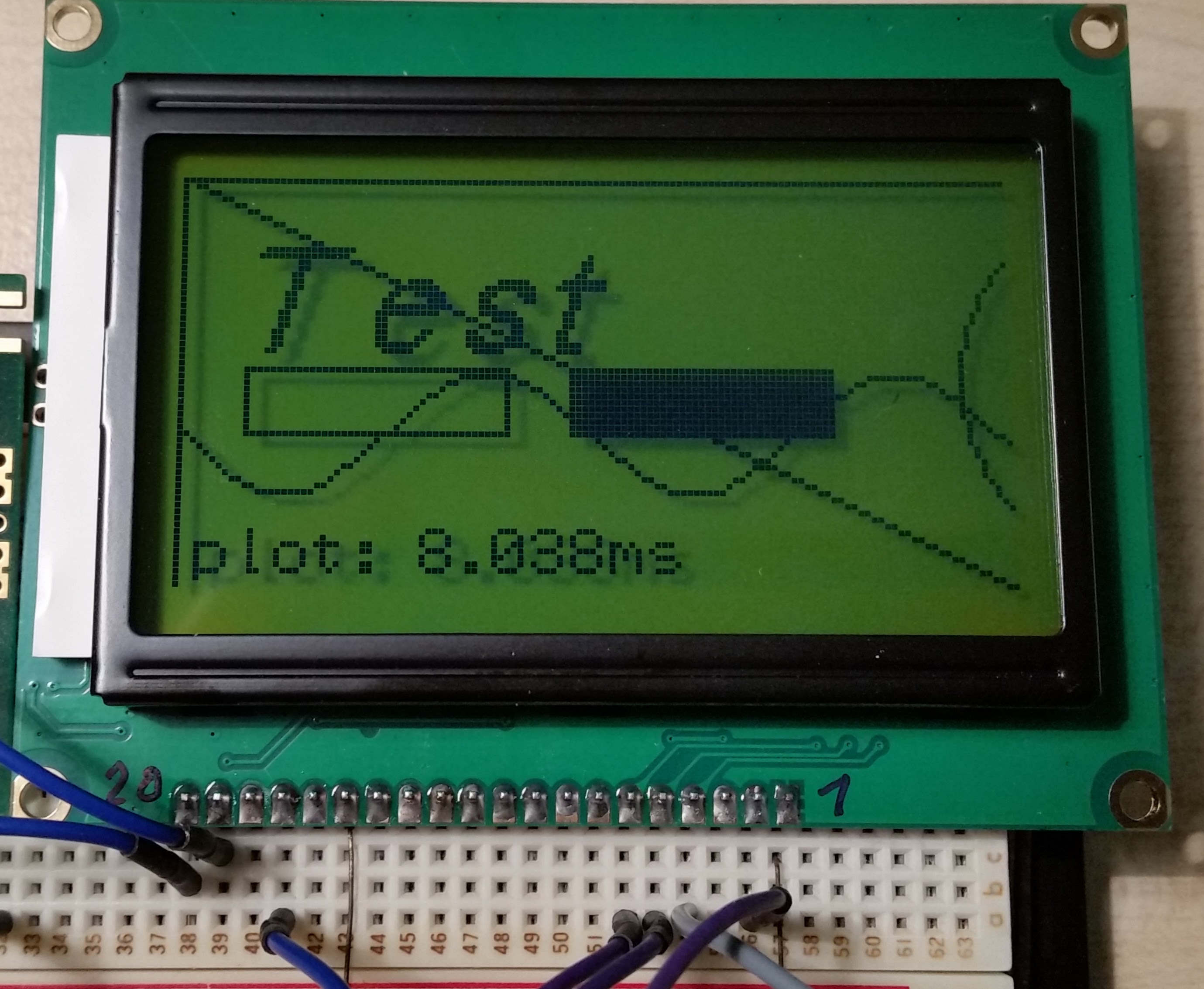

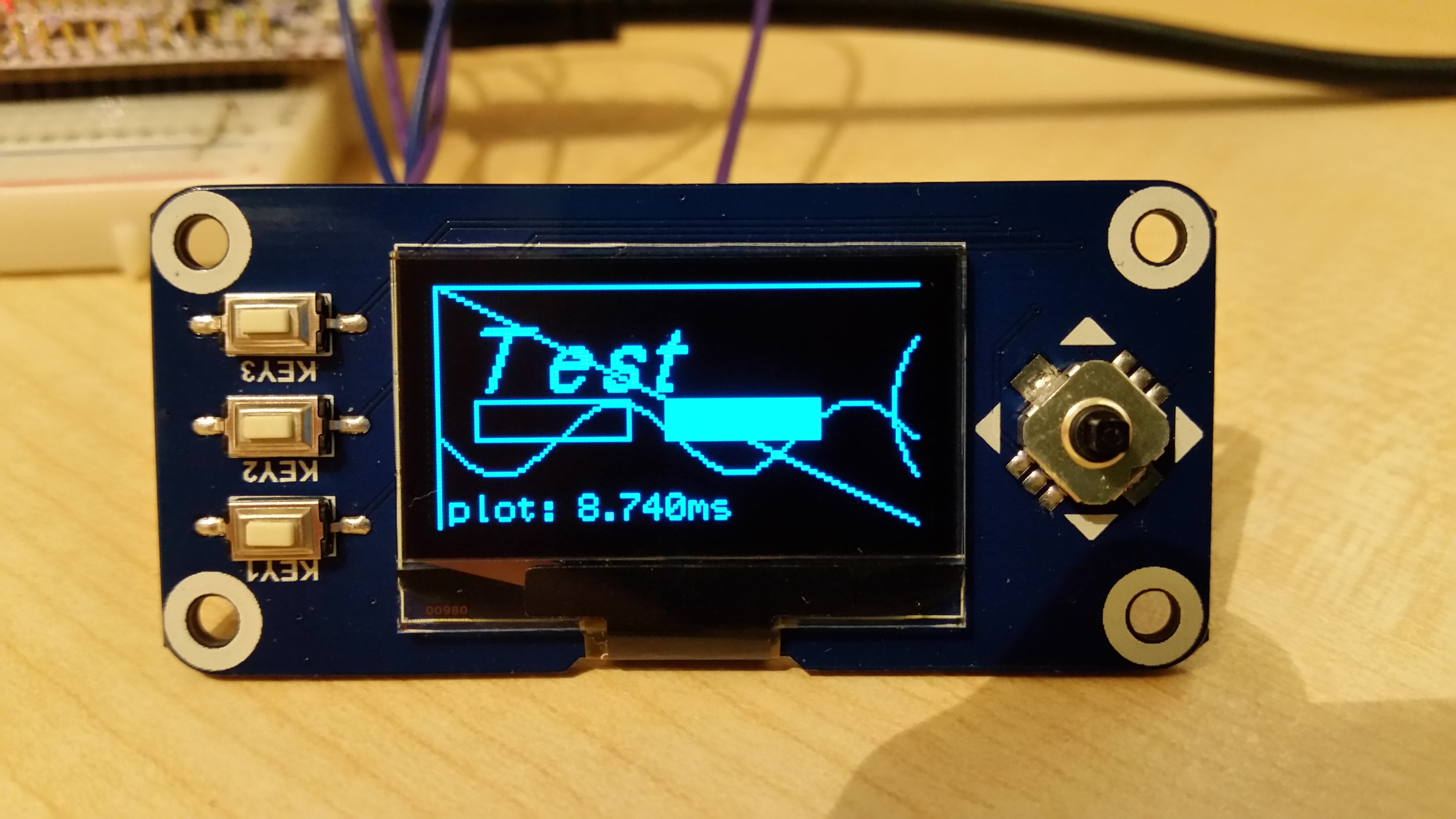

UniGraphic-Fork for ST7920-LCD-controller and SH1106. Tested with 128x64 LCD with SPI and 128x64-OLED with IIC

Dependents: UniGraphic-St7920-Test AfficheurUTILECO

Fork of UniGraphic by

Fork of the UniGraphic-Library for monochrome LCDs with ST7920 controller and 128x64-IIC-OLED-Display with SH1106-Controller

Had to adapt LCD for following reasons:

- Give access to screenbuffer buffer[] to parent class

- pixel() and pixel_read() as they are hardware-dependent

- added reset-pin to IIC-Interface

GraphicDisplay:: sends buffer to LCD when auto_update is set to true.

Testprogram for ST7920 can be found here:

https://developer.mbed.org/users/charly/code/UniGraphic-St7920-Test/

Inits/SSD1306.cpp@36:668396f861d2, 2018-04-22 (annotated)

- Committer:

- charly

- Date:

- Sun Apr 22 21:41:24 2018 +0000

- Revision:

- 36:668396f861d2

- Parent:

- 33:f87f06292637

- Child:

- 37:5de028b08308

Added SH1106 for OLED Display 128x64 via IIC

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| dreschpe | 12:9c8f3076347c | 1 | /* mbed UniGraphic library - Device specific class |

| dreschpe | 12:9c8f3076347c | 2 | * Copyright (c) 2015 Peter Drescher |

| dreschpe | 12:9c8f3076347c | 3 | * Released under the MIT License: http://mbed.org/license/mit |

| dreschpe | 12:9c8f3076347c | 4 | */ |

| dreschpe | 12:9c8f3076347c | 5 | |

| dreschpe | 12:9c8f3076347c | 6 | #include "Protocols.h" |

| dreschpe | 12:9c8f3076347c | 7 | #include "SSD1306.h" |

| dreschpe | 12:9c8f3076347c | 8 | |

| dreschpe | 12:9c8f3076347c | 9 | ////////////////////////////////////////////////////////////////////////////////// |

| dreschpe | 12:9c8f3076347c | 10 | // display settings /////////////////////////////////////////////////////// |

| dreschpe | 12:9c8f3076347c | 11 | ///////////////////////////////////////////////////////////////////////// |

| dreschpe | 12:9c8f3076347c | 12 | |

| dreschpe | 12:9c8f3076347c | 13 | |

| charly | 36:668396f861d2 | 14 | #define IC_X_SEGS 132 // 132 SEG |

| charly | 36:668396f861d2 | 15 | #define IC_Y_COMS 64 // 64 COM |

| dreschpe | 12:9c8f3076347c | 16 | |

| dreschpe | 12:9c8f3076347c | 17 | #define SSD1306_SETCONTRAST 0x81 |

| dreschpe | 12:9c8f3076347c | 18 | #define SSD1306_DISPLAYALLON_RESUME 0xA4 |

| dreschpe | 12:9c8f3076347c | 19 | #define SSD1306_DISPLAYALLON 0xA5 |

| dreschpe | 12:9c8f3076347c | 20 | #define SSD1306_NORMALDISPLAY 0xA6 |

| dreschpe | 12:9c8f3076347c | 21 | #define SSD1306_INVERTDISPLAY 0xA7 |

| dreschpe | 12:9c8f3076347c | 22 | #define SSD1306_DISPLAYOFF 0xAE |

| dreschpe | 12:9c8f3076347c | 23 | #define SSD1306_DISPLAYON 0xAF |

| dreschpe | 12:9c8f3076347c | 24 | #define SSD1306_SETDISPLAYOFFSET 0xD3 |

| dreschpe | 12:9c8f3076347c | 25 | #define SSD1306_SETCOMPINS 0xDA |

| dreschpe | 12:9c8f3076347c | 26 | #define SSD1306_SETVCOMDETECT 0xDB |

| dreschpe | 12:9c8f3076347c | 27 | #define SSD1306_SETDISPLAYCLOCKDIV 0xD5 |

| dreschpe | 12:9c8f3076347c | 28 | #define SSD1306_SETPRECHARGE 0xD9 |

| dreschpe | 12:9c8f3076347c | 29 | #define SSD1306_SETMULTIPLEX 0xA8 |

| dreschpe | 12:9c8f3076347c | 30 | #define SSD1306_SETLOWCOLUMN 0x00 |

| dreschpe | 12:9c8f3076347c | 31 | #define SSD1306_SETHIGHCOLUMN 0x10 |

| dreschpe | 12:9c8f3076347c | 32 | #define SSD1306_SETSTARTLINE 0x40 |

| dreschpe | 12:9c8f3076347c | 33 | #define SSD1306_MEMORYMODE 0x20 |

| dreschpe | 12:9c8f3076347c | 34 | #define SSD1306_COMSCANINC 0xC0 |

| dreschpe | 12:9c8f3076347c | 35 | #define SSD1306_COMSCANDEC 0xC8 |

| dreschpe | 12:9c8f3076347c | 36 | #define SSD1306_SEGREMAP 0xA0 |

| dreschpe | 12:9c8f3076347c | 37 | #define SSD1306_CHARGEPUMP 0x8D |

| dreschpe | 12:9c8f3076347c | 38 | |

| dreschpe | 12:9c8f3076347c | 39 | SSD1306::SSD1306(proto_t displayproto, PortName port, PinName CS, PinName reset, PinName DC, PinName WR, PinName RD, const char *name , unsigned int LCDSIZE_X, unsigned int LCDSIZE_Y) |

| dreschpe | 12:9c8f3076347c | 40 | : LCD(displayproto, port, CS, reset, DC, WR, RD, LCDSIZE_X, LCDSIZE_Y, IC_X_SEGS, IC_Y_COMS, name) |

| dreschpe | 12:9c8f3076347c | 41 | { |

| dreschpe | 12:9c8f3076347c | 42 | hw_reset(); |

| dreschpe | 12:9c8f3076347c | 43 | BusEnable(true); |

| dreschpe | 12:9c8f3076347c | 44 | init(); |

| dreschpe | 12:9c8f3076347c | 45 | cls(); |

| dreschpe | 12:9c8f3076347c | 46 | set_orientation(1); |

| dreschpe | 12:9c8f3076347c | 47 | locate(0,0); |

| dreschpe | 12:9c8f3076347c | 48 | } |

| dreschpe | 12:9c8f3076347c | 49 | SSD1306::SSD1306(proto_t displayproto, int Hz, PinName mosi, PinName miso, PinName sclk, PinName CS, PinName reset, PinName DC, const char *name, unsigned int LCDSIZE_X, unsigned int LCDSIZE_Y) |

| dreschpe | 12:9c8f3076347c | 50 | : LCD(displayproto, Hz, mosi, miso, sclk, CS, reset, DC, LCDSIZE_X, LCDSIZE_Y, IC_X_SEGS, IC_Y_COMS, name) |

| dreschpe | 12:9c8f3076347c | 51 | { |

| dreschpe | 12:9c8f3076347c | 52 | hw_reset(); |

| dreschpe | 12:9c8f3076347c | 53 | BusEnable(true); |

| dreschpe | 12:9c8f3076347c | 54 | init(); |

| dreschpe | 12:9c8f3076347c | 55 | cls(); |

| dreschpe | 12:9c8f3076347c | 56 | set_orientation(1); |

| dreschpe | 12:9c8f3076347c | 57 | locate(0,0); |

| dreschpe | 12:9c8f3076347c | 58 | } |

| dreschpe | 33:f87f06292637 | 59 | |

| charly | 36:668396f861d2 | 60 | SSD1306::SSD1306(proto_t displayproto, int Hz, int address, PinName sda, PinName scl, PinName reset, const char* name , unsigned int LCDSIZE_X, unsigned int LCDSIZE_Y) |

| charly | 36:668396f861d2 | 61 | : LCD(displayproto, Hz, address, sda, scl,reset, LCDSIZE_X, LCDSIZE_Y, IC_X_SEGS, IC_Y_COMS, name) |

| dreschpe | 33:f87f06292637 | 62 | { |

| charly | 36:668396f861d2 | 63 | hw_reset(); |

| dreschpe | 33:f87f06292637 | 64 | init(); |

| dreschpe | 33:f87f06292637 | 65 | cls(); |

| dreschpe | 33:f87f06292637 | 66 | set_orientation(1); |

| dreschpe | 33:f87f06292637 | 67 | locate(0,0); |

| dreschpe | 33:f87f06292637 | 68 | } |

| dreschpe | 33:f87f06292637 | 69 | |

| dreschpe | 33:f87f06292637 | 70 | |

| dreschpe | 12:9c8f3076347c | 71 | // reset and init the lcd controller |

| dreschpe | 12:9c8f3076347c | 72 | void SSD1306::init() |

| dreschpe | 12:9c8f3076347c | 73 | { |

| dreschpe | 12:9c8f3076347c | 74 | /* Start Initial Sequence ----------------------------------------------------*/ |

| charly | 36:668396f861d2 | 75 | /* SSD1306 |

| dreschpe | 12:9c8f3076347c | 76 | // wr_cmd8(0xE2); // sw reset |

| dreschpe | 12:9c8f3076347c | 77 | wait_ms(15); |

| dreschpe | 12:9c8f3076347c | 78 | |

| Geremia | 13:d8c593fa7705 | 79 | wr_cmd8(SSD1306_DISPLAYOFF); // no problem in SPI_16 for single byte cmds |

| Geremia | 13:d8c593fa7705 | 80 | wr_cmd16((SSD1306_SETDISPLAYCLOCKDIV<<8)|0x80); // wr_cmd16 for multibyte cmds issue in SPI16 mode |

| Geremia | 13:d8c593fa7705 | 81 | // wr_cmd8(0x80); // in SPI_16 it would become 0xE380 and will break things up |

| Geremia | 13:d8c593fa7705 | 82 | wr_cmd16((SSD1306_SETMULTIPLEX<<8)|63); |

| Geremia | 13:d8c593fa7705 | 83 | // wr_cmd8(63); |

| dreschpe | 12:9c8f3076347c | 84 | |

| Geremia | 13:d8c593fa7705 | 85 | wr_cmd16((SSD1306_SETDISPLAYOFFSET<<8)|0x00); |

| Geremia | 13:d8c593fa7705 | 86 | // wr_cmd8(0x0); |

| dreschpe | 12:9c8f3076347c | 87 | |

| dreschpe | 12:9c8f3076347c | 88 | wr_cmd8(SSD1306_SETSTARTLINE | 0x0); // line #0 |

| dreschpe | 12:9c8f3076347c | 89 | |

| Geremia | 13:d8c593fa7705 | 90 | wr_cmd16((SSD1306_CHARGEPUMP<<8)|0x14); |

| Geremia | 13:d8c593fa7705 | 91 | // wr_cmd8(0x14); // 0x10 |

| dreschpe | 12:9c8f3076347c | 92 | |

| Geremia | 13:d8c593fa7705 | 93 | wr_cmd16((SSD1306_MEMORYMODE<<8)|0x00); |

| Geremia | 13:d8c593fa7705 | 94 | // wr_cmd8(0x00); // 0x0 act like ks0108 |

| dreschpe | 12:9c8f3076347c | 95 | |

| dreschpe | 12:9c8f3076347c | 96 | wr_cmd8(SSD1306_SEGREMAP ); //| 0x1); |

| dreschpe | 12:9c8f3076347c | 97 | |

| dreschpe | 12:9c8f3076347c | 98 | wr_cmd8(SSD1306_COMSCANDEC); |

| dreschpe | 12:9c8f3076347c | 99 | |

| Geremia | 13:d8c593fa7705 | 100 | wr_cmd16((SSD1306_SETCOMPINS<<8)|0x12); |

| Geremia | 13:d8c593fa7705 | 101 | // wr_cmd8(0x12); // LCDSIZE_Y == 32 ? 0x02 : 0x12); |

| dreschpe | 12:9c8f3076347c | 102 | |

| Geremia | 13:d8c593fa7705 | 103 | wr_cmd16((SSD1306_SETCONTRAST<<8)|0xCF); |

| Geremia | 13:d8c593fa7705 | 104 | // wr_cmd8(0xCF); // _rawHeight == 32 ? 0x8F : ((vccstate == SSD1306_EXTERNALVCC) ? 0x9F : 0xCF) ); |

| dreschpe | 12:9c8f3076347c | 105 | |

| Geremia | 13:d8c593fa7705 | 106 | wr_cmd16((SSD1306_SETPRECHARGE<<8)|0xF1); |

| Geremia | 13:d8c593fa7705 | 107 | // wr_cmd8(0xF1); // : 0x22); |

| dreschpe | 12:9c8f3076347c | 108 | |

| Geremia | 13:d8c593fa7705 | 109 | wr_cmd16((SSD1306_SETVCOMDETECT<<8)|0x40); |

| Geremia | 13:d8c593fa7705 | 110 | // wr_cmd8(0x40); |

| dreschpe | 12:9c8f3076347c | 111 | |

| dreschpe | 12:9c8f3076347c | 112 | wr_cmd8(SSD1306_DISPLAYALLON_RESUME); |

| dreschpe | 12:9c8f3076347c | 113 | |

| dreschpe | 12:9c8f3076347c | 114 | //wr_cmd8(SSD1306_NORMALDISPLAY); |

| dreschpe | 12:9c8f3076347c | 115 | wr_cmd8(SSD1306_INVERTDISPLAY); |

| dreschpe | 12:9c8f3076347c | 116 | |

| dreschpe | 12:9c8f3076347c | 117 | wr_cmd8(SSD1306_DISPLAYON); |

| charly | 36:668396f861d2 | 118 | */ |

| charly | 36:668396f861d2 | 119 | |

| charly | 36:668396f861d2 | 120 | //SH1106 |

| charly | 36:668396f861d2 | 121 | wr_cmd8(0xAE);//--turn off oled panel |

| charly | 36:668396f861d2 | 122 | wr_cmd8(0x02);//---set low column address |

| charly | 36:668396f861d2 | 123 | wr_cmd8(0x10);//---set high column address |

| charly | 36:668396f861d2 | 124 | wr_cmd8(0x40);//--set start line address Set Mapping RAM Display Start Line (0x00~0x3F) |

| charly | 36:668396f861d2 | 125 | wr_cmd8(0x81);//--set contrast control register |

| charly | 36:668396f861d2 | 126 | wr_cmd8(0xA0);//--Set contrast |

| charly | 36:668396f861d2 | 127 | wr_cmd8(0xA8);//--set multiplex ratio(1 to 64) |

| charly | 36:668396f861d2 | 128 | wr_cmd8(0x3F);//--1/64 duty |

| charly | 36:668396f861d2 | 129 | wr_cmd8(0xD3);//-set display offset Shift Mapping RAM Counter (0x00~0x3F) |

| charly | 36:668396f861d2 | 130 | wr_cmd8(0x00);//-not offset |

| charly | 36:668396f861d2 | 131 | wr_cmd8(0xd5);//--set display clock divide ratio/oscillator frequency |

| charly | 36:668396f861d2 | 132 | wr_cmd8(0x80);//--set divide ratio, Set Clock as 100 Frames/Sec |

| charly | 36:668396f861d2 | 133 | wr_cmd8(0xD9);//--set pre-charge period |

| charly | 36:668396f861d2 | 134 | wr_cmd8(0xF1);//Set Pre-Charge as 15 Clocks & Discharge as 1 Clock |

| charly | 36:668396f861d2 | 135 | wr_cmd8(0xDA);//--set com pins hardware configuration |

| charly | 36:668396f861d2 | 136 | wr_cmd8(0x12); // or 0x02 |

| charly | 36:668396f861d2 | 137 | wr_cmd8(0xDB);//--set vcomh |

| charly | 36:668396f861d2 | 138 | wr_cmd8(0x40);//Set VCOM Deselect Level |

| charly | 36:668396f861d2 | 139 | //wr_cmd8(0x20);//-Set Page Addressing Mode (0x00/0x01/0x02) // not on SH1106 |

| charly | 36:668396f861d2 | 140 | wr_cmd8(0xA4);// Disable Entire Display On (0xa4/0xa5) |

| charly | 36:668396f861d2 | 141 | wr_cmd8(0xA6);// Disable Inverse Display On (0xa6/a7) |

| charly | 36:668396f861d2 | 142 | |

| charly | 36:668396f861d2 | 143 | wr_cmd8(0xA1); // reverse order |

| charly | 36:668396f861d2 | 144 | //wr_cmd8(0xC0);//Set COM/Row Scan Direction |

| charly | 36:668396f861d2 | 145 | wr_cmd8(0xC8); //reverse direction |

| charly | 36:668396f861d2 | 146 | wr_cmd8(0xAF);//--turn on oled panel |

| dreschpe | 12:9c8f3076347c | 147 | } |

| dreschpe | 12:9c8f3076347c | 148 | |

| dreschpe | 12:9c8f3076347c | 149 | //////////////////////////////////////////////////////////////////// |

| dreschpe | 12:9c8f3076347c | 150 | // functions that overrides the standard ones implemented in LCD.cpp |

| dreschpe | 12:9c8f3076347c | 151 | //////////////////////////////////////////////////////////////////// |

| dreschpe | 12:9c8f3076347c | 152 | |

| charly | 36:668396f861d2 | 153 | void SSD1306::copy_to_lcd(void) |

| charly | 36:668396f861d2 | 154 | { |

| charly | 36:668396f861d2 | 155 | |

| charly | 36:668396f861d2 | 156 | for(int page=0; page<8 /*_LCDPAGES */; page++) |

| charly | 36:668396f861d2 | 157 | { |

| charly | 36:668396f861d2 | 158 | wr_cmd8(0x02); // set column low nibble |

| charly | 36:668396f861d2 | 159 | wr_cmd8(0x10); // set column hi nibble |

| charly | 36:668396f861d2 | 160 | wr_cmd8(0xB0+page); // set page |

| charly | 36:668396f861d2 | 161 | wr_grambuf(buffer16+(page*screensize_X>>1), /*screensize_X*/ 128>>1); // send whole page pixels as shorts(16bit) not bytes! |

| charly | 36:668396f861d2 | 162 | } |

| charly | 36:668396f861d2 | 163 | } |

| charly | 36:668396f861d2 | 164 | |

| charly | 36:668396f861d2 | 165 | void SSD1306::cls(void) |

| charly | 36:668396f861d2 | 166 | { |

| charly | 36:668396f861d2 | 167 | unsigned short tmp = _background^0xFFFF; |

| charly | 36:668396f861d2 | 168 | //memset(buffer,tmp,/*screensize_X*_LCDPAGES*/ 128*64/8); // clear display buffer |

| charly | 36:668396f861d2 | 169 | memset(buffer,0x00,screensize_X*(screensize_Y>>3)); // clear display buffer |

| charly | 36:668396f861d2 | 170 | copy_to_lcd(); |

| charly | 36:668396f861d2 | 171 | } |

| charly | 36:668396f861d2 | 172 | |

| dreschpe | 12:9c8f3076347c | 173 | void SSD1306::mirrorXY(mirror_t mode) |

| dreschpe | 12:9c8f3076347c | 174 | { |

| dreschpe | 12:9c8f3076347c | 175 | switch (mode) |

| dreschpe | 12:9c8f3076347c | 176 | { |

| dreschpe | 12:9c8f3076347c | 177 | case(NONE): |

| dreschpe | 12:9c8f3076347c | 178 | wr_cmd16(0xA0C0); |

| dreschpe | 12:9c8f3076347c | 179 | break; |

| dreschpe | 12:9c8f3076347c | 180 | case(X): |

| dreschpe | 12:9c8f3076347c | 181 | wr_cmd16(0xA1C0); |

| dreschpe | 12:9c8f3076347c | 182 | break; |

| dreschpe | 12:9c8f3076347c | 183 | case(Y): |

| dreschpe | 12:9c8f3076347c | 184 | wr_cmd16(0xA0C8); |

| dreschpe | 12:9c8f3076347c | 185 | break; |

| dreschpe | 12:9c8f3076347c | 186 | case(XY): |

| dreschpe | 12:9c8f3076347c | 187 | wr_cmd16(0xA1C8); |

| dreschpe | 12:9c8f3076347c | 188 | break; |

| dreschpe | 12:9c8f3076347c | 189 | } |

| dreschpe | 12:9c8f3076347c | 190 | } |

| dreschpe | 12:9c8f3076347c | 191 | |

| dreschpe | 12:9c8f3076347c | 192 | void SSD1306::set_contrast(int o) |

| dreschpe | 12:9c8f3076347c | 193 | { |

| dreschpe | 12:9c8f3076347c | 194 | contrast = o; |

| dreschpe | 12:9c8f3076347c | 195 | |

| Geremia | 15:b9483ba842c8 | 196 | wr_cmd16(0x8100|(o&0xFF)); |

| dreschpe | 12:9c8f3076347c | 197 | } |

| dreschpe | 17:1dafb896c6f5 | 198 | |

| charly | 36:668396f861d2 | 199 | void SSD1306::pixel(int x, int y, unsigned short color) |

| charly | 36:668396f861d2 | 200 | { |

| charly | 36:668396f861d2 | 201 | // first check parameter |

| charly | 36:668396f861d2 | 202 | if((x >= screensize_X) || (y >= screensize_Y) || (x<0) || (y<0)) return; |

| charly | 36:668396f861d2 | 203 | |

| charly | 36:668396f861d2 | 204 | //Buffer[(Xpoint + (Ypoint / 8) * sOLED_DIS.OLED_Dis_Column)] |= 1 << (Ypoint % 8); |

| charly | 36:668396f861d2 | 205 | //Buffer[(Xpoint + (Ypoint / 8) * sOLED_DIS.OLED_Dis_Column)] |= 0 << (Ypoint % 8); |

| charly | 36:668396f861d2 | 206 | if (color) {buffer[x+((y>>3)*screensize_X)] |= 0 << (y % 8);} |

| charly | 36:668396f861d2 | 207 | else {buffer[x+((y>>3)*screensize_X)] |= 1 << (y % 8);} |

| charly | 36:668396f861d2 | 208 | |

| charly | 36:668396f861d2 | 209 | |

| charly | 36:668396f861d2 | 210 | } |

| dreschpe | 17:1dafb896c6f5 | 211 | |

| dreschpe | 17:1dafb896c6f5 | 212 | |

| dreschpe | 17:1dafb896c6f5 | 213 | const uint8_t scroll_speed[8]={3,2,1,6,0,5,4,7}; |

| dreschpe | 17:1dafb896c6f5 | 214 | |

| dreschpe | 17:1dafb896c6f5 | 215 | //////////////////////////////////////////////////////////////////// |

| dreschpe | 17:1dafb896c6f5 | 216 | // functions addon to LCD.cpp |

| dreschpe | 17:1dafb896c6f5 | 217 | //////////////////////////////////////////////////////////////////// |

| dreschpe | 17:1dafb896c6f5 | 218 | void SSD1306::horizontal_scroll(int l_r,int s_page,int e_page,int speed){ |

| dreschpe | 17:1dafb896c6f5 | 219 | wr_cmd8(0x2E); // deactivate scroll before change |

| dreschpe | 17:1dafb896c6f5 | 220 | if(l_r == 1){ |

| dreschpe | 17:1dafb896c6f5 | 221 | wr_cmd16(0x2700); // horizontal scroll left |

| dreschpe | 17:1dafb896c6f5 | 222 | } |

| dreschpe | 17:1dafb896c6f5 | 223 | else { |

| dreschpe | 17:1dafb896c6f5 | 224 | wr_cmd16(0x2600); |

| dreschpe | 17:1dafb896c6f5 | 225 | } |

| dreschpe | 17:1dafb896c6f5 | 226 | wr_cmd16((s_page & 0x07)<<8 | (scroll_speed[speed & 0x07])); |

| dreschpe | 17:1dafb896c6f5 | 227 | wr_cmd16((e_page & 0x07)<<8 ); |

| dreschpe | 17:1dafb896c6f5 | 228 | wr_cmd16(0xFF2F); |

| dreschpe | 17:1dafb896c6f5 | 229 | } |

| dreschpe | 17:1dafb896c6f5 | 230 | |

| dreschpe | 17:1dafb896c6f5 | 231 | void SSD1306::horiz_vert_scroll(int l_r,int s_page,int e_page,int v_off,int speed){ |

| dreschpe | 17:1dafb896c6f5 | 232 | wr_cmd8(0x2E); // deactivate scroll before change |

| dreschpe | 17:1dafb896c6f5 | 233 | if(l_r == 1){ |

| dreschpe | 17:1dafb896c6f5 | 234 | wr_cmd16(0x2A00); // horizontal scroll left |

| dreschpe | 17:1dafb896c6f5 | 235 | } |

| dreschpe | 17:1dafb896c6f5 | 236 | else { |

| dreschpe | 17:1dafb896c6f5 | 237 | wr_cmd16(0x2900); |

| dreschpe | 17:1dafb896c6f5 | 238 | } |

| dreschpe | 17:1dafb896c6f5 | 239 | wr_cmd16((s_page & 0x07)<<8 | (scroll_speed[speed & 0x07])); |

| dreschpe | 17:1dafb896c6f5 | 240 | wr_cmd16((e_page & 0x07)<<8 | (v_off & 0x3F) ); |

| dreschpe | 17:1dafb896c6f5 | 241 | wr_cmd8(0x2F); |

| dreschpe | 17:1dafb896c6f5 | 242 | |

| dreschpe | 17:1dafb896c6f5 | 243 | } |

| dreschpe | 17:1dafb896c6f5 | 244 | |

| dreschpe | 17:1dafb896c6f5 | 245 | void SSD1306::end_scroll(){ |

| dreschpe | 17:1dafb896c6f5 | 246 | wr_cmd8(0x2E); |

| dreschpe | 17:1dafb896c6f5 | 247 | } |