demo sample to drive PCU9955 and PCA9629

Dependencies: mbed I2C_slaves PCU9669 parallel_bus

Fork of mini_board_PCU9669 by

What is this?

This is a sample code to operate PCU9955 (16ch constant-current LED controller) and PCA9629 (intelligent stepper motor controller) through PCU9669 (3 channels (UltraFast mode * 2ch, FastModePlus *1ch) I2C bus controller).

This demo is written based on mini_board_PCU9669 sample code library and its API.

http://mbed.org/users/nxp_ip/code/mini_board_PCU9669/

Demo will shows how the LED controllers and stepper motor controllers works.

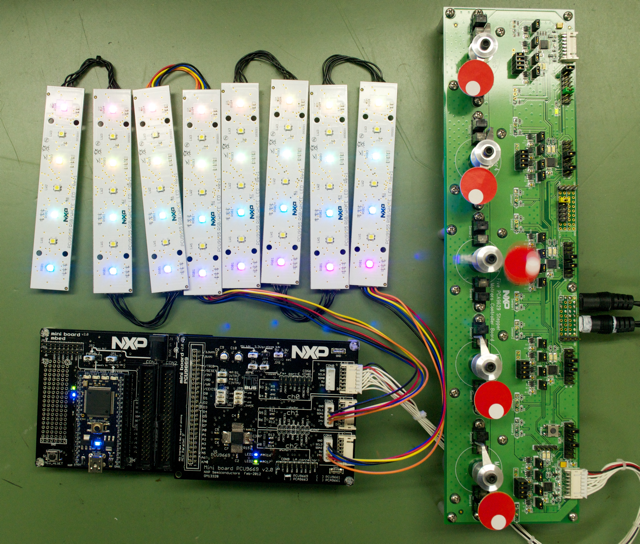

It uses a mini_board_PCU9669 board with mbed, 8 of PCU9955s and 5 PCA9629s.

Demo setup

(left-top: PCU9955 boards, left-bottom: mini-board PCU9669 with mbed, right: PCA9629 x5 board)

Board connections and device addresses

Reference:

User manual of PCU9669 demo board: Mini board PCU9669

http://www.nxp.com/documents/user_manual/UM10580.pdf

sample code : mbed programs

Import programmini_board_PCU9669

mini board PCU9669 (and PCA9665) sample code

Import programPCA9955_Hello

PCA9955 16 channel current drive(sink) LED driver sample code

Import programPCA9955_simple

very simple sample code for PCA9955 (16 channel current control LED driver)

Import programPCA9629_Hello

Sample code for PCA9629 operation

device infomation

PCU9669 (Parallel bus to 1 channel Fm+ and 2 channel UFm I2C-bus controller)

PCU9955 (16-channel UFm I²C-bus 57 mA constant current LED driver)

PCA9955 (16-channel Fm+ I²C-bus 57 mA constant current LED driver)

PCU9629 (Fm+ I2C-bus stepper motor controller)

main_PCU9669.c@2:401c24301f60, 2012-03-21 (annotated)

- Committer:

- nxp_ip

- Date:

- Wed Mar 21 02:18:02 2012 +0000

- Revision:

- 2:401c24301f60

- Parent:

- 1:709e2c8e789a

- Child:

- 4:c50d5596cb47

9669 without 9629

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| nxp_ip | 0:de9a15767563 | 1 | /** A sample code for "mini board PCU9669/PCA9665" |

| nxp_ip | 0:de9a15767563 | 2 | * |

| nxp_ip | 0:de9a15767563 | 3 | * @author Tedd OKANO, NXP Semiconductors |

| nxp_ip | 0:de9a15767563 | 4 | * @version 0.9 |

| nxp_ip | 0:de9a15767563 | 5 | * @date 14-Feb-2011 |

| nxp_ip | 0:de9a15767563 | 6 | * |

| nxp_ip | 0:de9a15767563 | 7 | * Released under the MIT License: http://mbed.org/license/mit |

| nxp_ip | 0:de9a15767563 | 8 | * |

| nxp_ip | 0:de9a15767563 | 9 | * An operation sample of PCU9669/PCA9665 I2C bus controller. |

| nxp_ip | 0:de9a15767563 | 10 | * The mbed accesses the bus controller's parallel port (8/2 bit address and 8 bit data) by bit-banging. |

| nxp_ip | 0:de9a15767563 | 11 | * The bit-banging is poerformed by PortInOut function of mbed library. |

| nxp_ip | 0:de9a15767563 | 12 | * |

| nxp_ip | 0:de9a15767563 | 13 | * To make the code porting easier, all codes are partitioned into layers to abstract other parts. |

| nxp_ip | 0:de9a15767563 | 14 | * The mbed specific parts are concentrated in lowest layer: "hardware_abs.*". |

| nxp_ip | 0:de9a15767563 | 15 | * This module may need to be modified for the porting. |

| nxp_ip | 0:de9a15767563 | 16 | * |

| nxp_ip | 0:de9a15767563 | 17 | * All other upper layers are writen in standard-C. |

| nxp_ip | 0:de9a15767563 | 18 | * |

| nxp_ip | 0:de9a15767563 | 19 | * base code is written from 05-Sep-2011 to 09-Sep-2011. |

| nxp_ip | 0:de9a15767563 | 20 | * And demo code has been build on 11-Sep-2011. |

| nxp_ip | 0:de9a15767563 | 21 | * Debug and code adjustment has been done on 08-Sep-2011. |

| nxp_ip | 0:de9a15767563 | 22 | * Small sanitization for main.cpp. All mbed related codes are moved in to "hardware_abs.*". 13-Oct-2011 |

| nxp_ip | 0:de9a15767563 | 23 | * hardware_abs are moved into parallel_bus library folder, 3 LED driver operation sample 13-Feb.-2012 |

| nxp_ip | 0:de9a15767563 | 24 | * PCU9669 and PCA9665 codes are packed in a project 14-Feb-2012. |

| nxp_ip | 0:de9a15767563 | 25 | * |

| nxp_ip | 0:de9a15767563 | 26 | * Before builidng the code, please edit the file mini_board_PCU9669/config.h |

| nxp_ip | 0:de9a15767563 | 27 | * Uncomment the target name what you want to target. |

| nxp_ip | 0:de9a15767563 | 28 | */ |

| nxp_ip | 0:de9a15767563 | 29 | |

| nxp_ip | 0:de9a15767563 | 30 | /** @note Application layer module of PCU9669 |

| nxp_ip | 0:de9a15767563 | 31 | * |

| nxp_ip | 0:de9a15767563 | 32 | * This code is made to explain basic PCU9669 operation. |

| nxp_ip | 0:de9a15767563 | 33 | * And also, it demonstrates 3 channels of I2C operation with several slaves on those buses. |

| nxp_ip | 0:de9a15767563 | 34 | * |

| nxp_ip | 0:de9a15767563 | 35 | * The ch0 is an Fm+ bus that has a PCA9955 as slave device |

| nxp_ip | 0:de9a15767563 | 36 | * The ch1 and ch2 are UFm buses. Each bus has a PCU9955 as slave devices. |

| nxp_ip | 0:de9a15767563 | 37 | */ |

| nxp_ip | 0:de9a15767563 | 38 | |

| nxp_ip | 0:de9a15767563 | 39 | #include "config.h" |

| nxp_ip | 0:de9a15767563 | 40 | |

| nxp_ip | 0:de9a15767563 | 41 | #include "transfer_manager.h" // abstracting the access of PCU9669 internal buffer |

| nxp_ip | 0:de9a15767563 | 42 | #include "PCU9669_access.h" // PCU9669 chip access interface |

| nxp_ip | 0:de9a15767563 | 43 | #include "hardware_abs.h" // to use install_ISR() and wait_sec() functions |

| nxp_ip | 0:de9a15767563 | 44 | #include "PCx9955_reg.h" // slave specific definitions |

| nxp_ip | 0:de9a15767563 | 45 | #include "PCA9629_reg.h" |

| nxp_ip | 0:de9a15767563 | 46 | #include "utility.h" // |

| nxp_ip | 0:de9a15767563 | 47 | //#include "mbed.h" // this header is required only when printf() is used. |

| nxp_ip | 0:de9a15767563 | 48 | |

| nxp_ip | 0:de9a15767563 | 49 | #if defined( CODE_FOR_PCU9669 ) || defined( CODE_FOR_PCA9663 ) |

| nxp_ip | 0:de9a15767563 | 50 | |

| nxp_ip | 0:de9a15767563 | 51 | #ifdef CODE_FOR_PCU9669 |

| nxp_ip | 0:de9a15767563 | 52 | #define TARGET_CHIP_ID PCU9669_ID |

| nxp_ip | 0:de9a15767563 | 53 | #endif |

| nxp_ip | 0:de9a15767563 | 54 | |

| nxp_ip | 0:de9a15767563 | 55 | #ifdef CODE_FOR_PCA9663 |

| nxp_ip | 0:de9a15767563 | 56 | #define TARGET_CHIP_ID PCA9663_ID |

| nxp_ip | 0:de9a15767563 | 57 | #endif |

| nxp_ip | 0:de9a15767563 | 58 | |

| nxp_ip | 0:de9a15767563 | 59 | /** |

| nxp_ip | 0:de9a15767563 | 60 | * register settings for PCx9955 |

| nxp_ip | 0:de9a15767563 | 61 | */ |

| nxp_ip | 0:de9a15767563 | 62 | |

| nxp_ip | 0:de9a15767563 | 63 | char PCx9955_reg_data[] = { |

| nxp_ip | 0:de9a15767563 | 64 | 0x80, // Strat register address with AutoIncrement bit |

| nxp_ip | 0:de9a15767563 | 65 | 0x00, 0x05, // MODE1, MODE2 |

| nxp_ip | 0:de9a15767563 | 66 | 0xAA, 0xAA, 0xAA, 0xAA, // LEDOUT[3:0] |

| nxp_ip | 0:de9a15767563 | 67 | 0x80, 0x00, // GRPPWM, GRPFREQ |

| nxp_ip | 0:de9a15767563 | 68 | PWM_INIT, PWM_INIT, PWM_INIT, PWM_INIT, // PWM[3:0] |

| nxp_ip | 0:de9a15767563 | 69 | PWM_INIT, PWM_INIT, PWM_INIT, PWM_INIT, // PWM[7:4] |

| nxp_ip | 0:de9a15767563 | 70 | PWM_INIT, PWM_INIT, PWM_INIT, PWM_INIT, // PWM[11:8] |

| nxp_ip | 0:de9a15767563 | 71 | PWM_INIT, PWM_INIT, PWM_INIT, PWM_INIT, // PWM[15:12] |

| nxp_ip | 0:de9a15767563 | 72 | IREF_INIT, IREF_INIT, IREF_INIT, IREF_INIT, // IREF[3:0] |

| nxp_ip | 0:de9a15767563 | 73 | IREF_INIT, IREF_INIT, IREF_INIT, IREF_INIT, // IREF[7:4] |

| nxp_ip | 0:de9a15767563 | 74 | IREF_INIT, IREF_INIT, IREF_INIT, IREF_INIT, // IREF[11:8] |

| nxp_ip | 0:de9a15767563 | 75 | IREF_INIT, IREF_INIT, IREF_INIT, IREF_INIT, // IREF[15:12] |

| nxp_ip | 0:de9a15767563 | 76 | 0x08 // OFFSET: 1uS offsets |

| nxp_ip | 0:de9a15767563 | 77 | }; |

| nxp_ip | 0:de9a15767563 | 78 | |

| nxp_ip | 0:de9a15767563 | 79 | char PCx9629_reg_data[] = { // This sample data performs ramp-up/down with rotation=2 in 1 second |

| nxp_ip | 0:de9a15767563 | 80 | 0x80, // Strat register address with AutoIncrement bit |

| nxp_ip | 0:de9a15767563 | 81 | 0x20, 0xE2, 0xE4, 0xE6, 0xE0, 0xFF, 0x10, // for registers MODE - WDCNTL (0x00 - 0x06 |

| nxp_ip | 0:de9a15767563 | 82 | 0x00, 0x00, // for registers IP and INTSTAT (0x07, 0x08) |

| nxp_ip | 0:de9a15767563 | 83 | 0x0F, 0x03, 0x0C, 0x0F, 0x03, 0x00, 0x03, 0x03, 0x01, // for registers OP - INT_AUTO_CLR (0x09 - 0x11) |

| nxp_ip | 0:de9a15767563 | 84 | 0x03, 0x00, 0x30, 0x00, 0x1D, 0x07, 0x1D, 0x07, // for registers SETMODE - CCWPWH (0x12 - 0x19) |

| nxp_ip | 0:de9a15767563 | 85 | 0x2F, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, // for registers CWSCOUNTL - CCWRCOUNTH (0x1A - 0x21) |

| nxp_ip | 0:de9a15767563 | 86 | 0x08, 0x08, // for registers EXTRASTEPS0 and EXTRASTEPS1 (0x22, 0x23) |

| nxp_ip | 0:de9a15767563 | 87 | 0x38, 0x00, 0x80 // for registers RMPCNTL - MCNTL (0x24 - 0x26) |

| nxp_ip | 0:de9a15767563 | 88 | }; |

| nxp_ip | 0:de9a15767563 | 89 | |

| nxp_ip | 0:de9a15767563 | 90 | |

| nxp_ip | 0:de9a15767563 | 91 | char PCx9955_reg_read_start_address = 0x80; |

| nxp_ip | 0:de9a15767563 | 92 | |

| nxp_ip | 1:709e2c8e789a | 93 | char read_buffer[ 41 ]; |

| nxp_ip | 0:de9a15767563 | 94 | |

| nxp_ip | 0:de9a15767563 | 95 | transaction ufm_transactions[] = { |

| nxp_ip | 0:de9a15767563 | 96 | { PCx9955_ADDR0, PCx9955_reg_data, sizeof( PCx9955_reg_data ) } |

| nxp_ip | 0:de9a15767563 | 97 | }; |

| nxp_ip | 0:de9a15767563 | 98 | |

| nxp_ip | 0:de9a15767563 | 99 | transaction fm_plus_transactions[] = { |

| nxp_ip | 0:de9a15767563 | 100 | { PCx9955_ADDR0, PCx9955_reg_data, sizeof( PCx9955_reg_data ) }, |

| nxp_ip | 2:401c24301f60 | 101 | { PCx9955_ADDR0, &PCx9955_reg_read_start_address, 1 }, |

| nxp_ip | 2:401c24301f60 | 102 | { PCx9955_ADDR0 | 0x01, read_buffer, sizeof( read_buffer ) } |

| nxp_ip | 1:709e2c8e789a | 103 | // { 0x4A, PCx9629_reg_data, sizeof( PCx9629_reg_data ) } |

| nxp_ip | 0:de9a15767563 | 104 | }; |

| nxp_ip | 0:de9a15767563 | 105 | |

| nxp_ip | 0:de9a15767563 | 106 | char read_done = 0; |

| nxp_ip | 0:de9a15767563 | 107 | |

| nxp_ip | 0:de9a15767563 | 108 | void interrupt_handler( void ); |

| nxp_ip | 0:de9a15767563 | 109 | |

| nxp_ip | 0:de9a15767563 | 110 | int main() { |

| nxp_ip | 0:de9a15767563 | 111 | char clear[ 16 ] = { 0 }; |

| nxp_ip | 0:de9a15767563 | 112 | int count = 0; |

| nxp_ip | 0:de9a15767563 | 113 | int i; |

| nxp_ip | 0:de9a15767563 | 114 | int j; |

| nxp_ip | 0:de9a15767563 | 115 | |

| nxp_ip | 0:de9a15767563 | 116 | // printf( "\r\nPCU9669 simple demo program on mbed\r\n build : %s (UTC), %s \r\n\r\n", __TIME__, __DATE__ ); |

| nxp_ip | 0:de9a15767563 | 117 | |

| nxp_ip | 0:de9a15767563 | 118 | hardware_initialize(); // initializing bit-banging parallel port |

| nxp_ip | 0:de9a15767563 | 119 | reset(); // assert hardware /RESET sgnal |

| nxp_ip | 0:de9a15767563 | 120 | |

| nxp_ip | 0:de9a15767563 | 121 | if ( start_bus_controller( TARGET_CHIP_ID ) ) // wait the bus controller ready and check chip ID |

| nxp_ip | 0:de9a15767563 | 122 | return 1; |

| nxp_ip | 0:de9a15767563 | 123 | |

| nxp_ip | 0:de9a15767563 | 124 | write_ch_register( CH_FM_PLUS, INTMSK, 0x30 ); // set bus controller to ignore NAK return from Fm+ slaves |

| nxp_ip | 0:de9a15767563 | 125 | install_ISR( &interrupt_handler ); // interrupt service routine install |

| nxp_ip | 0:de9a15767563 | 126 | |

| nxp_ip | 0:de9a15767563 | 127 | setup_transfer( CH_FM_PLUS, fm_plus_transactions, sizeof( fm_plus_transactions ) / sizeof( transaction ) ); |

| nxp_ip | 0:de9a15767563 | 128 | setup_transfer( CH_UFM1, ufm_transactions, sizeof( ufm_transactions ) / sizeof( transaction ) ); |

| nxp_ip | 0:de9a15767563 | 129 | setup_transfer( CH_UFM2, ufm_transactions, sizeof( ufm_transactions ) / sizeof( transaction ) ); |

| nxp_ip | 0:de9a15767563 | 130 | |

| nxp_ip | 0:de9a15767563 | 131 | while ( 1 ) { |

| nxp_ip | 0:de9a15767563 | 132 | for ( i = 0; i < 16; i++ ) { |

| nxp_ip | 0:de9a15767563 | 133 | for ( j = 0; j < 256; j += 4 ) { |

| nxp_ip | 0:de9a15767563 | 134 | buffer_overwrite( CH_FM_PLUS, 0, 9 + i, (char *)&j, 1 ); |

| nxp_ip | 0:de9a15767563 | 135 | buffer_overwrite( CH_UFM1, 0, 9 + i, (char *)&j, 1 ); |

| nxp_ip | 0:de9a15767563 | 136 | buffer_overwrite( CH_UFM2, 0, 9 + i, (char *)&j, 1 ); |

| nxp_ip | 0:de9a15767563 | 137 | |

| nxp_ip | 0:de9a15767563 | 138 | read_done = 0; |

| nxp_ip | 0:de9a15767563 | 139 | |

| nxp_ip | 0:de9a15767563 | 140 | set_n_of_transaction( CH_FM_PLUS, (sizeof( fm_plus_transactions ) / sizeof( transaction )) - ((count % 256) ? 1 : 0) ); |

| nxp_ip | 0:de9a15767563 | 141 | |

| nxp_ip | 0:de9a15767563 | 142 | start( CH_FM_PLUS ); |

| nxp_ip | 0:de9a15767563 | 143 | start( CH_UFM1 ); |

| nxp_ip | 0:de9a15767563 | 144 | start( CH_UFM2 ); |

| nxp_ip | 0:de9a15767563 | 145 | |

| nxp_ip | 0:de9a15767563 | 146 | #if 0 |

| nxp_ip | 0:de9a15767563 | 147 | if ( read_done ) { |

| nxp_ip | 0:de9a15767563 | 148 | buffer_read( CH_FM_PLUS, 2, 0, read_buffer, sizeof( read_buffer ) ); |

| nxp_ip | 0:de9a15767563 | 149 | dump_read_data( read_buffer, sizeof( read_buffer ) ); |

| nxp_ip | 0:de9a15767563 | 150 | read_done = 0; |

| nxp_ip | 0:de9a15767563 | 151 | } |

| nxp_ip | 0:de9a15767563 | 152 | #endif |

| nxp_ip | 0:de9a15767563 | 153 | wait_sec( 0.01 ); |

| nxp_ip | 0:de9a15767563 | 154 | count++; |

| nxp_ip | 0:de9a15767563 | 155 | } |

| nxp_ip | 0:de9a15767563 | 156 | } |

| nxp_ip | 0:de9a15767563 | 157 | buffer_overwrite( CH_FM_PLUS, 0, 9, clear, 16 ); |

| nxp_ip | 0:de9a15767563 | 158 | buffer_overwrite( CH_UFM1, 0, 9, clear, 16 ); |

| nxp_ip | 0:de9a15767563 | 159 | buffer_overwrite( CH_UFM2, 0, 9, clear, 16 ); |

| nxp_ip | 0:de9a15767563 | 160 | } |

| nxp_ip | 0:de9a15767563 | 161 | } |

| nxp_ip | 0:de9a15767563 | 162 | |

| nxp_ip | 0:de9a15767563 | 163 | void interrupt_handler( void ) { |

| nxp_ip | 0:de9a15767563 | 164 | char global_status; |

| nxp_ip | 0:de9a15767563 | 165 | char channel_status; |

| nxp_ip | 0:de9a15767563 | 166 | |

| nxp_ip | 0:de9a15767563 | 167 | global_status = read_data( CTRLSTATUS ); |

| nxp_ip | 0:de9a15767563 | 168 | |

| nxp_ip | 0:de9a15767563 | 169 | if ( global_status & 0x01 ) { // ch0 |

| nxp_ip | 0:de9a15767563 | 170 | channel_status = read_ch_register( 0, CHSTATUS ); |

| nxp_ip | 0:de9a15767563 | 171 | |

| nxp_ip | 0:de9a15767563 | 172 | if ( channel_status & 0x80 ) |

| nxp_ip | 0:de9a15767563 | 173 | read_done = 1; |

| nxp_ip | 0:de9a15767563 | 174 | } |

| nxp_ip | 0:de9a15767563 | 175 | if ( global_status & 0x02 ) { |

| nxp_ip | 0:de9a15767563 | 176 | channel_status = read_ch_register( 1, CHSTATUS ); |

| nxp_ip | 0:de9a15767563 | 177 | } |

| nxp_ip | 0:de9a15767563 | 178 | if ( global_status & 0x04 ) { |

| nxp_ip | 0:de9a15767563 | 179 | channel_status = read_ch_register( 2, CHSTATUS ); |

| nxp_ip | 0:de9a15767563 | 180 | } |

| nxp_ip | 0:de9a15767563 | 181 | // printf( "ISR channel_status 0x%02X\r\n", channel_status ); |

| nxp_ip | 0:de9a15767563 | 182 | } |

| nxp_ip | 0:de9a15767563 | 183 | |

| nxp_ip | 0:de9a15767563 | 184 | #endif // CODE_FOR_PCU9669 |

| nxp_ip | 0:de9a15767563 | 185 | |

| nxp_ip | 0:de9a15767563 | 186 | |

| nxp_ip | 0:de9a15767563 | 187 | |

| nxp_ip | 0:de9a15767563 | 188 | |

| nxp_ip | 0:de9a15767563 | 189 | |

| nxp_ip | 0:de9a15767563 | 190 |