This is Library using WIZnet Hardware TCP/IP chip, W5500 and WIZnet TCP/IP Offload Engine, W7500.

Dependents: HTTP_SDcard_file_server_WIZwiki-W7500 SSD1306_smart_watch TCPEchoServer-WIZwiki-W7500 httpServer-WIZwiki-W7500 ... more

Fork of WIZnetInterface by

This is WIZnet Ethernet Interface using Hardware TCP/IP chip, W5500 and TCP/IP Offload Engine, W7500.

[Users » embeddist » Code » WIZnetInterface](https://developer.mbed.org/users/embeddist/code/WIZnetInterface/) -> WIZnetInterface Lib will be released on [Team WIZnet](https://developer.mbed.org/teams/WIZnet/)

- WIZwiki_W7500 : /platforms/WIZwiki-W7500/

- WIZwiki_W7500P : /platforms/WIZwiki-W7500P/

- WIZwiki_W7500ECO : /platforms/WIZwiki-W7500ECO/

- W5500 Ethernet Shield : /components/W5500-Ethernet-Kit-for-IoT/

This library is an Ethernet Interface library port-based on [EthernetInterface](https://developer.mbed.org/users/mbed_official/code/EthernetInterface/docs/tip/).

For more detail, visit http://embeddist.blogspot.kr/2015/06/wiznetinterface-for-armmbed.html

Diff: arch/int/W7500x_toe.cpp

- Revision:

- 25:48abbe1d9bab

- Parent:

- 19:d8773cd4edc5

--- a/arch/int/W7500x_toe.cpp Wed Jul 01 04:02:50 2015 +0000 +++ b/arch/int/W7500x_toe.cpp Mon Oct 05 05:34:44 2015 +0000 @@ -15,7 +15,8 @@ * OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE SOFTWARE. */ #include "eth_arch.h" -#if defined(TARGET_WIZwiki_W7500) +#if defined(TARGET_WIZwiki_W7500) || defined(TARGET_WIZwiki_W7500P) + #include "mbed.h" #include "mbed_debug.h" @@ -29,6 +30,9 @@ * - input_MDIO(),output_MDIO(),turnaroud_MDIO(),idle_MDIO() * called by ethernet_link() and ethernet_set_link() */ + +#if defined TARGET_WIZwiki_W7500 + #define MDIO GPIO_Pin_14 #define MDC GPIO_Pin_15 #define GPIO_MDC GPIOB @@ -41,6 +45,24 @@ #define CNTL_AUTONEGO (0x01ul<<11) #define CNTL_SPEED (0x01ul<<12) #define MDC_WAIT (1) + +#elif TARGET_WIZwiki_W7500P + +#define MDIO GPIO_Pin_15 +#define MDC GPIO_Pin_14 +#define GPIO_MDC GPIOB +#define PHY_ADDR_IP101G 0x01 +#define PHY_ADDR PHY_ADDR_IP101G +#define SVAL 0x2 //right shift val = 2 +#define PHYREG_CONTROL 0x0 //Control Register address (Contorl basic register) +#define PHYREG_STATUS 0x1 //Status Register address (Status basic register) +#define CNTL_DUPLEX (0x01ul<< 7) +#define CNTL_AUTONEGO (0x01ul<<11) +#define CNTL_SPEED (0x01ul<<12) +#define MDC_WAIT (1) + +#endif + void mdio_init(GPIO_TypeDef* GPIOx, uint16_t GPIO_Pin_MDC, uint16_t GPIO_Pin_MDIO); void mdio_write(GPIO_TypeDef* GPIOx, uint32_t PhyRegAddr, uint32_t val); uint32_t mdio_read(GPIO_TypeDef* GPIOx, uint32_t PhyRegAddr); @@ -151,12 +173,18 @@ reg_wr<uint8_t>(MR, MR_RST); // set PAD strengh and pull-up for TXD[3:0] and TXE #ifdef __DEF_USED_IC101AG__ //For using IC+101AG + +#if defined(TARGET_WIZwiki_W7500) + *(volatile uint32_t *)(0x41003068) = 0x64; //TXD0 *(volatile uint32_t *)(0x4100306C) = 0x64; //TXD1 *(volatile uint32_t *)(0x41003070) = 0x64; //TXD2 *(volatile uint32_t *)(0x41003074) = 0x64; //TXD3 *(volatile uint32_t *)(0x41003050) = 0x64; //TXE +#endif + #endif + // set ticker counter reg_wr<uint32_t>(TIC100US, (SystemCoreClock/10000)); // write MAC address inside the WZTOE MAC address register

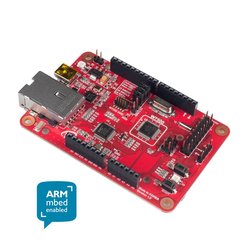

Network-Shield W5500

Network-Shield W5500

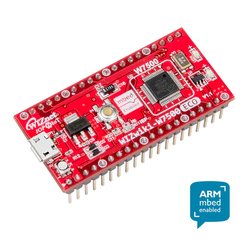

M0-Switch WIZnet W7500

M0-Switch WIZnet W7500

Serial-to-Ethernet Controller WIZ750SR

Serial-to-Ethernet Controller WIZ750SR