This is Library using WIZnet Hardware TCP/IP chip, W5500 and WIZnet TCP/IP Offload Engine, W7500.

Dependents: HTTP_SDcard_file_server_WIZwiki-W7500 SSD1306_smart_watch TCPEchoServer-WIZwiki-W7500 httpServer-WIZwiki-W7500 ... more

Fork of WIZnetInterface by

This is WIZnet Ethernet Interface using Hardware TCP/IP chip, W5500 and TCP/IP Offload Engine, W7500.

[Users » embeddist » Code » WIZnetInterface](https://developer.mbed.org/users/embeddist/code/WIZnetInterface/) -> WIZnetInterface Lib will be released on [Team WIZnet](https://developer.mbed.org/teams/WIZnet/)

- WIZwiki_W7500 : /platforms/WIZwiki-W7500/

- WIZwiki_W7500P : /platforms/WIZwiki-W7500P/

- WIZwiki_W7500ECO : /platforms/WIZwiki-W7500ECO/

- W5500 Ethernet Shield : /components/W5500-Ethernet-Kit-for-IoT/

This library is an Ethernet Interface library port-based on [EthernetInterface](https://developer.mbed.org/users/mbed_official/code/EthernetInterface/docs/tip/).

For more detail, visit http://embeddist.blogspot.kr/2015/06/wiznetinterface-for-armmbed.html

Diff: arch/ext/W5500.cpp

- Revision:

- 14:2101ab5ee40f

- Parent:

- 13:ec1c34e9ec45

- Child:

- 19:d8773cd4edc5

- Child:

- 26:d07c80e18b27

--- a/arch/ext/W5500.cpp Tue Jun 16 13:03:28 2015 +0900

+++ b/arch/ext/W5500.cpp Wed Jun 17 00:24:45 2015 +0000

@@ -155,23 +155,19 @@

void WIZnet_Chip::reset()

{

#if defined(USE_WIZ550IO_MAC)

+ //read the MAC address inside the module

+ reg_rd_mac(SHAR, mac);

+#endif

// hw reset

reset_pin = 1;

reset_pin = 0;

wait_us(500); // 500us (w5500)

reset_pin = 1;

wait_ms(400); // 400ms (w5500)

-

- reg_rd_mac(SHAR, mac); // read the MAC address inside the modulea

-#else

- // hw reset

- reg_wr(MR, 0x80);

- wait_us(500); // 500us (w5500)

-#endif

-

+#if defined(USE_WIZ550IO_MAC)

// write MAC address inside the WZTOE MAC address register

reg_wr_mac(SHAR, mac);

-

+#endif

// set RX and TX buffer size

#if 0

for (int socket = 0; socket < MAX_SOCK_NUM; socket++) {

@@ -378,7 +374,7 @@

}

cs = 1;

-#if DBG_SPI

+#if DBG_SPI

debug("[SPI]W %04x(%02x %d)", addr, cb, len);

for(int i = 0; i < len; i++) {

debug(" %02x", buf[i]);

@@ -471,23 +467,54 @@

debug("\n");

}

-int ethernet_link(void) {

-

- return ((uint8_t)(WIZnet_Chip::getPHYCFGR())& 0x01);

+int WIZnet_Chip::ethernet_link(void) {

+ int val = getPHYCFGR();

+ return (val&0x01);

}

-void ethernet_set_link(int speed, int duplex) {

+void WIZnet_Chip::ethernet_set_link(int speed, int duplex) {

uint32_t val=0;

if((speed < 0) || (speed > 1)) {

val = (PHYCFGR_OPMDC_ALLA)<<3;

} else {

val = (((speed&0x01)<<1)+ (duplex&0x01))<<3;

}

- WIZnet_Chip::setPHYCFGR((uint8_t)(PHYCFGR_RST&(PHYCFGR_OPMD|val)));

+ setPHYCFGR((uint8_t)(PHYCFGR_RST&(PHYCFGR_OPMD|val)));

wait(0.2);

- WIZnet_Chip::setPHYCFGR((uint8_t)((~PHYCFGR_RST)|(PHYCFGR_OPMD|val)));

+ setPHYCFGR((uint8_t)((~PHYCFGR_RST)|(PHYCFGR_OPMD|val)));

wait(0.2);

}

+ void WIZnet_Chip::reg_rd_mac(uint16_t addr, uint8_t* data) {

+ spi_read(addr, 0x00, data, 6);

+ }

+

+ void WIZnet_Chip::reg_wr_ip(uint16_t addr, uint8_t cb, const char* ip) {

+ uint8_t buf[4];

+ char* p = (char*)ip;

+ for(int i = 0; i < 4; i++) {

+ buf[i] = atoi(p);

+ p = strchr(p, '.');

+ if (p == NULL) {

+ break;

+ }

+ p++;

+ }

+ spi_write(addr, cb, buf, sizeof(buf));

+ }

+

+ void WIZnet_Chip::sreg_ip(int socket, uint16_t addr, const char* ip) {

+ reg_wr_ip(addr, (0x0C + (socket << 5)), ip);

+ }

+

+ void WIZnet_Chip::reg_rd_ip_byte(uint16_t addr, uint8_t* data) {

+ spi_read(addr, 0x00, data, 4);

+ }

+

+ void WIZnet_Chip::reg_wr_ip_byte(uint16_t addr, uint8_t* data) {

+ spi_write(addr, 0x04, data, 4);

+ }

+

+

#endif

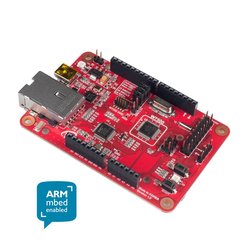

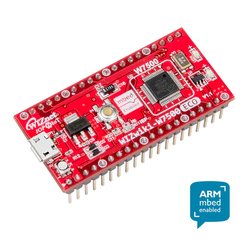

Network-Shield W5500

Network-Shield W5500

M0-Switch WIZnet W7500

M0-Switch WIZnet W7500

Serial-to-Ethernet Controller WIZ750SR

Serial-to-Ethernet Controller WIZ750SR