Lcd companion boards support (VKLCD50RTA & VKLCD70RT)

What is this ?

This is a demo program using Renesas RGA library & USB Camera to demonstrate VK-RZ/A1H's companion boards workability.

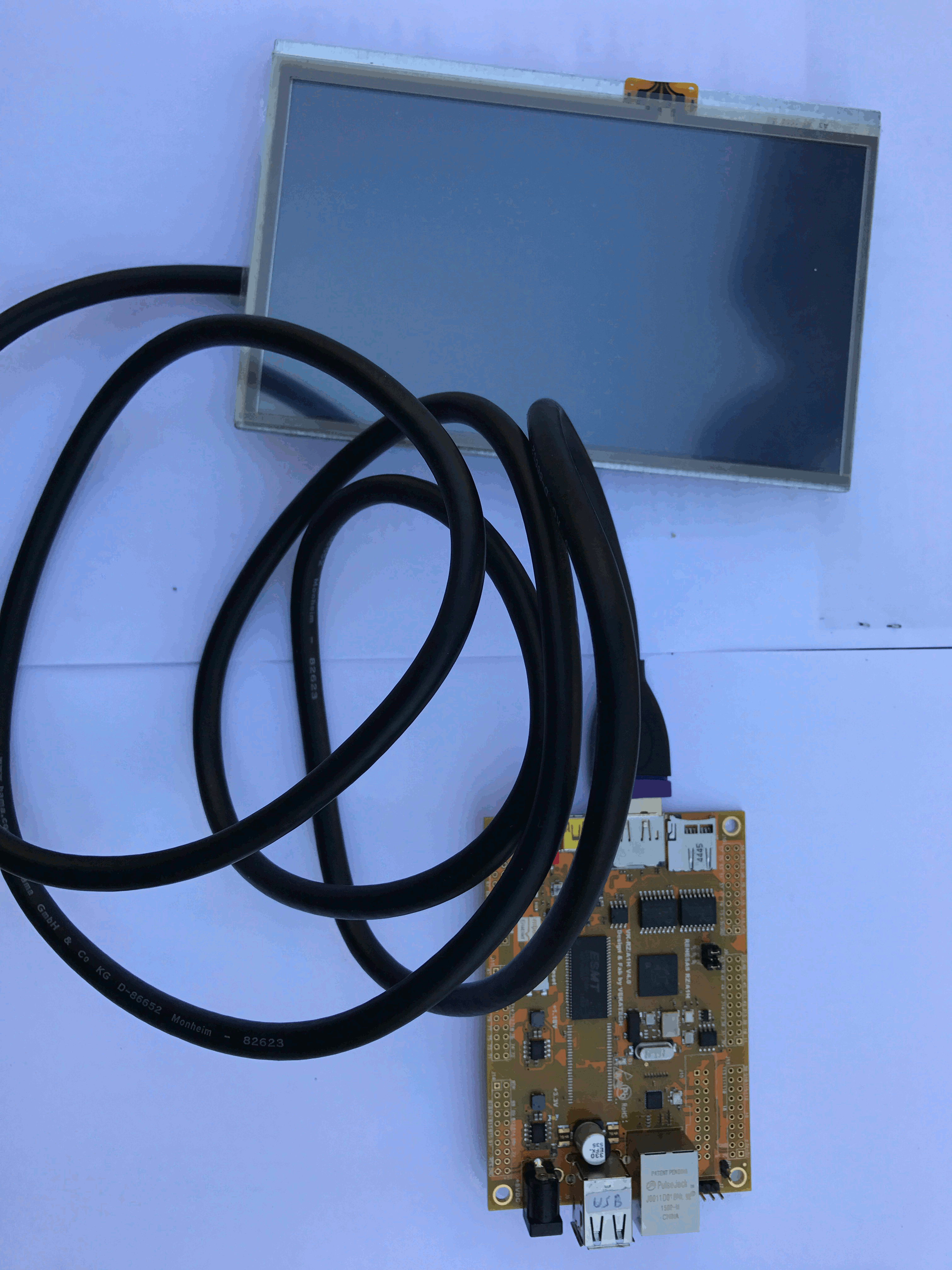

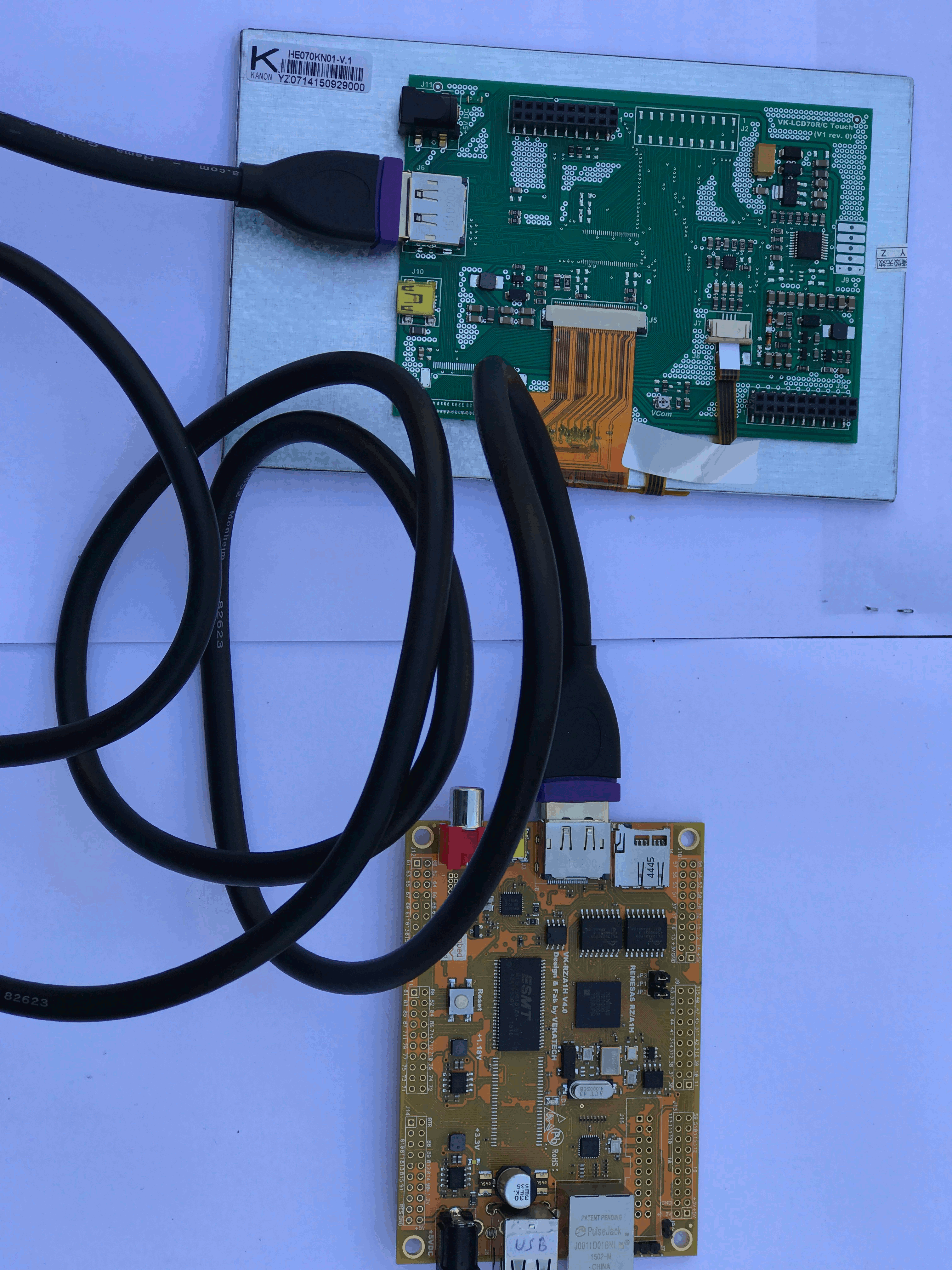

Supported companion Boards:

VKLCD50RTA

VKLCD70RT

How to Configure ?

You can choose which display is installed by altering the lcd_panel.h file

Leave the active one & comment out the others:

#define LCD_VDC5_CH0_PANEL LCD_CH0_PANEL_VKLCD50RTA //#define LCD_VDC5_CH0_PANEL LCD_CH0_PANEL_VKLCD70RT

You can alter the whole demo with your pictures if you like:

How to compile ?

- The Demo can be compiled in 3 modes:

- I. Execution from the internal 10-MB on-chip SRAM.

- II. Execution from the on-board serial FALSH in dual (32-MB) mode.

- After import in the online compiler just leave only the VKRZA1H_DOUBLE.sct & delete all others linker files in the TOOLCHAIN_ARM_STD folder.

- Drag & drop the result binary in MBED disk, (previously inited in double flash mode)

- III. Execution from the on-board serial FALSH in single (16-MB) mode.

- After import in the online compiler just leave only the VKRZA1H_SINGLE.sct & delete all others linker files in the TOOLCHAIN_ARM_STD folder.

- Drag & drop the result binary in MBED disk, (previously inited in single flash mode )

Quick presentation:

Other demos ?

More demos you can find on our FTP

hal/common/SPI.cpp@0:6435b67ad23c, 2017-02-16 (annotated)

- Committer:

- tvendov

- Date:

- Thu Feb 16 10:23:48 2017 +0000

- Revision:

- 0:6435b67ad23c

Initial lcd support (VKLCD50RTA & VKLCD70RT companion boards)

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| tvendov | 0:6435b67ad23c | 1 | /* mbed Microcontroller Library |

| tvendov | 0:6435b67ad23c | 2 | * Copyright (c) 2006-2013 ARM Limited |

| tvendov | 0:6435b67ad23c | 3 | * |

| tvendov | 0:6435b67ad23c | 4 | * Licensed under the Apache License, Version 2.0 (the "License"); |

| tvendov | 0:6435b67ad23c | 5 | * you may not use this file except in compliance with the License. |

| tvendov | 0:6435b67ad23c | 6 | * You may obtain a copy of the License at |

| tvendov | 0:6435b67ad23c | 7 | * |

| tvendov | 0:6435b67ad23c | 8 | * http://www.apache.org/licenses/LICENSE-2.0 |

| tvendov | 0:6435b67ad23c | 9 | * |

| tvendov | 0:6435b67ad23c | 10 | * Unless required by applicable law or agreed to in writing, software |

| tvendov | 0:6435b67ad23c | 11 | * distributed under the License is distributed on an "AS IS" BASIS, |

| tvendov | 0:6435b67ad23c | 12 | * WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied. |

| tvendov | 0:6435b67ad23c | 13 | * See the License for the specific language governing permissions and |

| tvendov | 0:6435b67ad23c | 14 | * limitations under the License. |

| tvendov | 0:6435b67ad23c | 15 | */ |

| tvendov | 0:6435b67ad23c | 16 | #include "SPI.h" |

| tvendov | 0:6435b67ad23c | 17 | #include "critical.h" |

| tvendov | 0:6435b67ad23c | 18 | |

| tvendov | 0:6435b67ad23c | 19 | #if DEVICE_SPI |

| tvendov | 0:6435b67ad23c | 20 | |

| tvendov | 0:6435b67ad23c | 21 | namespace mbed { |

| tvendov | 0:6435b67ad23c | 22 | |

| tvendov | 0:6435b67ad23c | 23 | #if DEVICE_SPI_ASYNCH && TRANSACTION_QUEUE_SIZE_SPI |

| tvendov | 0:6435b67ad23c | 24 | CircularBuffer<Transaction<SPI>, TRANSACTION_QUEUE_SIZE_SPI> SPI::_transaction_buffer; |

| tvendov | 0:6435b67ad23c | 25 | #endif |

| tvendov | 0:6435b67ad23c | 26 | |

| tvendov | 0:6435b67ad23c | 27 | SPI::SPI(PinName mosi, PinName miso, PinName sclk, PinName ssel) : |

| tvendov | 0:6435b67ad23c | 28 | _spi(), |

| tvendov | 0:6435b67ad23c | 29 | #if DEVICE_SPI_ASYNCH |

| tvendov | 0:6435b67ad23c | 30 | _irq(this), |

| tvendov | 0:6435b67ad23c | 31 | _usage(DMA_USAGE_NEVER), |

| tvendov | 0:6435b67ad23c | 32 | #endif |

| tvendov | 0:6435b67ad23c | 33 | _bits(8), |

| tvendov | 0:6435b67ad23c | 34 | _mode(0), |

| tvendov | 0:6435b67ad23c | 35 | _hz(1000000) { |

| tvendov | 0:6435b67ad23c | 36 | // No lock needed in the constructor |

| tvendov | 0:6435b67ad23c | 37 | |

| tvendov | 0:6435b67ad23c | 38 | spi_init(&_spi, mosi, miso, sclk, ssel); |

| tvendov | 0:6435b67ad23c | 39 | aquire(); |

| tvendov | 0:6435b67ad23c | 40 | } |

| tvendov | 0:6435b67ad23c | 41 | |

| tvendov | 0:6435b67ad23c | 42 | void SPI::format(int bits, int mode) { |

| tvendov | 0:6435b67ad23c | 43 | lock(); |

| tvendov | 0:6435b67ad23c | 44 | _bits = bits; |

| tvendov | 0:6435b67ad23c | 45 | _mode = mode; |

| tvendov | 0:6435b67ad23c | 46 | SPI::_owner = NULL; // Not that elegant, but works. rmeyer |

| tvendov | 0:6435b67ad23c | 47 | aquire(); |

| tvendov | 0:6435b67ad23c | 48 | unlock(); |

| tvendov | 0:6435b67ad23c | 49 | } |

| tvendov | 0:6435b67ad23c | 50 | |

| tvendov | 0:6435b67ad23c | 51 | void SPI::frequency(int hz) { |

| tvendov | 0:6435b67ad23c | 52 | lock(); |

| tvendov | 0:6435b67ad23c | 53 | _hz = hz; |

| tvendov | 0:6435b67ad23c | 54 | SPI::_owner = NULL; // Not that elegant, but works. rmeyer |

| tvendov | 0:6435b67ad23c | 55 | aquire(); |

| tvendov | 0:6435b67ad23c | 56 | unlock(); |

| tvendov | 0:6435b67ad23c | 57 | } |

| tvendov | 0:6435b67ad23c | 58 | |

| tvendov | 0:6435b67ad23c | 59 | SPI* SPI::_owner = NULL; |

| tvendov | 0:6435b67ad23c | 60 | SingletonPtr<PlatformMutex> SPI::_mutex; |

| tvendov | 0:6435b67ad23c | 61 | |

| tvendov | 0:6435b67ad23c | 62 | // ignore the fact there are multiple physical spis, and always update if it wasnt us last |

| tvendov | 0:6435b67ad23c | 63 | void SPI::aquire() { |

| tvendov | 0:6435b67ad23c | 64 | lock(); |

| tvendov | 0:6435b67ad23c | 65 | if (_owner != this) { |

| tvendov | 0:6435b67ad23c | 66 | spi_format(&_spi, _bits, _mode, 0); |

| tvendov | 0:6435b67ad23c | 67 | spi_frequency(&_spi, _hz); |

| tvendov | 0:6435b67ad23c | 68 | _owner = this; |

| tvendov | 0:6435b67ad23c | 69 | } |

| tvendov | 0:6435b67ad23c | 70 | unlock(); |

| tvendov | 0:6435b67ad23c | 71 | } |

| tvendov | 0:6435b67ad23c | 72 | |

| tvendov | 0:6435b67ad23c | 73 | int SPI::write(int value) { |

| tvendov | 0:6435b67ad23c | 74 | lock(); |

| tvendov | 0:6435b67ad23c | 75 | aquire(); |

| tvendov | 0:6435b67ad23c | 76 | int ret = spi_master_write(&_spi, value); |

| tvendov | 0:6435b67ad23c | 77 | unlock(); |

| tvendov | 0:6435b67ad23c | 78 | return ret; |

| tvendov | 0:6435b67ad23c | 79 | } |

| tvendov | 0:6435b67ad23c | 80 | |

| tvendov | 0:6435b67ad23c | 81 | void SPI::lock() { |

| tvendov | 0:6435b67ad23c | 82 | _mutex->lock(); |

| tvendov | 0:6435b67ad23c | 83 | } |

| tvendov | 0:6435b67ad23c | 84 | |

| tvendov | 0:6435b67ad23c | 85 | void SPI::unlock() { |

| tvendov | 0:6435b67ad23c | 86 | _mutex->unlock(); |

| tvendov | 0:6435b67ad23c | 87 | } |

| tvendov | 0:6435b67ad23c | 88 | |

| tvendov | 0:6435b67ad23c | 89 | #if DEVICE_SPI_ASYNCH |

| tvendov | 0:6435b67ad23c | 90 | |

| tvendov | 0:6435b67ad23c | 91 | int SPI::transfer(const void *tx_buffer, int tx_length, void *rx_buffer, int rx_length, unsigned char bit_width, const event_callback_t& callback, int event) |

| tvendov | 0:6435b67ad23c | 92 | { |

| tvendov | 0:6435b67ad23c | 93 | if (spi_active(&_spi)) { |

| tvendov | 0:6435b67ad23c | 94 | return queue_transfer(tx_buffer, tx_length, rx_buffer, rx_length, bit_width, callback, event); |

| tvendov | 0:6435b67ad23c | 95 | } |

| tvendov | 0:6435b67ad23c | 96 | start_transfer(tx_buffer, tx_length, rx_buffer, rx_length, bit_width, callback, event); |

| tvendov | 0:6435b67ad23c | 97 | return 0; |

| tvendov | 0:6435b67ad23c | 98 | } |

| tvendov | 0:6435b67ad23c | 99 | |

| tvendov | 0:6435b67ad23c | 100 | void SPI::abort_transfer() |

| tvendov | 0:6435b67ad23c | 101 | { |

| tvendov | 0:6435b67ad23c | 102 | spi_abort_asynch(&_spi); |

| tvendov | 0:6435b67ad23c | 103 | #if TRANSACTION_QUEUE_SIZE_SPI |

| tvendov | 0:6435b67ad23c | 104 | dequeue_transaction(); |

| tvendov | 0:6435b67ad23c | 105 | #endif |

| tvendov | 0:6435b67ad23c | 106 | } |

| tvendov | 0:6435b67ad23c | 107 | |

| tvendov | 0:6435b67ad23c | 108 | |

| tvendov | 0:6435b67ad23c | 109 | void SPI::clear_transfer_buffer() |

| tvendov | 0:6435b67ad23c | 110 | { |

| tvendov | 0:6435b67ad23c | 111 | #if TRANSACTION_QUEUE_SIZE_SPI |

| tvendov | 0:6435b67ad23c | 112 | _transaction_buffer.reset(); |

| tvendov | 0:6435b67ad23c | 113 | #endif |

| tvendov | 0:6435b67ad23c | 114 | } |

| tvendov | 0:6435b67ad23c | 115 | |

| tvendov | 0:6435b67ad23c | 116 | void SPI::abort_all_transfers() |

| tvendov | 0:6435b67ad23c | 117 | { |

| tvendov | 0:6435b67ad23c | 118 | clear_transfer_buffer(); |

| tvendov | 0:6435b67ad23c | 119 | abort_transfer(); |

| tvendov | 0:6435b67ad23c | 120 | } |

| tvendov | 0:6435b67ad23c | 121 | |

| tvendov | 0:6435b67ad23c | 122 | int SPI::set_dma_usage(DMAUsage usage) |

| tvendov | 0:6435b67ad23c | 123 | { |

| tvendov | 0:6435b67ad23c | 124 | if (spi_active(&_spi)) { |

| tvendov | 0:6435b67ad23c | 125 | return -1; |

| tvendov | 0:6435b67ad23c | 126 | } |

| tvendov | 0:6435b67ad23c | 127 | _usage = usage; |

| tvendov | 0:6435b67ad23c | 128 | return 0; |

| tvendov | 0:6435b67ad23c | 129 | } |

| tvendov | 0:6435b67ad23c | 130 | |

| tvendov | 0:6435b67ad23c | 131 | int SPI::queue_transfer(const void *tx_buffer, int tx_length, void *rx_buffer, int rx_length, unsigned char bit_width, const event_callback_t& callback, int event) |

| tvendov | 0:6435b67ad23c | 132 | { |

| tvendov | 0:6435b67ad23c | 133 | #if TRANSACTION_QUEUE_SIZE_SPI |

| tvendov | 0:6435b67ad23c | 134 | transaction_t t; |

| tvendov | 0:6435b67ad23c | 135 | |

| tvendov | 0:6435b67ad23c | 136 | t.tx_buffer = const_cast<void *>(tx_buffer); |

| tvendov | 0:6435b67ad23c | 137 | t.tx_length = tx_length; |

| tvendov | 0:6435b67ad23c | 138 | t.rx_buffer = rx_buffer; |

| tvendov | 0:6435b67ad23c | 139 | t.rx_length = rx_length; |

| tvendov | 0:6435b67ad23c | 140 | t.event = event; |

| tvendov | 0:6435b67ad23c | 141 | t.callback = callback; |

| tvendov | 0:6435b67ad23c | 142 | t.width = bit_width; |

| tvendov | 0:6435b67ad23c | 143 | Transaction<SPI> transaction(this, t); |

| tvendov | 0:6435b67ad23c | 144 | if (_transaction_buffer.full()) { |

| tvendov | 0:6435b67ad23c | 145 | return -1; // the buffer is full |

| tvendov | 0:6435b67ad23c | 146 | } else { |

| tvendov | 0:6435b67ad23c | 147 | core_util_critical_section_enter(); |

| tvendov | 0:6435b67ad23c | 148 | _transaction_buffer.push(transaction); |

| tvendov | 0:6435b67ad23c | 149 | if (!spi_active(&_spi)) { |

| tvendov | 0:6435b67ad23c | 150 | dequeue_transaction(); |

| tvendov | 0:6435b67ad23c | 151 | } |

| tvendov | 0:6435b67ad23c | 152 | core_util_critical_section_exit(); |

| tvendov | 0:6435b67ad23c | 153 | return 0; |

| tvendov | 0:6435b67ad23c | 154 | } |

| tvendov | 0:6435b67ad23c | 155 | #else |

| tvendov | 0:6435b67ad23c | 156 | return -1; |

| tvendov | 0:6435b67ad23c | 157 | #endif |

| tvendov | 0:6435b67ad23c | 158 | } |

| tvendov | 0:6435b67ad23c | 159 | |

| tvendov | 0:6435b67ad23c | 160 | void SPI::start_transfer(const void *tx_buffer, int tx_length, void *rx_buffer, int rx_length, unsigned char bit_width, const event_callback_t& callback, int event) |

| tvendov | 0:6435b67ad23c | 161 | { |

| tvendov | 0:6435b67ad23c | 162 | aquire(); |

| tvendov | 0:6435b67ad23c | 163 | _callback = callback; |

| tvendov | 0:6435b67ad23c | 164 | _irq.callback(&SPI::irq_handler_asynch); |

| tvendov | 0:6435b67ad23c | 165 | spi_master_transfer(&_spi, tx_buffer, tx_length, rx_buffer, rx_length, bit_width, _irq.entry(), event , _usage); |

| tvendov | 0:6435b67ad23c | 166 | } |

| tvendov | 0:6435b67ad23c | 167 | |

| tvendov | 0:6435b67ad23c | 168 | #if TRANSACTION_QUEUE_SIZE_SPI |

| tvendov | 0:6435b67ad23c | 169 | |

| tvendov | 0:6435b67ad23c | 170 | void SPI::start_transaction(transaction_t *data) |

| tvendov | 0:6435b67ad23c | 171 | { |

| tvendov | 0:6435b67ad23c | 172 | start_transfer(data->tx_buffer, data->tx_length, data->rx_buffer, data->rx_length, data->width, data->callback, data->event); |

| tvendov | 0:6435b67ad23c | 173 | } |

| tvendov | 0:6435b67ad23c | 174 | |

| tvendov | 0:6435b67ad23c | 175 | void SPI::dequeue_transaction() |

| tvendov | 0:6435b67ad23c | 176 | { |

| tvendov | 0:6435b67ad23c | 177 | Transaction<SPI> t; |

| tvendov | 0:6435b67ad23c | 178 | if (_transaction_buffer.pop(t)) { |

| tvendov | 0:6435b67ad23c | 179 | SPI* obj = t.get_object(); |

| tvendov | 0:6435b67ad23c | 180 | transaction_t* data = t.get_transaction(); |

| tvendov | 0:6435b67ad23c | 181 | obj->start_transaction(data); |

| tvendov | 0:6435b67ad23c | 182 | } |

| tvendov | 0:6435b67ad23c | 183 | } |

| tvendov | 0:6435b67ad23c | 184 | |

| tvendov | 0:6435b67ad23c | 185 | #endif |

| tvendov | 0:6435b67ad23c | 186 | |

| tvendov | 0:6435b67ad23c | 187 | void SPI::irq_handler_asynch(void) |

| tvendov | 0:6435b67ad23c | 188 | { |

| tvendov | 0:6435b67ad23c | 189 | int event = spi_irq_handler_asynch(&_spi); |

| tvendov | 0:6435b67ad23c | 190 | if (_callback && (event & SPI_EVENT_ALL)) { |

| tvendov | 0:6435b67ad23c | 191 | _callback.call(event & SPI_EVENT_ALL); |

| tvendov | 0:6435b67ad23c | 192 | } |

| tvendov | 0:6435b67ad23c | 193 | #if TRANSACTION_QUEUE_SIZE_SPI |

| tvendov | 0:6435b67ad23c | 194 | if (event & (SPI_EVENT_ALL | SPI_EVENT_INTERNAL_TRANSFER_COMPLETE)) { |

| tvendov | 0:6435b67ad23c | 195 | // SPI peripheral is free (event happend), dequeue transaction |

| tvendov | 0:6435b67ad23c | 196 | dequeue_transaction(); |

| tvendov | 0:6435b67ad23c | 197 | } |

| tvendov | 0:6435b67ad23c | 198 | #endif |

| tvendov | 0:6435b67ad23c | 199 | } |

| tvendov | 0:6435b67ad23c | 200 | |

| tvendov | 0:6435b67ad23c | 201 | #endif |

| tvendov | 0:6435b67ad23c | 202 | |

| tvendov | 0:6435b67ad23c | 203 | } // namespace mbed |

| tvendov | 0:6435b67ad23c | 204 | |

| tvendov | 0:6435b67ad23c | 205 | #endif |

| tvendov | 0:6435b67ad23c | 206 |