Library to handle the X-NUCLEO-IHM01A1 Motor Control Expansion Board based on the L6474 component.

Dependencies: X_NUCLEO_COMMON ST_INTERFACES

Dependents: Stepper_Matlab_Control SunTracker_BLE Stepper_Matlab_Control MemsMotorControl ... more

Fork of X_NUCLEO_IHM01A1 by

Motor Control Library

Introduction

Library to handle the X-NUCLEO-IHM01A1 Motor Control Expansion Board based on the the L6474 component.

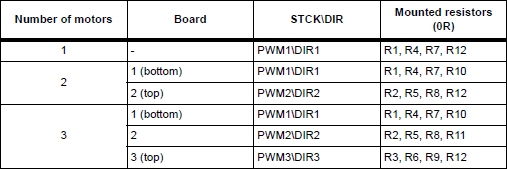

Daisy-Chain Configuration

This board can be stacked up to three times so that the L6474 components will be connected in daisy-chain configuration. For this purpose, some resistors must be correctly connected on the boards as depicted here below:

Platform compatibility

- NUCLEO boards have been tested with the default configuration provided by the HelloWorld_IHM01A1 example.

- LPCXpresso11U68 board has been tested with the following patch:

- to connect with a wire from the LPCX’s

D4pin to the IHM01A1’sD9pin; - to initialize the pwm PinName variable with

D4rather thanD9.

- to connect with a wire from the LPCX’s

- FRDM-K64F board has been tested with the following patch:

- to connect with a wire from the FRDM’s

D4pin to the IHM01A1’sD8pin; - to initialize the standby_reset PinName variable with

D4rather thanD8.

- to connect with a wire from the FRDM’s

Example Applications

- HelloWorld_IHM01A1

- HelloWorld_IHM01A1_2Motors

- MotorControl_IHM01A1

- MemsMotorControl

- MemsMotorControl_IHM01A1_IKS01A2

Components/l6474/L6474_config.h@33:8daea0279301, 2017-03-10 (annotated)

- Committer:

- davide.aliprandi@st.com

- Date:

- Fri Mar 10 11:07:50 2017 +0100

- Revision:

- 33:8daea0279301

Aligning to ARM mbed coding style.

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| davide.aliprandi@st.com | 33:8daea0279301 | 1 | /** |

| davide.aliprandi@st.com | 33:8daea0279301 | 2 | ****************************************************************************** |

| davide.aliprandi@st.com | 33:8daea0279301 | 3 | * @file L6474_target_config.h |

| davide.aliprandi@st.com | 33:8daea0279301 | 4 | * @author IPC Rennes |

| davide.aliprandi@st.com | 33:8daea0279301 | 5 | * @version V1.5.0 |

| davide.aliprandi@st.com | 33:8daea0279301 | 6 | * @date November 12, 2014 |

| davide.aliprandi@st.com | 33:8daea0279301 | 7 | * @brief Predefines values for the L6474 registers |

| davide.aliprandi@st.com | 33:8daea0279301 | 8 | * and for the devices parameters |

| davide.aliprandi@st.com | 33:8daea0279301 | 9 | * @note (C) COPYRIGHT 2014 STMicroelectronics |

| davide.aliprandi@st.com | 33:8daea0279301 | 10 | ****************************************************************************** |

| davide.aliprandi@st.com | 33:8daea0279301 | 11 | * @attention |

| davide.aliprandi@st.com | 33:8daea0279301 | 12 | * |

| davide.aliprandi@st.com | 33:8daea0279301 | 13 | * <h2><center>© COPYRIGHT(c) 2014 STMicroelectronics</center></h2> |

| davide.aliprandi@st.com | 33:8daea0279301 | 14 | * |

| davide.aliprandi@st.com | 33:8daea0279301 | 15 | * Redistribution and use in source and binary forms, with or without modification, |

| davide.aliprandi@st.com | 33:8daea0279301 | 16 | * are permitted provided that the following conditions are met: |

| davide.aliprandi@st.com | 33:8daea0279301 | 17 | * 1. Redistributions of source code must retain the above copyright notice, |

| davide.aliprandi@st.com | 33:8daea0279301 | 18 | * this list of conditions and the following disclaimer. |

| davide.aliprandi@st.com | 33:8daea0279301 | 19 | * 2. Redistributions in binary form must reproduce the above copyright notice, |

| davide.aliprandi@st.com | 33:8daea0279301 | 20 | * this list of conditions and the following disclaimer in the documentation |

| davide.aliprandi@st.com | 33:8daea0279301 | 21 | * and/or other materials provided with the distribution. |

| davide.aliprandi@st.com | 33:8daea0279301 | 22 | * 3. Neither the name of STMicroelectronics nor the names of its contributors |

| davide.aliprandi@st.com | 33:8daea0279301 | 23 | * may be used to endorse or promote products derived from this software |

| davide.aliprandi@st.com | 33:8daea0279301 | 24 | * without specific prior written permission. |

| davide.aliprandi@st.com | 33:8daea0279301 | 25 | * |

| davide.aliprandi@st.com | 33:8daea0279301 | 26 | * THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" |

| davide.aliprandi@st.com | 33:8daea0279301 | 27 | * AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE |

| davide.aliprandi@st.com | 33:8daea0279301 | 28 | * IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE |

| davide.aliprandi@st.com | 33:8daea0279301 | 29 | * DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE |

| davide.aliprandi@st.com | 33:8daea0279301 | 30 | * FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL |

| davide.aliprandi@st.com | 33:8daea0279301 | 31 | * DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR |

| davide.aliprandi@st.com | 33:8daea0279301 | 32 | * SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER |

| davide.aliprandi@st.com | 33:8daea0279301 | 33 | * CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, |

| davide.aliprandi@st.com | 33:8daea0279301 | 34 | * OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE |

| davide.aliprandi@st.com | 33:8daea0279301 | 35 | * OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE. |

| davide.aliprandi@st.com | 33:8daea0279301 | 36 | * |

| davide.aliprandi@st.com | 33:8daea0279301 | 37 | ****************************************************************************** |

| davide.aliprandi@st.com | 33:8daea0279301 | 38 | */ |

| davide.aliprandi@st.com | 33:8daea0279301 | 39 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 40 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 41 | /* Define to prevent recursive inclusion -------------------------------------*/ |

| davide.aliprandi@st.com | 33:8daea0279301 | 42 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 43 | #ifndef __L6474_TARGET_CONFIG_H |

| davide.aliprandi@st.com | 33:8daea0279301 | 44 | #define __L6474_TARGET_CONFIG_H |

| davide.aliprandi@st.com | 33:8daea0279301 | 45 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 46 | #ifdef __cplusplus |

| davide.aliprandi@st.com | 33:8daea0279301 | 47 | extern "C" { |

| davide.aliprandi@st.com | 33:8daea0279301 | 48 | #endif |

| davide.aliprandi@st.com | 33:8daea0279301 | 49 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 50 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 51 | /* Definitions ---------------------------------------------------------------*/ |

| davide.aliprandi@st.com | 33:8daea0279301 | 52 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 53 | /** @addtogroup BSP |

| davide.aliprandi@st.com | 33:8daea0279301 | 54 | * @{ |

| davide.aliprandi@st.com | 33:8daea0279301 | 55 | */ |

| davide.aliprandi@st.com | 33:8daea0279301 | 56 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 57 | /** @addtogroup L6474 |

| davide.aliprandi@st.com | 33:8daea0279301 | 58 | * @{ |

| davide.aliprandi@st.com | 33:8daea0279301 | 59 | */ |

| davide.aliprandi@st.com | 33:8daea0279301 | 60 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 61 | /** @addtogroup L6474_Exported_Constants |

| davide.aliprandi@st.com | 33:8daea0279301 | 62 | * @{ |

| davide.aliprandi@st.com | 33:8daea0279301 | 63 | */ |

| davide.aliprandi@st.com | 33:8daea0279301 | 64 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 65 | /** @defgroup Predefined_L6474_Registers_Values |

| davide.aliprandi@st.com | 33:8daea0279301 | 66 | * @{ |

| davide.aliprandi@st.com | 33:8daea0279301 | 67 | */ |

| davide.aliprandi@st.com | 33:8daea0279301 | 68 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 69 | /// The maximum number of devices in the daisy chain |

| davide.aliprandi@st.com | 33:8daea0279301 | 70 | #define MAX_NUMBER_OF_DEVICES (3) |

| davide.aliprandi@st.com | 33:8daea0279301 | 71 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 72 | /************************ Speed Profile *******************************/ |

| davide.aliprandi@st.com | 33:8daea0279301 | 73 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 74 | /// Acceleration rate in step/s2 for device 0 (must be greater than 0) |

| davide.aliprandi@st.com | 33:8daea0279301 | 75 | #define L6474_CONF_PARAM_ACC_DEVICE_0 (160) |

| davide.aliprandi@st.com | 33:8daea0279301 | 76 | /// Acceleration rate in step/s2 for device 1 (must be greater than 0) |

| davide.aliprandi@st.com | 33:8daea0279301 | 77 | #define L6474_CONF_PARAM_ACC_DEVICE_1 (160) |

| davide.aliprandi@st.com | 33:8daea0279301 | 78 | /// Acceleration rate in step/s2 for device 2 (must be greater than 0) |

| davide.aliprandi@st.com | 33:8daea0279301 | 79 | #define L6474_CONF_PARAM_ACC_DEVICE_2 (160) |

| davide.aliprandi@st.com | 33:8daea0279301 | 80 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 81 | /// Deceleration rate in step/s2 for device 0 (must be greater than 0) |

| davide.aliprandi@st.com | 33:8daea0279301 | 82 | #define L6474_CONF_PARAM_DEC_DEVICE_0 (160) |

| davide.aliprandi@st.com | 33:8daea0279301 | 83 | /// Deceleration rate in step/s2 for device 1 (must be greater than 0) |

| davide.aliprandi@st.com | 33:8daea0279301 | 84 | #define L6474_CONF_PARAM_DEC_DEVICE_1 (160) |

| davide.aliprandi@st.com | 33:8daea0279301 | 85 | /// Deceleration rate in step/s2 for device 2 (must be greater than 0) |

| davide.aliprandi@st.com | 33:8daea0279301 | 86 | #define L6474_CONF_PARAM_DEC_DEVICE_2 (160) |

| davide.aliprandi@st.com | 33:8daea0279301 | 87 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 88 | /// Maximum speed in step/s for device 0 (30 step/s < Maximum speed <= 10 000 step/s ) |

| davide.aliprandi@st.com | 33:8daea0279301 | 89 | #define L6474_CONF_PARAM_MAX_SPEED_DEVICE_0 (1600) |

| davide.aliprandi@st.com | 33:8daea0279301 | 90 | /// Maximum speed in step/s for device 1 (30 step/s < Maximum speed <= 10 000 step/s ) |

| davide.aliprandi@st.com | 33:8daea0279301 | 91 | #define L6474_CONF_PARAM_MAX_SPEED_DEVICE_1 (1600) |

| davide.aliprandi@st.com | 33:8daea0279301 | 92 | /// Maximum speed in step/s for device 2 (30 step/s < Maximum speed <= 10 000 step/s ) |

| davide.aliprandi@st.com | 33:8daea0279301 | 93 | #define L6474_CONF_PARAM_MAX_SPEED_DEVICE_2 (1600) |

| davide.aliprandi@st.com | 33:8daea0279301 | 94 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 95 | /// Minimum speed in step/s for device 0 (30 step/s <= Minimum speed < 10 000 step/s) |

| davide.aliprandi@st.com | 33:8daea0279301 | 96 | #define L6474_CONF_PARAM_MIN_SPEED_DEVICE_0 (800) |

| davide.aliprandi@st.com | 33:8daea0279301 | 97 | /// Minimum speed in step/s for device 1 (30 step/s <= Minimum speed < 10 000 step/s) |

| davide.aliprandi@st.com | 33:8daea0279301 | 98 | #define L6474_CONF_PARAM_MIN_SPEED_DEVICE_1 (800) |

| davide.aliprandi@st.com | 33:8daea0279301 | 99 | /// Minimum speed in step/s for device 2 (30 step/s <= Minimum speed < 10 000 step/s) |

| davide.aliprandi@st.com | 33:8daea0279301 | 100 | #define L6474_CONF_PARAM_MIN_SPEED_DEVICE_2 (800) |

| davide.aliprandi@st.com | 33:8daea0279301 | 101 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 102 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 103 | /************************ Phase Current Control *******************************/ |

| davide.aliprandi@st.com | 33:8daea0279301 | 104 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 105 | // Current value that is assigned to the torque regulation DAC |

| davide.aliprandi@st.com | 33:8daea0279301 | 106 | /// TVAL register value for device 0 (range 31.25mA to 4000mA) |

| davide.aliprandi@st.com | 33:8daea0279301 | 107 | #define L6474_CONF_PARAM_TVAL_DEVICE_0 (250) |

| davide.aliprandi@st.com | 33:8daea0279301 | 108 | /// TVAL register value for device 1 (range 31.25mA to 4000mA) |

| davide.aliprandi@st.com | 33:8daea0279301 | 109 | #define L6474_CONF_PARAM_TVAL_DEVICE_1 (250) |

| davide.aliprandi@st.com | 33:8daea0279301 | 110 | /// TVAL register value for device 2 (range 31.25mA to 4000mA) |

| davide.aliprandi@st.com | 33:8daea0279301 | 111 | #define L6474_CONF_PARAM_TVAL_DEVICE_2 (250) |

| davide.aliprandi@st.com | 33:8daea0279301 | 112 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 113 | /// Fall time value (T_FAST field of T_FAST register) for device 0 (range 2us to 32us) |

| davide.aliprandi@st.com | 33:8daea0279301 | 114 | #define L6474_CONF_PARAM_FAST_STEP_DEVICE_0 (L6474_FAST_STEP_12us) |

| davide.aliprandi@st.com | 33:8daea0279301 | 115 | /// Fall time value (T_FAST field of T_FAST register) for device 1 (range 2us to 32us) |

| davide.aliprandi@st.com | 33:8daea0279301 | 116 | #define L6474_CONF_PARAM_FAST_STEP_DEVICE_1 (L6474_FAST_STEP_12us) |

| davide.aliprandi@st.com | 33:8daea0279301 | 117 | /// Fall time value (T_FAST field of T_FAST register) for device 2 (range 2us to 32us) |

| davide.aliprandi@st.com | 33:8daea0279301 | 118 | #define L6474_CONF_PARAM_FAST_STEP_DEVICE_2 (L6474_FAST_STEP_12us) |

| davide.aliprandi@st.com | 33:8daea0279301 | 119 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 120 | /// Maximum fast decay time (T_OFF field of T_FAST register) for device 0 (range 2us to 32us) |

| davide.aliprandi@st.com | 33:8daea0279301 | 121 | #define L6474_CONF_PARAM_TOFF_FAST_DEVICE_0 (L6474_TOFF_FAST_8us) |

| davide.aliprandi@st.com | 33:8daea0279301 | 122 | /// Maximum fast decay time (T_OFF field of T_FAST register) for device 1 (range 2us to 32us) |

| davide.aliprandi@st.com | 33:8daea0279301 | 123 | #define L6474_CONF_PARAM_TOFF_FAST_DEVICE_1 (L6474_TOFF_FAST_8us) |

| davide.aliprandi@st.com | 33:8daea0279301 | 124 | /// Maximum fast decay time (T_OFF field of T_FAST register) for device 2 (range 2us to 32us) |

| davide.aliprandi@st.com | 33:8daea0279301 | 125 | #define L6474_CONF_PARAM_TOFF_FAST_DEVICE_2 (L6474_TOFF_FAST_8us) |

| davide.aliprandi@st.com | 33:8daea0279301 | 126 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 127 | /// Minimum ON time (TON_MIN register) for device 0 (range 0.5us to 64us) |

| davide.aliprandi@st.com | 33:8daea0279301 | 128 | #define L6474_CONF_PARAM_TON_MIN_DEVICE_0 (3) |

| davide.aliprandi@st.com | 33:8daea0279301 | 129 | /// Minimum ON time (TON_MIN register) for device 1 (range 0.5us to 64us) |

| davide.aliprandi@st.com | 33:8daea0279301 | 130 | #define L6474_CONF_PARAM_TON_MIN_DEVICE_1 (3) |

| davide.aliprandi@st.com | 33:8daea0279301 | 131 | /// Minimum ON time (TON_MIN register) for device 2 (range 0.5us to 64us) |

| davide.aliprandi@st.com | 33:8daea0279301 | 132 | #define L6474_CONF_PARAM_TON_MIN_DEVICE_2 (3) |

| davide.aliprandi@st.com | 33:8daea0279301 | 133 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 134 | /// Minimum OFF time (TOFF_MIN register) for device 0 (range 0.5us to 64us) |

| davide.aliprandi@st.com | 33:8daea0279301 | 135 | #define L6474_CONF_PARAM_TOFF_MIN_DEVICE_0 (21) |

| davide.aliprandi@st.com | 33:8daea0279301 | 136 | /// Minimum OFF time (TOFF_MIN register) for device 1 (range 0.5us to 64us) |

| davide.aliprandi@st.com | 33:8daea0279301 | 137 | #define L6474_CONF_PARAM_TOFF_MIN_DEVICE_1 (21) |

| davide.aliprandi@st.com | 33:8daea0279301 | 138 | /// Minimum OFF time (TOFF_MIN register) for device 2 (range 0.5us to 64us) |

| davide.aliprandi@st.com | 33:8daea0279301 | 139 | #define L6474_CONF_PARAM_TOFF_MIN_DEVICE_2 (21) |

| davide.aliprandi@st.com | 33:8daea0279301 | 140 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 141 | /******************************* Others ***************************************/ |

| davide.aliprandi@st.com | 33:8daea0279301 | 142 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 143 | /// Overcurrent threshold settings for device 0 (OCD_TH register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 144 | #define L6474_CONF_PARAM_OCD_TH_DEVICE_0 (L6474_OCD_TH_750mA) |

| davide.aliprandi@st.com | 33:8daea0279301 | 145 | /// Overcurrent threshold settings for device 1 (OCD_TH register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 146 | #define L6474_CONF_PARAM_OCD_TH_DEVICE_1 (L6474_OCD_TH_750mA) |

| davide.aliprandi@st.com | 33:8daea0279301 | 147 | /// Overcurrent threshold settings for device 2 (OCD_TH register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 148 | #define L6474_CONF_PARAM_OCD_TH_DEVICE_2 (L6474_OCD_TH_750mA) |

| davide.aliprandi@st.com | 33:8daea0279301 | 149 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 150 | /// Alarm settings for device 0 (ALARM_EN register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 151 | #define L6474_CONF_PARAM_ALARM_EN_DEVICE_0 (L6474_ALARM_EN_OVERCURRENT |\ |

| davide.aliprandi@st.com | 33:8daea0279301 | 152 | L6474_ALARM_EN_THERMAL_SHUTDOWN |\ |

| davide.aliprandi@st.com | 33:8daea0279301 | 153 | L6474_ALARM_EN_THERMAL_WARNING |\ |

| davide.aliprandi@st.com | 33:8daea0279301 | 154 | L6474_ALARM_EN_UNDERVOLTAGE |\ |

| davide.aliprandi@st.com | 33:8daea0279301 | 155 | L6474_ALARM_EN_SW_TURN_ON |\ |

| davide.aliprandi@st.com | 33:8daea0279301 | 156 | L6474_ALARM_EN_WRONG_NPERF_CMD) |

| davide.aliprandi@st.com | 33:8daea0279301 | 157 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 158 | ///Alarm settings for device 1 (ALARM_EN register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 159 | #define L6474_CONF_PARAM_ALARM_EN_DEVICE_1 (L6474_ALARM_EN_OVERCURRENT |\ |

| davide.aliprandi@st.com | 33:8daea0279301 | 160 | L6474_ALARM_EN_THERMAL_SHUTDOWN |\ |

| davide.aliprandi@st.com | 33:8daea0279301 | 161 | L6474_ALARM_EN_THERMAL_WARNING |\ |

| davide.aliprandi@st.com | 33:8daea0279301 | 162 | L6474_ALARM_EN_UNDERVOLTAGE |\ |

| davide.aliprandi@st.com | 33:8daea0279301 | 163 | L6474_ALARM_EN_SW_TURN_ON |\ |

| davide.aliprandi@st.com | 33:8daea0279301 | 164 | L6474_ALARM_EN_WRONG_NPERF_CMD) |

| davide.aliprandi@st.com | 33:8daea0279301 | 165 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 166 | /// Alarm settings for device 2 (ALARM_EN register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 167 | #define L6474_CONF_PARAM_ALARM_EN_DEVICE_2 (L6474_ALARM_EN_OVERCURRENT |\ |

| davide.aliprandi@st.com | 33:8daea0279301 | 168 | L6474_ALARM_EN_THERMAL_SHUTDOWN |\ |

| davide.aliprandi@st.com | 33:8daea0279301 | 169 | L6474_ALARM_EN_THERMAL_WARNING |\ |

| davide.aliprandi@st.com | 33:8daea0279301 | 170 | L6474_ALARM_EN_UNDERVOLTAGE |\ |

| davide.aliprandi@st.com | 33:8daea0279301 | 171 | L6474_ALARM_EN_SW_TURN_ON |\ |

| davide.aliprandi@st.com | 33:8daea0279301 | 172 | L6474_ALARM_EN_WRONG_NPERF_CMD) |

| davide.aliprandi@st.com | 33:8daea0279301 | 173 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 174 | /// Step selection settings for device 0 (STEP_SEL field of STEP_MODE register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 175 | #define L6474_CONF_PARAM_STEP_SEL_DEVICE_0 (L6474_STEP_SEL_1_16) |

| davide.aliprandi@st.com | 33:8daea0279301 | 176 | /// Step selection settings for device 1 (STEP_SEL field of STEP_MODE register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 177 | #define L6474_CONF_PARAM_STEP_SEL_DEVICE_1 (L6474_STEP_SEL_1_16) |

| davide.aliprandi@st.com | 33:8daea0279301 | 178 | /// Step selection settings for device 2 (STEP_SEL field of STEP_MODE register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 179 | #define L6474_CONF_PARAM_STEP_SEL_DEVICE_2 (L6474_STEP_SEL_1_16) |

| davide.aliprandi@st.com | 33:8daea0279301 | 180 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 181 | /// Synch. selection settings for device 0 (SYNC_SEL field of STEP_MODE register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 182 | #define L6474_CONF_PARAM_SYNC_SEL_DEVICE_0 (L6474_SYNC_SEL_1_2) |

| davide.aliprandi@st.com | 33:8daea0279301 | 183 | /// Synch. selection settings for device 1 (SYNC_SEL field of STEP_MODE register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 184 | #define L6474_CONF_PARAM_SYNC_SEL_DEVICE_1 (L6474_SYNC_SEL_1_2) |

| davide.aliprandi@st.com | 33:8daea0279301 | 185 | /// Synch. selection settings for device 2 (SYNC_SEL field of STEP_MODE register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 186 | #define L6474_CONF_PARAM_SYNC_SEL_DEVICE_2 (L6474_SYNC_SEL_1_2) |

| davide.aliprandi@st.com | 33:8daea0279301 | 187 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 188 | /// Target Swicthing Period for device 0 (field TOFF of CONFIG register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 189 | #define L6474_CONF_PARAM_TOFF_DEVICE_0 (L6474_CONFIG_TOFF_044us) |

| davide.aliprandi@st.com | 33:8daea0279301 | 190 | /// Target Swicthing Period for device 1 (field TOFF of CONFIG register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 191 | #define L6474_CONF_PARAM_TOFF_DEVICE_1 (L6474_CONFIG_TOFF_044us) |

| davide.aliprandi@st.com | 33:8daea0279301 | 192 | /// Target Swicthing Period for device 2 (field TOFF of CONFIG register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 193 | #define L6474_CONF_PARAM_TOFF_DEVICE_2 (L6474_CONFIG_TOFF_044us) |

| davide.aliprandi@st.com | 33:8daea0279301 | 194 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 195 | /// Slew rate for device 0 (POW_SR field of CONFIG register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 196 | #define L6474_CONF_PARAM_SR_DEVICE_0 (L6474_CONFIG_SR_320V_us) |

| davide.aliprandi@st.com | 33:8daea0279301 | 197 | /// Slew rate for device 1 (POW_SR field of CONFIG register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 198 | #define L6474_CONF_PARAM_SR_DEVICE_1 (L6474_CONFIG_SR_320V_us) |

| davide.aliprandi@st.com | 33:8daea0279301 | 199 | /// Slew rate for device 2 (POW_SR field of CONFIG register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 200 | #define L6474_CONF_PARAM_SR_DEVICE_2 (L6474_CONFIG_SR_320V_us) |

| davide.aliprandi@st.com | 33:8daea0279301 | 201 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 202 | /// Over current shutwdown enabling for device 0 (OC_SD field of CONFIG register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 203 | #define L6474_CONF_PARAM_OC_SD_DEVICE_0 (L6474_CONFIG_OC_SD_ENABLE) |

| davide.aliprandi@st.com | 33:8daea0279301 | 204 | /// Over current shutwdown enabling for device 1 (OC_SD field of CONFIG register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 205 | #define L6474_CONF_PARAM_OC_SD_DEVICE_1 (L6474_CONFIG_OC_SD_ENABLE) |

| davide.aliprandi@st.com | 33:8daea0279301 | 206 | /// Over current shutwdown enabling for device 2 (OC_SD field of CONFIG register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 207 | #define L6474_CONF_PARAM_OC_SD_DEVICE_2 (L6474_CONFIG_OC_SD_ENABLE) |

| davide.aliprandi@st.com | 33:8daea0279301 | 208 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 209 | /// Torque regulation method for device 0 (EN_TQREG field of CONFIG register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 210 | #define L6474_CONF_PARAM_TQ_REG_DEVICE_0 (L6474_CONFIG_EN_TQREG_TVAL_USED) |

| davide.aliprandi@st.com | 33:8daea0279301 | 211 | ///Torque regulation method for device 1 (EN_TQREG field of CONFIG register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 212 | #define L6474_CONF_PARAM_TQ_REG_DEVICE_1 (L6474_CONFIG_EN_TQREG_TVAL_USED) |

| davide.aliprandi@st.com | 33:8daea0279301 | 213 | /// Torque regulation method for device 2 (EN_TQREG field of CONFIG register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 214 | #define L6474_CONF_PARAM_TQ_REG_DEVICE_2 (L6474_CONFIG_EN_TQREG_TVAL_USED) |

| davide.aliprandi@st.com | 33:8daea0279301 | 215 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 216 | /// Clock setting for device 0 (OSC_CLK_SEL field of CONFIG register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 217 | #define L6474_CONF_PARAM_CLOCK_SETTING_DEVICE_0 (L6474_CONFIG_INT_16MHZ) |

| davide.aliprandi@st.com | 33:8daea0279301 | 218 | /// Clock setting for device 1 (OSC_CLK_SEL field of CONFIG register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 219 | #define L6474_CONF_PARAM_CLOCK_SETTING_DEVICE_1 (L6474_CONFIG_INT_16MHZ) |

| davide.aliprandi@st.com | 33:8daea0279301 | 220 | /// Clock setting for device 2 (OSC_CLK_SEL field of CONFIG register) |

| davide.aliprandi@st.com | 33:8daea0279301 | 221 | #define L6474_CONF_PARAM_CLOCK_SETTING_DEVICE_2 (L6474_CONFIG_INT_16MHZ) |

| davide.aliprandi@st.com | 33:8daea0279301 | 222 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 223 | #ifdef __cplusplus |

| davide.aliprandi@st.com | 33:8daea0279301 | 224 | } |

| davide.aliprandi@st.com | 33:8daea0279301 | 225 | #endif |

| davide.aliprandi@st.com | 33:8daea0279301 | 226 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 227 | #endif /* __L6474_TARGET_CONFIG_H */ |

| davide.aliprandi@st.com | 33:8daea0279301 | 228 | |

| davide.aliprandi@st.com | 33:8daea0279301 | 229 | /************************ (C) COPYRIGHT STMicroelectronics *****END OF FILE****/ |

X-NUCLEO-IHM01A1 Stepper Motor Driver

X-NUCLEO-IHM01A1 Stepper Motor Driver