Temporary Connector Reversed Version

Dependencies: UniGraphic mbed vt100

afero_poc15_180403R , J1 のピン配置を反転させたヴァージョンです。

Color2系を使用するためには以下のピンをジャンパで接続してください。

J1-D7 <-> J1-D0

J1-D6 <-> J1-D1

(調査中) また、こちらでテストした範囲では、

FRDM-KL25Z の V3.3 を、Modulo2 の VCC_3V3 ピンに接続してやる必要がありました。

尚、J1-D1, D0 を使用するために UART を無効にしているため

ログは表示されません。

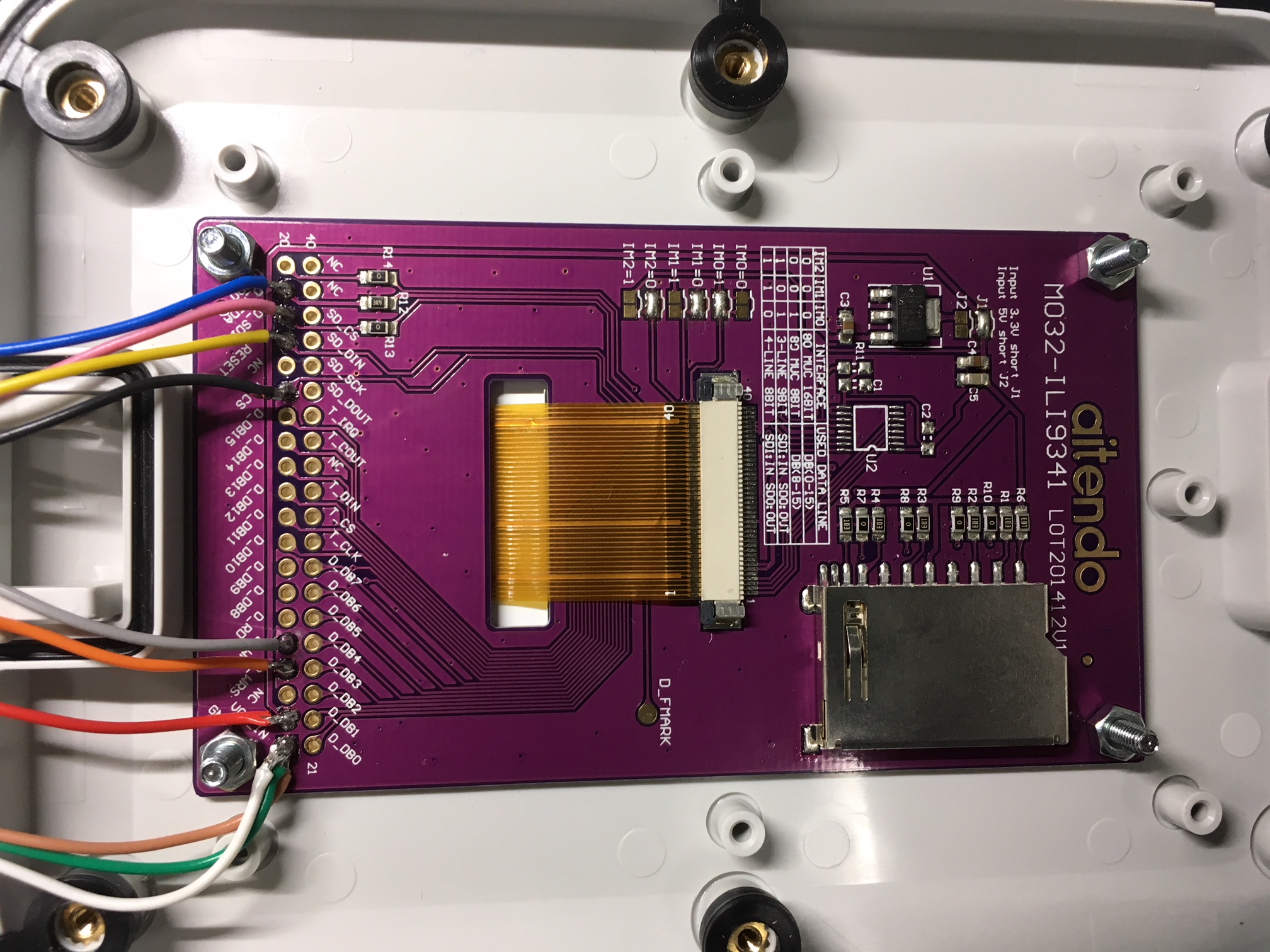

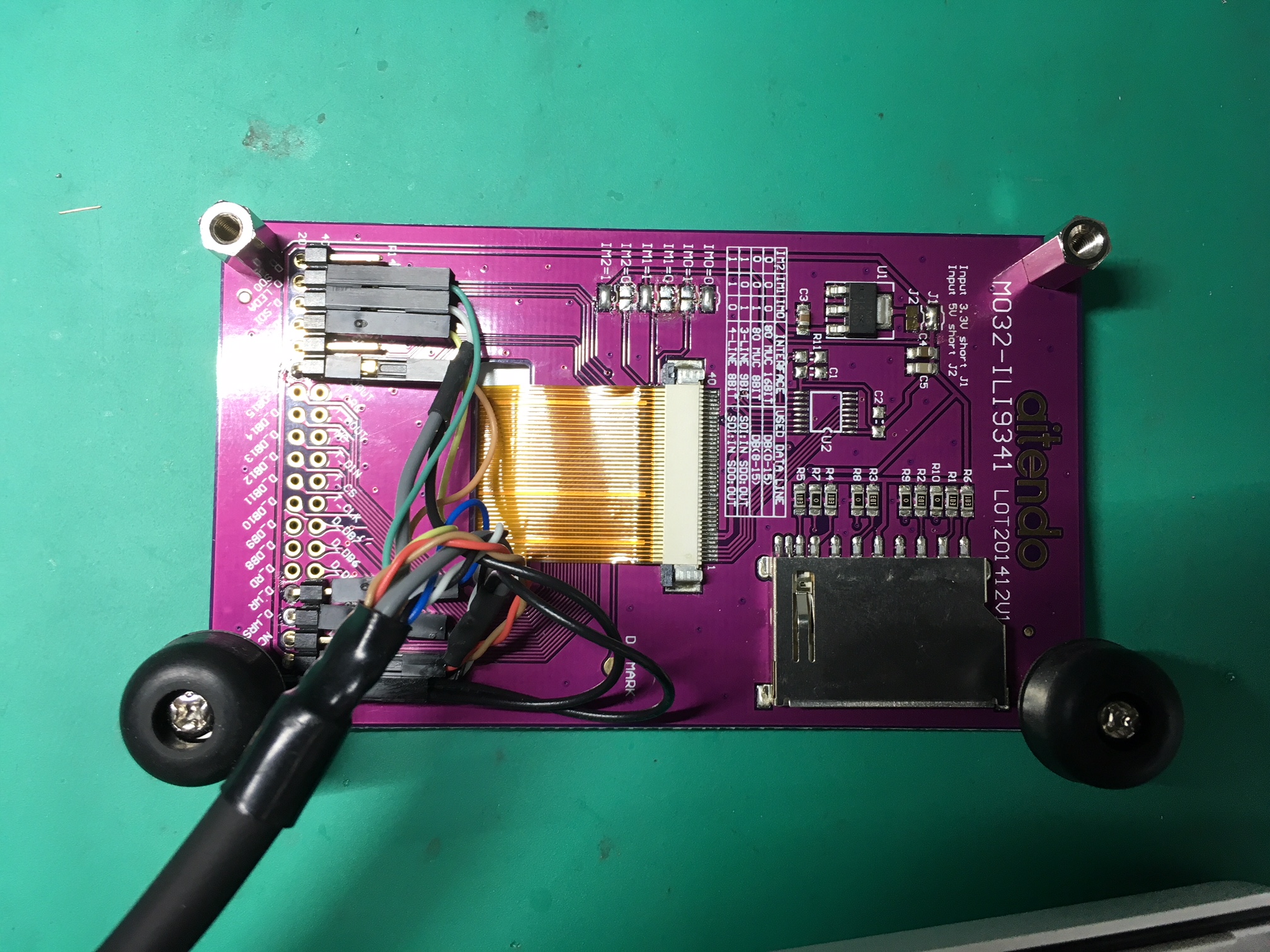

TFTモジュールについて

aitendoのTFTモジュールはデフォルトでは8bit bus モードになっています。

半田のジャンパを変えて、SPIの設定にしてください。

サーミスタについて

POC1.5 では サーミスタは 25℃の時に抵抗値が 50.0kΩになる502AT-11 が

4.95kΩのプルアップ(実際は10kΩx2の並列)で使用されていました。

今回の試作では抵抗値が 10.0kΩの 103AT-11 が

5.1kΩのプルアップで使用されていますので、係数を合わせるために

SMTC502AT-11 のコンストラクタを

R0 = 10.0

R1 = 5.1

B = 3435

T0 = 298.15

で呼ぶように変更しました。

edge_utils/KL25Z_SystemInit.c

- Committer:

- Rhyme

- Date:

- 2018-04-24

- Revision:

- 1:6c54dc8acf96

- Parent:

- 0:0b6732b53bf4

File content as of revision 1:6c54dc8acf96:

#if defined (TARGET_KL25Z)

/*

** ###################################################################

** Processor: MKL25Z128VLK4

** Compilers: ARM Compiler

** Freescale C/C++ for Embedded ARM

** GNU C Compiler

** IAR ANSI C/C++ Compiler for ARM

**

** Reference manual: KL25RM, Rev.1, Jun 2012

** Version: rev. 1.1, 2012-06-21

**

** Abstract:

** Provides a system configuration function and a global variable that

** contains the system frequency. It configures the device and initializes

** the oscillator (PLL) that is part of the microcontroller device.

**

** Copyright: 2012 Freescale Semiconductor, Inc. All Rights Reserved.

**

** http: www.freescale.com

** mail: support@freescale.com

**

** Revisions:

** - rev. 1.0 (2012-06-13)

** Initial version.

** - rev. 1.1 (2012-06-21)

** Update according to reference manual rev. 1.

**

** ###################################################################

*/

/**

* @file MKL25Z4

* @version 1.1

* @date 2012-06-21

* @brief Device specific configuration file for MKL25Z4 (implementation file)

*

* Provides a system configuration function and a global variable that contains

* the system frequency. It configures the device and initializes the oscillator

* (PLL) that is part of the microcontroller device.

*/

#include <stdint.h>

#include "MKL25Z4.h"

//MODIFICATION: We DO want watchdog, uC default after reset is enabled with timeout=1024ms (2^10*LPO=1KHz)

//#define DISABLE_WDOG 1

#define CLOCK_SETUP 1

/* Predefined clock setups

0 ... Multipurpose Clock Generator (MCG) in FLL Engaged Internal (FEI) mode

Reference clock source for MCG module is the slow internal clock source 32.768kHz

Core clock = 41.94MHz, BusClock = 13.98MHz

1 ... Multipurpose Clock Generator (MCG) in PLL Engaged External (PEE) mode

Reference clock source for MCG module is an external crystal 8MHz

Core clock = 48MHz, BusClock = 24MHz

2 ... Multipurpose Clock Generator (MCG) in Bypassed Low Power External (BLPE) mode

Core clock/Bus clock derived directly from an external crystal 8MHz with no multiplication

Core clock = 8MHz, BusClock = 8MHz

3 ... Multipurpose Clock Generator (MCG) in FLL Engaged External (FEE) mode

Reference clock source for MCG module is an external crystal 32.768kHz

Core clock = 47.97MHz, BusClock = 23.98MHz

This setup sets the RTC to be driven by the MCU clock directly without the need of an external source.

RTC register values are retained when MCU is reset although there will be a slight (mSec's)loss of time

accuracy durring the reset period. RTC will reset on power down.

*/

/*----------------------------------------------------------------------------

Define clock source values

*----------------------------------------------------------------------------*/

#if (CLOCK_SETUP == 0)

#define CPU_XTAL_CLK_HZ 8000000u /* Value of the external crystal or oscillator clock frequency in Hz */

#define CPU_INT_SLOW_CLK_HZ 32768u /* Value of the slow internal oscillator clock frequency in Hz */

#define CPU_INT_FAST_CLK_HZ 4000000u /* Value of the fast internal oscillator clock frequency in Hz */

#define DEFAULT_SYSTEM_CLOCK 41943040u /* Default System clock value */

#elif (CLOCK_SETUP == 1)

#define CPU_XTAL_CLK_HZ 8000000u /* Value of the external crystal or oscillator clock frequency in Hz */

#define CPU_INT_SLOW_CLK_HZ 32768u /* Value of the slow internal oscillator clock frequency in Hz */

#define CPU_INT_FAST_CLK_HZ 4000000u /* Value of the fast internal oscillator clock frequency in Hz */

#define DEFAULT_SYSTEM_CLOCK 48000000u /* Default System clock value */

#elif (CLOCK_SETUP == 2)

#define CPU_XTAL_CLK_HZ 8000000u /* Value of the external crystal or oscillator clock frequency in Hz */

#define CPU_INT_SLOW_CLK_HZ 32768u /* Value of the slow internal oscillator clock frequency in Hz */

#define CPU_INT_FAST_CLK_HZ 4000000u /* Value of the fast internal oscillator clock frequency in Hz */

#define DEFAULT_SYSTEM_CLOCK 8000000u /* Default System clock value */

#elif (CLOCK_SETUP == 3)

#define CPU_XTAL_CLK_HZ 32768u /* Value of the external crystal or oscillator clock frequency in Hz */

#define CPU_INT_SLOW_CLK_HZ 32768u /* Value of the slow internal oscillator clock frequency in Hz */

#define CPU_INT_FAST_CLK_HZ 4000000u /* Value of the fast internal oscillator clock frequency in Hz */

#define DEFAULT_SYSTEM_CLOCK 47972352u /* Default System clock value */

#endif /* (CLOCK_SETUP == 3) */

/* ----------------------------------------------------------------------------

-- Core clock

---------------------------------------------------------------------------- */

//MODIFICATION: That vartiable already exists

// uint32_t SystemCoreClock = DEFAULT_SYSTEM_CLOCK;

/* ----------------------------------------------------------------------------

-- SystemInit()

---------------------------------------------------------------------------- */

void $Sub$$SystemInit (void) {

//MODIFICATION:

// That variable already exists, we set it here

SystemCoreClock = DEFAULT_SYSTEM_CLOCK;

// We want visual indication of boot time with red LED on

//TODO

#if (DISABLE_WDOG)

/* Disable the WDOG module */

/* SIM_COPC: COPT=0,COPCLKS=0,COPW=0 */

SIM->COPC = (uint32_t)0x00u;

#endif /* (DISABLE_WDOG) */

#if (CLOCK_SETUP == 0)

/* SIM->CLKDIV1: OUTDIV1=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,OUTDIV4=2,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

SIM->CLKDIV1 = (uint32_t)0x00020000UL; /* Update system prescalers */

/* Switch to FEI Mode */

/* MCG->C1: CLKS=0,FRDIV=0,IREFS=1,IRCLKEN=1,IREFSTEN=0 */

MCG->C1 = (uint8_t)0x06U;

/* MCG_C2: LOCRE0=0,??=0,RANGE0=0,HGO0=0,EREFS0=0,LP=0,IRCS=0 */

MCG->C2 = (uint8_t)0x00U;

/* MCG->C4: DMX32=0,DRST_DRS=1 */

MCG->C4 = (uint8_t)((MCG->C4 & (uint8_t)~(uint8_t)0xC0U) | (uint8_t)0x20U);

/* OSC0->CR: ERCLKEN=1,??=0,EREFSTEN=0,??=0,SC2P=0,SC4P=0,SC8P=0,SC16P=0 */

OSC0->CR = (uint8_t)0x80U;

/* MCG->C5: ??=0,PLLCLKEN0=0,PLLSTEN0=0,PRDIV0=0 */

MCG->C5 = (uint8_t)0x00U;

/* MCG->C6: LOLIE0=0,PLLS=0,CME0=0,VDIV0=0 */

MCG->C6 = (uint8_t)0x00U;

while((MCG->S & MCG_S_IREFST_MASK) == 0x00U) { /* Check that the source of the FLL reference clock is the internal reference clock. */

}

while((MCG->S & 0x0CU) != 0x00U) { /* Wait until output of the FLL is selected */

}

#elif (CLOCK_SETUP == 1)

/* SIM->SCGC5: PORTA=1 */

SIM->SCGC5 |= (uint32_t)0x0200UL; /* Enable clock gate for ports to enable pin routing */

/* SIM->CLKDIV1: OUTDIV1=1,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,OUTDIV4=1,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

SIM->CLKDIV1 = (uint32_t)0x10010000UL; /* Update system prescalers */

/* PORTA->PCR18: ISF=0,MUX=0 */

PORTA->PCR[18] &= (uint32_t)~0x01000700UL;

/* PORTA->PCR19: ISF=0,MUX=0 */

PORTA->PCR[19] &= (uint32_t)~0x01000700UL;

/* Switch to FBE Mode */

/* OSC0->CR: ERCLKEN=1,??=0,EREFSTEN=0,??=0,SC2P=1,SC4P=0,SC8P=0,SC16P=1 */

OSC0->CR = (uint8_t)0x89U;

/* MCG->C2: LOCRE0=0,??=0,RANGE0=2,HGO0=0,EREFS0=1,LP=0,IRCS=0 */

MCG->C2 = (uint8_t)0x24U;

/* MCG->C1: CLKS=2,FRDIV=3,IREFS=0,IRCLKEN=1,IREFSTEN=0 */

MCG->C1 = (uint8_t)0x9AU;

/* MCG->C4: DMX32=0,DRST_DRS=0 */

MCG->C4 &= (uint8_t)~(uint8_t)0xE0U;

/* MCG->C5: ??=0,PLLCLKEN0=0,PLLSTEN0=0,PRDIV0=1 */

MCG->C5 = (uint8_t)0x01U;

/* MCG->C6: LOLIE0=0,PLLS=0,CME0=0,VDIV0=0 */

MCG->C6 = (uint8_t)0x00U;

while((MCG->S & MCG_S_IREFST_MASK) != 0x00U) { /* Check that the source of the FLL reference clock is the external reference clock. */

}

while((MCG->S & 0x0CU) != 0x08U) { /* Wait until external reference clock is selected as MCG output */

}

/* Switch to PBE Mode */

/* MCG->C6: LOLIE0=0,PLLS=1,CME0=0,VDIV0=0 */

MCG->C6 = (uint8_t)0x40U;

while((MCG->S & 0x0CU) != 0x08U) { /* Wait until external reference clock is selected as MCG output */

}

while((MCG->S & MCG_S_LOCK0_MASK) == 0x00U) { /* Wait until locked */

}

/* Switch to PEE Mode */

/* MCG->C1: CLKS=0,FRDIV=3,IREFS=0,IRCLKEN=1,IREFSTEN=0 */

MCG->C1 = (uint8_t)0x1AU;

while((MCG->S & 0x0CU) != 0x0CU) { /* Wait until output of the PLL is selected */

}

#elif (CLOCK_SETUP == 2)

/* SIM->SCGC5: PORTA=1 */

SIM->SCGC5 |= (uint32_t)0x0200UL; /* Enable clock gate for ports to enable pin routing */

/* SIM->CLKDIV1: OUTDIV1=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,OUTDIV4=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

SIM->CLKDIV1 = (uint32_t)0x00000000UL; /* Update system prescalers */

/* PORTA->PCR18: ISF=0,MUX=0 */

PORTA->PCR[18] &= (uint32_t)~0x01000700UL;

/* PORTA->PCR19: ISF=0,MUX=0 */

PORTA->PCR[19] &= (uint32_t)~0x01000700UL;

/* Switch to FBE Mode */

/* OSC0->CR: ERCLKEN=1,??=0,EREFSTEN=0,??=0,SC2P=1,SC4P=0,SC8P=0,SC16P=1 */

OSC0->CR = (uint8_t)0x89U;

/* MCG->C2: LOCRE0=0,??=0,RANGE0=2,HGO0=0,EREFS0=1,LP=0,IRCS=0 */

MCG->C2 = (uint8_t)0x24U;

/* MCG->C1: CLKS=2,FRDIV=3,IREFS=0,IRCLKEN=1,IREFSTEN=0 */

MCG->C1 = (uint8_t)0x9AU;

/* MCG->C4: DMX32=0,DRST_DRS=0 */

MCG->C4 &= (uint8_t)~(uint8_t)0xE0U;

/* MCG->C5: ??=0,PLLCLKEN0=0,PLLSTEN0=0,PRDIV0=0 */

MCG->C5 = (uint8_t)0x00U;

/* MCG->C6: LOLIE0=0,PLLS=0,CME0=0,VDIV0=0 */

MCG->C6 = (uint8_t)0x00U;

while((MCG->S & MCG_S_IREFST_MASK) != 0x00U) { /* Check that the source of the FLL reference clock is the external reference clock. */

}

while((MCG->S & 0x0CU) != 0x08U) { /* Wait until external reference clock is selected as MCG output */

}

/* Switch to BLPE Mode */

/* MCG->C2: LOCRE0=0,??=0,RANGE0=2,HGO0=0,EREFS0=1,LP=1,IRCS=0 */

MCG->C2 = (uint8_t)0x26U;

while((MCG->S & 0x0CU) != 0x08U) { /* Wait until external reference clock is selected as MCG output */

}

#elif (CLOCK_SETUP == 3)

/* SIM->SCGC5: PORTA=1 */

SIM->SCGC5 |= SIM_SCGC5_PORTA_MASK; /* Enable clock gate for ports to enable pin routing */

/* SIM->CLKDIV1: OUTDIV1=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,OUTDIV4=1,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

SIM->CLKDIV1 = (SIM_CLKDIV1_OUTDIV1(0x00) | SIM_CLKDIV1_OUTDIV4(0x01)); /* Update system prescalers */

/* PORTA->PCR[3]: ISF=0,MUX=0 */

PORTA->PCR[3] &= (uint32_t)~(uint32_t)((PORT_PCR_ISF_MASK | PORT_PCR_MUX(0x07)));

/* PORTA->PCR[4]: ISF=0,MUX=0 */

PORTA->PCR[4] &= (uint32_t)~(uint32_t)((PORT_PCR_ISF_MASK | PORT_PCR_MUX(0x07)));

/* Switch to FEE Mode */

/* MCG->C2: LOCRE0=0,??=0,RANGE0=0,HGO0=0,EREFS0=1,LP=0,IRCS=0 */

MCG->C2 = (MCG_C2_RANGE0(0x00) | MCG_C2_EREFS0_MASK);

/* OSC0->CR: ERCLKEN=1,??=0,EREFSTEN=0,??=0,SC2P=0,SC4P=0,SC8P=0,SC16P=0 */

OSC0->CR = OSC_CR_ERCLKEN_MASK | OSC_CR_SC16P_MASK | OSC_CR_SC4P_MASK | OSC_CR_SC2P_MASK;

/* MCG->C1: CLKS=0,FRDIV=0,IREFS=0,IRCLKEN=1,IREFSTEN=0 */

MCG->C1 = (MCG_C1_CLKS(0x00) | MCG_C1_FRDIV(0x00) | MCG_C1_IRCLKEN_MASK);

/* MCG->C4: DMX32=1,DRST_DRS=1 */

MCG->C4 = (uint8_t)((MCG->C4 & (uint8_t)~(uint8_t)(

MCG_C4_DRST_DRS(0x02)

)) | (uint8_t)(

MCG_C4_DMX32_MASK |

MCG_C4_DRST_DRS(0x01)

));

while((MCG->S & MCG_S_IREFST_MASK) != 0x00U) { /* Check that the source of the FLL reference clock is the external reference clock. */

}

while((MCG->S & 0x0CU) != 0x00U) { /* Wait until output of the FLL is selected */

}

#endif /* (CLOCK_SETUP == 3) */

}

#endif // TARGET_KL25Z

La Suno

La Suno