Temporary Connector Reversed Version

Dependencies: UniGraphic mbed vt100

afero_poc15_180403R , J1 のピン配置を反転させたヴァージョンです。

Color2系を使用するためには以下のピンをジャンパで接続してください。

J1-D7 <-> J1-D0

J1-D6 <-> J1-D1

(調査中) また、こちらでテストした範囲では、

FRDM-KL25Z の V3.3 を、Modulo2 の VCC_3V3 ピンに接続してやる必要がありました。

尚、J1-D1, D0 を使用するために UART を無効にしているため

ログは表示されません。

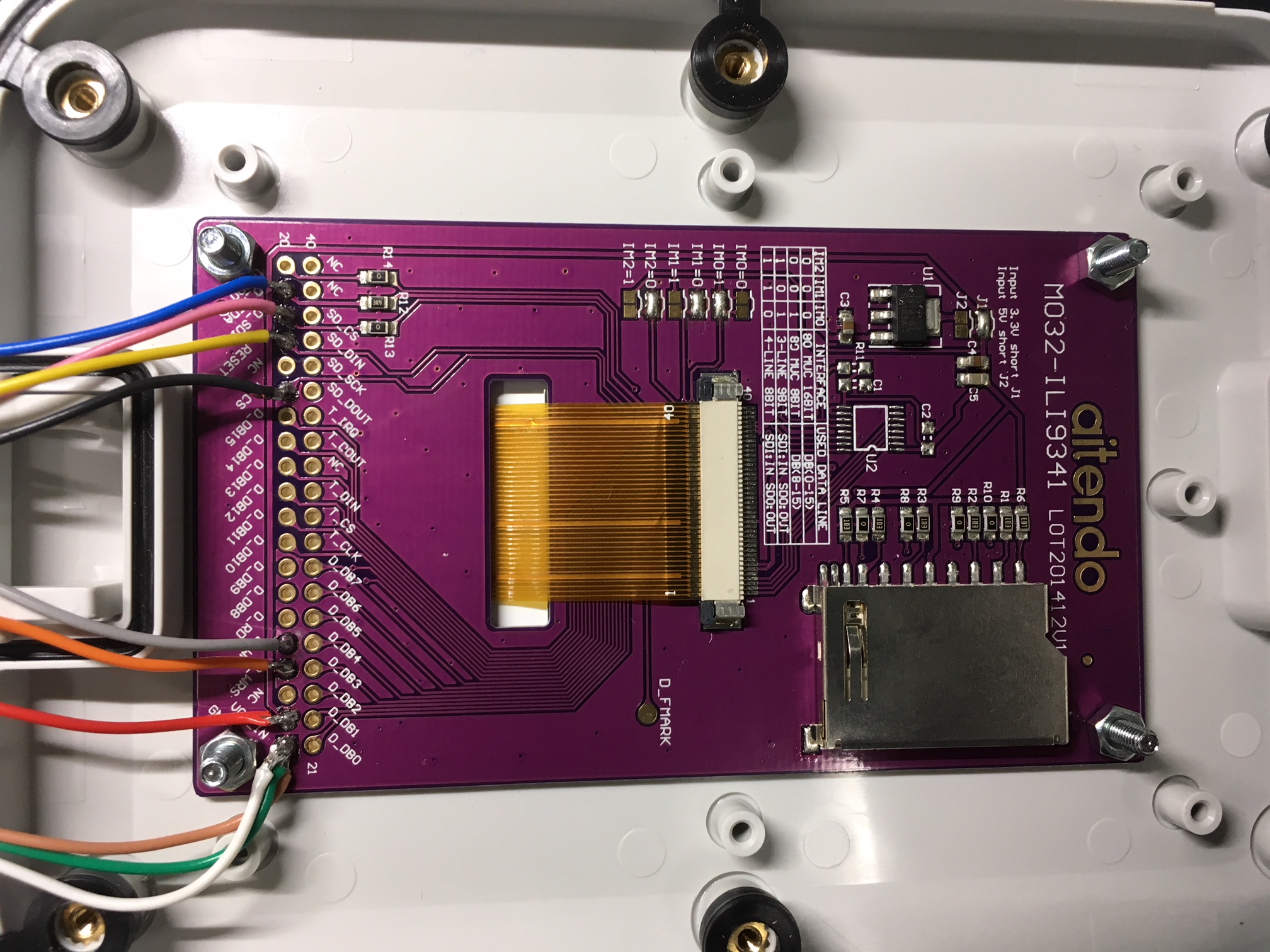

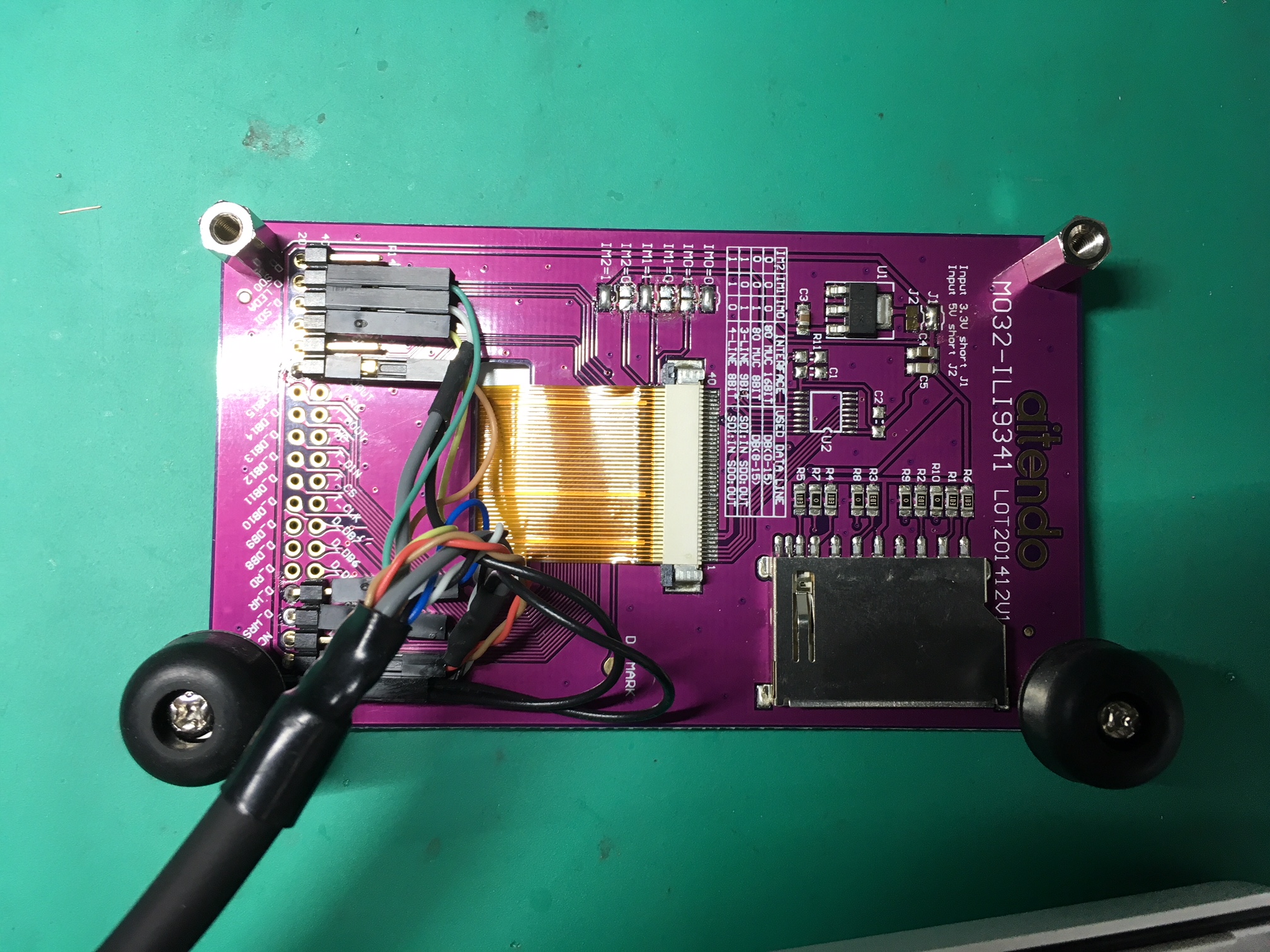

TFTモジュールについて

aitendoのTFTモジュールはデフォルトでは8bit bus モードになっています。

半田のジャンパを変えて、SPIの設定にしてください。

サーミスタについて

POC1.5 では サーミスタは 25℃の時に抵抗値が 50.0kΩになる502AT-11 が

4.95kΩのプルアップ(実際は10kΩx2の並列)で使用されていました。

今回の試作では抵抗値が 10.0kΩの 103AT-11 が

5.1kΩのプルアップで使用されていますので、係数を合わせるために

SMTC502AT-11 のコンストラクタを

R0 = 10.0

R1 = 5.1

B = 3435

T0 = 298.15

で呼ぶように変更しました。

edge_utils/KL25Z_SystemInit.c@1:6c54dc8acf96, 2018-04-24 (annotated)

- Committer:

- Rhyme

- Date:

- Tue Apr 24 12:18:10 2018 +0000

- Revision:

- 1:6c54dc8acf96

- Parent:

- 0:0b6732b53bf4

to adjust with 103AT-11 with 5.1k pull-up, the constructor of 502AT-11 is called with R0=10.0, R1=5.1, B=3435, T0=298.15

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| Rhyme | 0:0b6732b53bf4 | 1 | #if defined (TARGET_KL25Z) |

| Rhyme | 0:0b6732b53bf4 | 2 | /* |

| Rhyme | 0:0b6732b53bf4 | 3 | ** ################################################################### |

| Rhyme | 0:0b6732b53bf4 | 4 | ** Processor: MKL25Z128VLK4 |

| Rhyme | 0:0b6732b53bf4 | 5 | ** Compilers: ARM Compiler |

| Rhyme | 0:0b6732b53bf4 | 6 | ** Freescale C/C++ for Embedded ARM |

| Rhyme | 0:0b6732b53bf4 | 7 | ** GNU C Compiler |

| Rhyme | 0:0b6732b53bf4 | 8 | ** IAR ANSI C/C++ Compiler for ARM |

| Rhyme | 0:0b6732b53bf4 | 9 | ** |

| Rhyme | 0:0b6732b53bf4 | 10 | ** Reference manual: KL25RM, Rev.1, Jun 2012 |

| Rhyme | 0:0b6732b53bf4 | 11 | ** Version: rev. 1.1, 2012-06-21 |

| Rhyme | 0:0b6732b53bf4 | 12 | ** |

| Rhyme | 0:0b6732b53bf4 | 13 | ** Abstract: |

| Rhyme | 0:0b6732b53bf4 | 14 | ** Provides a system configuration function and a global variable that |

| Rhyme | 0:0b6732b53bf4 | 15 | ** contains the system frequency. It configures the device and initializes |

| Rhyme | 0:0b6732b53bf4 | 16 | ** the oscillator (PLL) that is part of the microcontroller device. |

| Rhyme | 0:0b6732b53bf4 | 17 | ** |

| Rhyme | 0:0b6732b53bf4 | 18 | ** Copyright: 2012 Freescale Semiconductor, Inc. All Rights Reserved. |

| Rhyme | 0:0b6732b53bf4 | 19 | ** |

| Rhyme | 0:0b6732b53bf4 | 20 | ** http: www.freescale.com |

| Rhyme | 0:0b6732b53bf4 | 21 | ** mail: support@freescale.com |

| Rhyme | 0:0b6732b53bf4 | 22 | ** |

| Rhyme | 0:0b6732b53bf4 | 23 | ** Revisions: |

| Rhyme | 0:0b6732b53bf4 | 24 | ** - rev. 1.0 (2012-06-13) |

| Rhyme | 0:0b6732b53bf4 | 25 | ** Initial version. |

| Rhyme | 0:0b6732b53bf4 | 26 | ** - rev. 1.1 (2012-06-21) |

| Rhyme | 0:0b6732b53bf4 | 27 | ** Update according to reference manual rev. 1. |

| Rhyme | 0:0b6732b53bf4 | 28 | ** |

| Rhyme | 0:0b6732b53bf4 | 29 | ** ################################################################### |

| Rhyme | 0:0b6732b53bf4 | 30 | */ |

| Rhyme | 0:0b6732b53bf4 | 31 | |

| Rhyme | 0:0b6732b53bf4 | 32 | /** |

| Rhyme | 0:0b6732b53bf4 | 33 | * @file MKL25Z4 |

| Rhyme | 0:0b6732b53bf4 | 34 | * @version 1.1 |

| Rhyme | 0:0b6732b53bf4 | 35 | * @date 2012-06-21 |

| Rhyme | 0:0b6732b53bf4 | 36 | * @brief Device specific configuration file for MKL25Z4 (implementation file) |

| Rhyme | 0:0b6732b53bf4 | 37 | * |

| Rhyme | 0:0b6732b53bf4 | 38 | * Provides a system configuration function and a global variable that contains |

| Rhyme | 0:0b6732b53bf4 | 39 | * the system frequency. It configures the device and initializes the oscillator |

| Rhyme | 0:0b6732b53bf4 | 40 | * (PLL) that is part of the microcontroller device. |

| Rhyme | 0:0b6732b53bf4 | 41 | */ |

| Rhyme | 0:0b6732b53bf4 | 42 | |

| Rhyme | 0:0b6732b53bf4 | 43 | #include <stdint.h> |

| Rhyme | 0:0b6732b53bf4 | 44 | #include "MKL25Z4.h" |

| Rhyme | 0:0b6732b53bf4 | 45 | |

| Rhyme | 0:0b6732b53bf4 | 46 | //MODIFICATION: We DO want watchdog, uC default after reset is enabled with timeout=1024ms (2^10*LPO=1KHz) |

| Rhyme | 0:0b6732b53bf4 | 47 | //#define DISABLE_WDOG 1 |

| Rhyme | 0:0b6732b53bf4 | 48 | |

| Rhyme | 0:0b6732b53bf4 | 49 | #define CLOCK_SETUP 1 |

| Rhyme | 0:0b6732b53bf4 | 50 | /* Predefined clock setups |

| Rhyme | 0:0b6732b53bf4 | 51 | 0 ... Multipurpose Clock Generator (MCG) in FLL Engaged Internal (FEI) mode |

| Rhyme | 0:0b6732b53bf4 | 52 | Reference clock source for MCG module is the slow internal clock source 32.768kHz |

| Rhyme | 0:0b6732b53bf4 | 53 | Core clock = 41.94MHz, BusClock = 13.98MHz |

| Rhyme | 0:0b6732b53bf4 | 54 | 1 ... Multipurpose Clock Generator (MCG) in PLL Engaged External (PEE) mode |

| Rhyme | 0:0b6732b53bf4 | 55 | Reference clock source for MCG module is an external crystal 8MHz |

| Rhyme | 0:0b6732b53bf4 | 56 | Core clock = 48MHz, BusClock = 24MHz |

| Rhyme | 0:0b6732b53bf4 | 57 | 2 ... Multipurpose Clock Generator (MCG) in Bypassed Low Power External (BLPE) mode |

| Rhyme | 0:0b6732b53bf4 | 58 | Core clock/Bus clock derived directly from an external crystal 8MHz with no multiplication |

| Rhyme | 0:0b6732b53bf4 | 59 | Core clock = 8MHz, BusClock = 8MHz |

| Rhyme | 0:0b6732b53bf4 | 60 | 3 ... Multipurpose Clock Generator (MCG) in FLL Engaged External (FEE) mode |

| Rhyme | 0:0b6732b53bf4 | 61 | Reference clock source for MCG module is an external crystal 32.768kHz |

| Rhyme | 0:0b6732b53bf4 | 62 | Core clock = 47.97MHz, BusClock = 23.98MHz |

| Rhyme | 0:0b6732b53bf4 | 63 | This setup sets the RTC to be driven by the MCU clock directly without the need of an external source. |

| Rhyme | 0:0b6732b53bf4 | 64 | RTC register values are retained when MCU is reset although there will be a slight (mSec's)loss of time |

| Rhyme | 0:0b6732b53bf4 | 65 | accuracy durring the reset period. RTC will reset on power down. |

| Rhyme | 0:0b6732b53bf4 | 66 | */ |

| Rhyme | 0:0b6732b53bf4 | 67 | |

| Rhyme | 0:0b6732b53bf4 | 68 | /*---------------------------------------------------------------------------- |

| Rhyme | 0:0b6732b53bf4 | 69 | Define clock source values |

| Rhyme | 0:0b6732b53bf4 | 70 | *----------------------------------------------------------------------------*/ |

| Rhyme | 0:0b6732b53bf4 | 71 | #if (CLOCK_SETUP == 0) |

| Rhyme | 0:0b6732b53bf4 | 72 | #define CPU_XTAL_CLK_HZ 8000000u /* Value of the external crystal or oscillator clock frequency in Hz */ |

| Rhyme | 0:0b6732b53bf4 | 73 | #define CPU_INT_SLOW_CLK_HZ 32768u /* Value of the slow internal oscillator clock frequency in Hz */ |

| Rhyme | 0:0b6732b53bf4 | 74 | #define CPU_INT_FAST_CLK_HZ 4000000u /* Value of the fast internal oscillator clock frequency in Hz */ |

| Rhyme | 0:0b6732b53bf4 | 75 | #define DEFAULT_SYSTEM_CLOCK 41943040u /* Default System clock value */ |

| Rhyme | 0:0b6732b53bf4 | 76 | #elif (CLOCK_SETUP == 1) |

| Rhyme | 0:0b6732b53bf4 | 77 | #define CPU_XTAL_CLK_HZ 8000000u /* Value of the external crystal or oscillator clock frequency in Hz */ |

| Rhyme | 0:0b6732b53bf4 | 78 | #define CPU_INT_SLOW_CLK_HZ 32768u /* Value of the slow internal oscillator clock frequency in Hz */ |

| Rhyme | 0:0b6732b53bf4 | 79 | #define CPU_INT_FAST_CLK_HZ 4000000u /* Value of the fast internal oscillator clock frequency in Hz */ |

| Rhyme | 0:0b6732b53bf4 | 80 | #define DEFAULT_SYSTEM_CLOCK 48000000u /* Default System clock value */ |

| Rhyme | 0:0b6732b53bf4 | 81 | #elif (CLOCK_SETUP == 2) |

| Rhyme | 0:0b6732b53bf4 | 82 | #define CPU_XTAL_CLK_HZ 8000000u /* Value of the external crystal or oscillator clock frequency in Hz */ |

| Rhyme | 0:0b6732b53bf4 | 83 | #define CPU_INT_SLOW_CLK_HZ 32768u /* Value of the slow internal oscillator clock frequency in Hz */ |

| Rhyme | 0:0b6732b53bf4 | 84 | #define CPU_INT_FAST_CLK_HZ 4000000u /* Value of the fast internal oscillator clock frequency in Hz */ |

| Rhyme | 0:0b6732b53bf4 | 85 | #define DEFAULT_SYSTEM_CLOCK 8000000u /* Default System clock value */ |

| Rhyme | 0:0b6732b53bf4 | 86 | #elif (CLOCK_SETUP == 3) |

| Rhyme | 0:0b6732b53bf4 | 87 | #define CPU_XTAL_CLK_HZ 32768u /* Value of the external crystal or oscillator clock frequency in Hz */ |

| Rhyme | 0:0b6732b53bf4 | 88 | #define CPU_INT_SLOW_CLK_HZ 32768u /* Value of the slow internal oscillator clock frequency in Hz */ |

| Rhyme | 0:0b6732b53bf4 | 89 | #define CPU_INT_FAST_CLK_HZ 4000000u /* Value of the fast internal oscillator clock frequency in Hz */ |

| Rhyme | 0:0b6732b53bf4 | 90 | #define DEFAULT_SYSTEM_CLOCK 47972352u /* Default System clock value */ |

| Rhyme | 0:0b6732b53bf4 | 91 | #endif /* (CLOCK_SETUP == 3) */ |

| Rhyme | 0:0b6732b53bf4 | 92 | |

| Rhyme | 0:0b6732b53bf4 | 93 | /* ---------------------------------------------------------------------------- |

| Rhyme | 0:0b6732b53bf4 | 94 | -- Core clock |

| Rhyme | 0:0b6732b53bf4 | 95 | ---------------------------------------------------------------------------- */ |

| Rhyme | 0:0b6732b53bf4 | 96 | |

| Rhyme | 0:0b6732b53bf4 | 97 | //MODIFICATION: That vartiable already exists |

| Rhyme | 0:0b6732b53bf4 | 98 | // uint32_t SystemCoreClock = DEFAULT_SYSTEM_CLOCK; |

| Rhyme | 0:0b6732b53bf4 | 99 | |

| Rhyme | 0:0b6732b53bf4 | 100 | /* ---------------------------------------------------------------------------- |

| Rhyme | 0:0b6732b53bf4 | 101 | -- SystemInit() |

| Rhyme | 0:0b6732b53bf4 | 102 | ---------------------------------------------------------------------------- */ |

| Rhyme | 0:0b6732b53bf4 | 103 | |

| Rhyme | 0:0b6732b53bf4 | 104 | void $Sub$$SystemInit (void) { |

| Rhyme | 0:0b6732b53bf4 | 105 | |

| Rhyme | 0:0b6732b53bf4 | 106 | //MODIFICATION: |

| Rhyme | 0:0b6732b53bf4 | 107 | // That variable already exists, we set it here |

| Rhyme | 0:0b6732b53bf4 | 108 | SystemCoreClock = DEFAULT_SYSTEM_CLOCK; |

| Rhyme | 0:0b6732b53bf4 | 109 | // We want visual indication of boot time with red LED on |

| Rhyme | 0:0b6732b53bf4 | 110 | //TODO |

| Rhyme | 0:0b6732b53bf4 | 111 | |

| Rhyme | 0:0b6732b53bf4 | 112 | #if (DISABLE_WDOG) |

| Rhyme | 0:0b6732b53bf4 | 113 | /* Disable the WDOG module */ |

| Rhyme | 0:0b6732b53bf4 | 114 | /* SIM_COPC: COPT=0,COPCLKS=0,COPW=0 */ |

| Rhyme | 0:0b6732b53bf4 | 115 | SIM->COPC = (uint32_t)0x00u; |

| Rhyme | 0:0b6732b53bf4 | 116 | #endif /* (DISABLE_WDOG) */ |

| Rhyme | 0:0b6732b53bf4 | 117 | #if (CLOCK_SETUP == 0) |

| Rhyme | 0:0b6732b53bf4 | 118 | /* SIM->CLKDIV1: OUTDIV1=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,OUTDIV4=2,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */ |

| Rhyme | 0:0b6732b53bf4 | 119 | SIM->CLKDIV1 = (uint32_t)0x00020000UL; /* Update system prescalers */ |

| Rhyme | 0:0b6732b53bf4 | 120 | /* Switch to FEI Mode */ |

| Rhyme | 0:0b6732b53bf4 | 121 | /* MCG->C1: CLKS=0,FRDIV=0,IREFS=1,IRCLKEN=1,IREFSTEN=0 */ |

| Rhyme | 0:0b6732b53bf4 | 122 | MCG->C1 = (uint8_t)0x06U; |

| Rhyme | 0:0b6732b53bf4 | 123 | /* MCG_C2: LOCRE0=0,??=0,RANGE0=0,HGO0=0,EREFS0=0,LP=0,IRCS=0 */ |

| Rhyme | 0:0b6732b53bf4 | 124 | MCG->C2 = (uint8_t)0x00U; |

| Rhyme | 0:0b6732b53bf4 | 125 | /* MCG->C4: DMX32=0,DRST_DRS=1 */ |

| Rhyme | 0:0b6732b53bf4 | 126 | MCG->C4 = (uint8_t)((MCG->C4 & (uint8_t)~(uint8_t)0xC0U) | (uint8_t)0x20U); |

| Rhyme | 0:0b6732b53bf4 | 127 | /* OSC0->CR: ERCLKEN=1,??=0,EREFSTEN=0,??=0,SC2P=0,SC4P=0,SC8P=0,SC16P=0 */ |

| Rhyme | 0:0b6732b53bf4 | 128 | OSC0->CR = (uint8_t)0x80U; |

| Rhyme | 0:0b6732b53bf4 | 129 | /* MCG->C5: ??=0,PLLCLKEN0=0,PLLSTEN0=0,PRDIV0=0 */ |

| Rhyme | 0:0b6732b53bf4 | 130 | MCG->C5 = (uint8_t)0x00U; |

| Rhyme | 0:0b6732b53bf4 | 131 | /* MCG->C6: LOLIE0=0,PLLS=0,CME0=0,VDIV0=0 */ |

| Rhyme | 0:0b6732b53bf4 | 132 | MCG->C6 = (uint8_t)0x00U; |

| Rhyme | 0:0b6732b53bf4 | 133 | while((MCG->S & MCG_S_IREFST_MASK) == 0x00U) { /* Check that the source of the FLL reference clock is the internal reference clock. */ |

| Rhyme | 0:0b6732b53bf4 | 134 | } |

| Rhyme | 0:0b6732b53bf4 | 135 | while((MCG->S & 0x0CU) != 0x00U) { /* Wait until output of the FLL is selected */ |

| Rhyme | 0:0b6732b53bf4 | 136 | } |

| Rhyme | 0:0b6732b53bf4 | 137 | #elif (CLOCK_SETUP == 1) |

| Rhyme | 0:0b6732b53bf4 | 138 | /* SIM->SCGC5: PORTA=1 */ |

| Rhyme | 0:0b6732b53bf4 | 139 | SIM->SCGC5 |= (uint32_t)0x0200UL; /* Enable clock gate for ports to enable pin routing */ |

| Rhyme | 0:0b6732b53bf4 | 140 | /* SIM->CLKDIV1: OUTDIV1=1,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,OUTDIV4=1,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */ |

| Rhyme | 0:0b6732b53bf4 | 141 | SIM->CLKDIV1 = (uint32_t)0x10010000UL; /* Update system prescalers */ |

| Rhyme | 0:0b6732b53bf4 | 142 | /* PORTA->PCR18: ISF=0,MUX=0 */ |

| Rhyme | 0:0b6732b53bf4 | 143 | PORTA->PCR[18] &= (uint32_t)~0x01000700UL; |

| Rhyme | 0:0b6732b53bf4 | 144 | /* PORTA->PCR19: ISF=0,MUX=0 */ |

| Rhyme | 0:0b6732b53bf4 | 145 | PORTA->PCR[19] &= (uint32_t)~0x01000700UL; |

| Rhyme | 0:0b6732b53bf4 | 146 | /* Switch to FBE Mode */ |

| Rhyme | 0:0b6732b53bf4 | 147 | /* OSC0->CR: ERCLKEN=1,??=0,EREFSTEN=0,??=0,SC2P=1,SC4P=0,SC8P=0,SC16P=1 */ |

| Rhyme | 0:0b6732b53bf4 | 148 | OSC0->CR = (uint8_t)0x89U; |

| Rhyme | 0:0b6732b53bf4 | 149 | /* MCG->C2: LOCRE0=0,??=0,RANGE0=2,HGO0=0,EREFS0=1,LP=0,IRCS=0 */ |

| Rhyme | 0:0b6732b53bf4 | 150 | MCG->C2 = (uint8_t)0x24U; |

| Rhyme | 0:0b6732b53bf4 | 151 | /* MCG->C1: CLKS=2,FRDIV=3,IREFS=0,IRCLKEN=1,IREFSTEN=0 */ |

| Rhyme | 0:0b6732b53bf4 | 152 | MCG->C1 = (uint8_t)0x9AU; |

| Rhyme | 0:0b6732b53bf4 | 153 | /* MCG->C4: DMX32=0,DRST_DRS=0 */ |

| Rhyme | 0:0b6732b53bf4 | 154 | MCG->C4 &= (uint8_t)~(uint8_t)0xE0U; |

| Rhyme | 0:0b6732b53bf4 | 155 | /* MCG->C5: ??=0,PLLCLKEN0=0,PLLSTEN0=0,PRDIV0=1 */ |

| Rhyme | 0:0b6732b53bf4 | 156 | MCG->C5 = (uint8_t)0x01U; |

| Rhyme | 0:0b6732b53bf4 | 157 | /* MCG->C6: LOLIE0=0,PLLS=0,CME0=0,VDIV0=0 */ |

| Rhyme | 0:0b6732b53bf4 | 158 | MCG->C6 = (uint8_t)0x00U; |

| Rhyme | 0:0b6732b53bf4 | 159 | while((MCG->S & MCG_S_IREFST_MASK) != 0x00U) { /* Check that the source of the FLL reference clock is the external reference clock. */ |

| Rhyme | 0:0b6732b53bf4 | 160 | } |

| Rhyme | 0:0b6732b53bf4 | 161 | while((MCG->S & 0x0CU) != 0x08U) { /* Wait until external reference clock is selected as MCG output */ |

| Rhyme | 0:0b6732b53bf4 | 162 | } |

| Rhyme | 0:0b6732b53bf4 | 163 | /* Switch to PBE Mode */ |

| Rhyme | 0:0b6732b53bf4 | 164 | /* MCG->C6: LOLIE0=0,PLLS=1,CME0=0,VDIV0=0 */ |

| Rhyme | 0:0b6732b53bf4 | 165 | MCG->C6 = (uint8_t)0x40U; |

| Rhyme | 0:0b6732b53bf4 | 166 | while((MCG->S & 0x0CU) != 0x08U) { /* Wait until external reference clock is selected as MCG output */ |

| Rhyme | 0:0b6732b53bf4 | 167 | } |

| Rhyme | 0:0b6732b53bf4 | 168 | while((MCG->S & MCG_S_LOCK0_MASK) == 0x00U) { /* Wait until locked */ |

| Rhyme | 0:0b6732b53bf4 | 169 | } |

| Rhyme | 0:0b6732b53bf4 | 170 | /* Switch to PEE Mode */ |

| Rhyme | 0:0b6732b53bf4 | 171 | /* MCG->C1: CLKS=0,FRDIV=3,IREFS=0,IRCLKEN=1,IREFSTEN=0 */ |

| Rhyme | 0:0b6732b53bf4 | 172 | MCG->C1 = (uint8_t)0x1AU; |

| Rhyme | 0:0b6732b53bf4 | 173 | while((MCG->S & 0x0CU) != 0x0CU) { /* Wait until output of the PLL is selected */ |

| Rhyme | 0:0b6732b53bf4 | 174 | } |

| Rhyme | 0:0b6732b53bf4 | 175 | #elif (CLOCK_SETUP == 2) |

| Rhyme | 0:0b6732b53bf4 | 176 | /* SIM->SCGC5: PORTA=1 */ |

| Rhyme | 0:0b6732b53bf4 | 177 | SIM->SCGC5 |= (uint32_t)0x0200UL; /* Enable clock gate for ports to enable pin routing */ |

| Rhyme | 0:0b6732b53bf4 | 178 | /* SIM->CLKDIV1: OUTDIV1=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,OUTDIV4=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */ |

| Rhyme | 0:0b6732b53bf4 | 179 | SIM->CLKDIV1 = (uint32_t)0x00000000UL; /* Update system prescalers */ |

| Rhyme | 0:0b6732b53bf4 | 180 | /* PORTA->PCR18: ISF=0,MUX=0 */ |

| Rhyme | 0:0b6732b53bf4 | 181 | PORTA->PCR[18] &= (uint32_t)~0x01000700UL; |

| Rhyme | 0:0b6732b53bf4 | 182 | /* PORTA->PCR19: ISF=0,MUX=0 */ |

| Rhyme | 0:0b6732b53bf4 | 183 | PORTA->PCR[19] &= (uint32_t)~0x01000700UL; |

| Rhyme | 0:0b6732b53bf4 | 184 | /* Switch to FBE Mode */ |

| Rhyme | 0:0b6732b53bf4 | 185 | /* OSC0->CR: ERCLKEN=1,??=0,EREFSTEN=0,??=0,SC2P=1,SC4P=0,SC8P=0,SC16P=1 */ |

| Rhyme | 0:0b6732b53bf4 | 186 | OSC0->CR = (uint8_t)0x89U; |

| Rhyme | 0:0b6732b53bf4 | 187 | /* MCG->C2: LOCRE0=0,??=0,RANGE0=2,HGO0=0,EREFS0=1,LP=0,IRCS=0 */ |

| Rhyme | 0:0b6732b53bf4 | 188 | MCG->C2 = (uint8_t)0x24U; |

| Rhyme | 0:0b6732b53bf4 | 189 | /* MCG->C1: CLKS=2,FRDIV=3,IREFS=0,IRCLKEN=1,IREFSTEN=0 */ |

| Rhyme | 0:0b6732b53bf4 | 190 | MCG->C1 = (uint8_t)0x9AU; |

| Rhyme | 0:0b6732b53bf4 | 191 | /* MCG->C4: DMX32=0,DRST_DRS=0 */ |

| Rhyme | 0:0b6732b53bf4 | 192 | MCG->C4 &= (uint8_t)~(uint8_t)0xE0U; |

| Rhyme | 0:0b6732b53bf4 | 193 | /* MCG->C5: ??=0,PLLCLKEN0=0,PLLSTEN0=0,PRDIV0=0 */ |

| Rhyme | 0:0b6732b53bf4 | 194 | MCG->C5 = (uint8_t)0x00U; |

| Rhyme | 0:0b6732b53bf4 | 195 | /* MCG->C6: LOLIE0=0,PLLS=0,CME0=0,VDIV0=0 */ |

| Rhyme | 0:0b6732b53bf4 | 196 | MCG->C6 = (uint8_t)0x00U; |

| Rhyme | 0:0b6732b53bf4 | 197 | while((MCG->S & MCG_S_IREFST_MASK) != 0x00U) { /* Check that the source of the FLL reference clock is the external reference clock. */ |

| Rhyme | 0:0b6732b53bf4 | 198 | } |

| Rhyme | 0:0b6732b53bf4 | 199 | while((MCG->S & 0x0CU) != 0x08U) { /* Wait until external reference clock is selected as MCG output */ |

| Rhyme | 0:0b6732b53bf4 | 200 | } |

| Rhyme | 0:0b6732b53bf4 | 201 | /* Switch to BLPE Mode */ |

| Rhyme | 0:0b6732b53bf4 | 202 | /* MCG->C2: LOCRE0=0,??=0,RANGE0=2,HGO0=0,EREFS0=1,LP=1,IRCS=0 */ |

| Rhyme | 0:0b6732b53bf4 | 203 | MCG->C2 = (uint8_t)0x26U; |

| Rhyme | 0:0b6732b53bf4 | 204 | while((MCG->S & 0x0CU) != 0x08U) { /* Wait until external reference clock is selected as MCG output */ |

| Rhyme | 0:0b6732b53bf4 | 205 | } |

| Rhyme | 0:0b6732b53bf4 | 206 | #elif (CLOCK_SETUP == 3) |

| Rhyme | 0:0b6732b53bf4 | 207 | /* SIM->SCGC5: PORTA=1 */ |

| Rhyme | 0:0b6732b53bf4 | 208 | SIM->SCGC5 |= SIM_SCGC5_PORTA_MASK; /* Enable clock gate for ports to enable pin routing */ |

| Rhyme | 0:0b6732b53bf4 | 209 | /* SIM->CLKDIV1: OUTDIV1=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,OUTDIV4=1,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */ |

| Rhyme | 0:0b6732b53bf4 | 210 | SIM->CLKDIV1 = (SIM_CLKDIV1_OUTDIV1(0x00) | SIM_CLKDIV1_OUTDIV4(0x01)); /* Update system prescalers */ |

| Rhyme | 0:0b6732b53bf4 | 211 | /* PORTA->PCR[3]: ISF=0,MUX=0 */ |

| Rhyme | 0:0b6732b53bf4 | 212 | PORTA->PCR[3] &= (uint32_t)~(uint32_t)((PORT_PCR_ISF_MASK | PORT_PCR_MUX(0x07))); |

| Rhyme | 0:0b6732b53bf4 | 213 | /* PORTA->PCR[4]: ISF=0,MUX=0 */ |

| Rhyme | 0:0b6732b53bf4 | 214 | PORTA->PCR[4] &= (uint32_t)~(uint32_t)((PORT_PCR_ISF_MASK | PORT_PCR_MUX(0x07))); |

| Rhyme | 0:0b6732b53bf4 | 215 | /* Switch to FEE Mode */ |

| Rhyme | 0:0b6732b53bf4 | 216 | /* MCG->C2: LOCRE0=0,??=0,RANGE0=0,HGO0=0,EREFS0=1,LP=0,IRCS=0 */ |

| Rhyme | 0:0b6732b53bf4 | 217 | MCG->C2 = (MCG_C2_RANGE0(0x00) | MCG_C2_EREFS0_MASK); |

| Rhyme | 0:0b6732b53bf4 | 218 | /* OSC0->CR: ERCLKEN=1,??=0,EREFSTEN=0,??=0,SC2P=0,SC4P=0,SC8P=0,SC16P=0 */ |

| Rhyme | 0:0b6732b53bf4 | 219 | OSC0->CR = OSC_CR_ERCLKEN_MASK | OSC_CR_SC16P_MASK | OSC_CR_SC4P_MASK | OSC_CR_SC2P_MASK; |

| Rhyme | 0:0b6732b53bf4 | 220 | /* MCG->C1: CLKS=0,FRDIV=0,IREFS=0,IRCLKEN=1,IREFSTEN=0 */ |

| Rhyme | 0:0b6732b53bf4 | 221 | MCG->C1 = (MCG_C1_CLKS(0x00) | MCG_C1_FRDIV(0x00) | MCG_C1_IRCLKEN_MASK); |

| Rhyme | 0:0b6732b53bf4 | 222 | /* MCG->C4: DMX32=1,DRST_DRS=1 */ |

| Rhyme | 0:0b6732b53bf4 | 223 | MCG->C4 = (uint8_t)((MCG->C4 & (uint8_t)~(uint8_t)( |

| Rhyme | 0:0b6732b53bf4 | 224 | MCG_C4_DRST_DRS(0x02) |

| Rhyme | 0:0b6732b53bf4 | 225 | )) | (uint8_t)( |

| Rhyme | 0:0b6732b53bf4 | 226 | MCG_C4_DMX32_MASK | |

| Rhyme | 0:0b6732b53bf4 | 227 | MCG_C4_DRST_DRS(0x01) |

| Rhyme | 0:0b6732b53bf4 | 228 | )); |

| Rhyme | 0:0b6732b53bf4 | 229 | while((MCG->S & MCG_S_IREFST_MASK) != 0x00U) { /* Check that the source of the FLL reference clock is the external reference clock. */ |

| Rhyme | 0:0b6732b53bf4 | 230 | } |

| Rhyme | 0:0b6732b53bf4 | 231 | while((MCG->S & 0x0CU) != 0x00U) { /* Wait until output of the FLL is selected */ |

| Rhyme | 0:0b6732b53bf4 | 232 | } |

| Rhyme | 0:0b6732b53bf4 | 233 | #endif /* (CLOCK_SETUP == 3) */ |

| Rhyme | 0:0b6732b53bf4 | 234 | } |

| Rhyme | 0:0b6732b53bf4 | 235 | #endif // TARGET_KL25Z |

La Suno

La Suno