Important changes to forums and questions

All forums and questions are now archived. To start a new conversation or read the latest updates go to forums.mbed.com.

10 years, 11 months ago.

GR-PEACH and cache

Hello,

1. What is the current state of the L1 Data, L1 Instruction and L2 caches in the GR-PEACH?

2. How can I tell if Data and/or Instruction cache is turned on or not?

3. Does the user have the ability to enable/disable Data cache?

4. Does the user have the ability to enable/disable Instruction cache?

5. Can L1 caches be enabled/disabled independently from L2 cache?

Regards,

...kevin

Question relating to:

2 Answers

10 years, 11 months ago.

1.

L1 cache and L2 cache are enabled.

mbed-src/targets/cmsis/TARGET_RENESAS/TARGET_RZ_A1H/system_MBRZA1H.c

void InitMemorySubsystem(void) {

........

/* After MMU is enabled and data has been invalidated, enable caches and BTAC */

__enable_caches();

__enable_btac();

/* If present, you may also need to Invalidate and Enable L2 cache here */

l2_id = PL310_GetID();

if (l2_id)

{

PL310_InvAllByWay();

PL310_Enable();

}

2.

It can be checked by the following code.

if ((__get_SCTLR() & (1 << 12)) != 0) {

printf("Instruction cache is enabled.\n");

} else {

printf("Instruction cache is disabled.\n");

}

if ((__get_SCTLR() & (1 << 2)) != 0) {

printf("Data cache is enabled.\n");

} else {

printf("Data cache is disabled.\n");

}

3. 4.

Yes. Please change it as follows.

Data cache and Instruction cache are enabled. (default)

system_MBRZA1H.c

void InitMemorySubsystem(void) {

........

/* After MMU is enabled and data has been invalidated, enable caches and BTAC */

__enable_caches();

__enable_btac();

........

Instruction cache only.

system_MBRZA1H.c

void InitMemorySubsystem(void) {

........

/* After MMU is enabled and data has been invalidated, enable caches and BTAC */

// __enable_caches();

__set_SCTLR( __get_SCTLR() | (1 << 12)); // Set I bit 12 to enable I Cache (Instruction)

__enable_btac();

........

Data cache only.

system_MBRZA1H.c

void InitMemorySubsystem(void) {

........

/* After MMU is enabled and data has been invalidated, enable caches and BTAC */

// __enable_caches();

__set_SCTLR( __get_SCTLR() | (1 << 2)); // Set C bit 2 to enable D Cache (Data)

__enable_btac();

........

5.

Yes. Please change it as follows.

L2 cache is enabled. (default)

system_MBRZA1H.c

void InitMemorySubsystem(void) {

........

/* If present, you may also need to Invalidate and Enable L2 cache here */

l2_id = PL310_GetID();

if (l2_id)

{

PL310_InvAllByWay();

PL310_Enable();

}

L2 cache is disabled.

system_MBRZA1H.c

void InitMemorySubsystem(void) {

........

/* If present, you may also need to Invalidate and Enable L2 cache here */

// l2_id = PL310_GetID();

// if (l2_id)

// {

// PL310_InvAllByWay();

// PL310_Enable();

// }

Please use mbed-src lib instead of mbed lib.

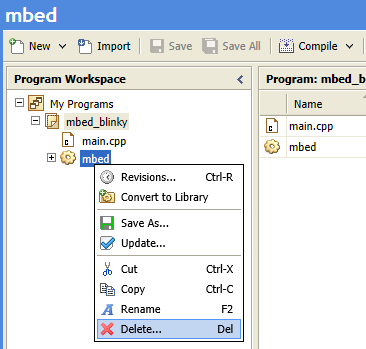

- Select "mbed" library and delete it as shown below.

- Import mbed-src library.

Import librarymbed-src

mbed library sources

- Check "Update all libraries to the latest version".

- Get the source code by clicking "Import" button.

Hi Daiki,

I was using mbed-src_GR-PEACH_rev_b, not the mbed library

I had to keep mbed-src_GR-PEACH_rev_b . mbed-src from your link above compiled ok, but the GR-PEACH board would not even start. Is it because I have a rev B board?

1. When I disabled L2 cache only, the erroneous numbers declined significantly, but not completely.

2. When I disabled all caches, the erroneous numbers got way worse!!!

3. When I enable only the Instruction cache, like 2. above, the erroneous numbers got way worse.

4. When I enable only the Data cache, like 2. and 3. above, the erroneous numbers got way worse.

5. When I enable the Data and L2 caches (Instruction cache disabled), the erroneous numbers were about the same as when all caches are enabled.

6. When I enable the Instruction and L2 caches (Data cache disabled), the erroneous numbers were about the same as when all caches are enabled.

7. When I disabled data and instruction caches, but L2 cache enabled, the erroneous numbers were about the same as with all caches enabled.

8. The printf statements (from above) detect the enable/disable caches correctly.

Q1. Is there an equivalent printf available for detecting L2 cache enabled/disabled?

Q2: Is there a way to disable the internal FPU and use an external floating point library?

posted by 08 May 2015For the rev.B board, it should work by the following way.

・Replace your "mbed-src\taregets\hal\TARGET_RENESAS\TARGET_RZ_A1H\PinNames.h" with PinNames.h for GR-PEACH rev.B.

A1.

To check whether L2 cache is enabled, you need to change some files.

Add to mbed-src/targets/cmsis/TARGET_RENESAS/TARGET_RZ_A1H/pl310.h

extern int PL310_GetEnable (void);

Add to mbed-src/targets/cmsis/TARGET_RENESAS/TARGET_RZ_A1H/pl310.c

//Get L2 cache enable bit

int PL310_GetEnable (void) {

return PL310->CONTROL;

}

An example of main.cpp

#include "mbed.h"

#include "pl310.h"

DigitalOut myled(LED1);

int main() {

while(1) {

myled = 1;

wait(0.2);

myled = 0;

wait(0.2);

if (( PL310_GetEnable() & 0x01 ) != 0 ) {

printf ("L2 cache is enabled.\n");

} else {

printf ("L2 cache is disabled.\n");

}

}

}

A2.

In online compiler, you can not use external floating point library because compile options are fixed.

If you export your program and use offline compiler, you can change compile options and use external floating point library.

10 years, 11 months ago.

Without seeing the code its difficult to know but my first thought would be uninitialized variables. Don't forget that stack variables are not initialized by default so will contain what was left by the previous call. The two working boards use Cortex CPUs so it might well be that due to their similarities that you are getting consistent good values for the uninitialized variables where as on the GR-PEACH with its A9 CPU is producing a different stack usage and inconsistent results.

While I have seen many instances of uninitialized variables causing inconsistent results, I've never seen problems caused by caching or faulty hardware.

Uninitialized variables is something I do not do (at least I don't think I do). Not to say that libraries I import may have done so. I've been writing code on mbed since 2009. Granted, they are all Cortex M cores.

By uninitialized, what specifically do you mean? I am not specifically pushing popping items from the stack. Can you give a couple codes examples of what this issue could be or what I should be looking for?

posted by 11 May 2015

The reason I'm asking, is that I am seeing strange math behavior. Occasionally, when performing calculations on data, I get a "nan", "inf", zero, or results that are way out of range. So far, I have seen this only on floating numbers. It doesn't happen often, maybe one bad result every couple of minutes with calculations happening every second. If I detect the error and re-run the calculation, the results come back normal. The phenomena even happens when copying a floating number from an array to a variable. This NEVER happens with a mbed K64F or KL25Z.

Perhaps you may have an API or driver that can manipulate cache functions (enable, disable, flush, etc.) that I can play with so I can look into this further.

Regards,

...kevin

posted by Kevin Braun 01 May 2015