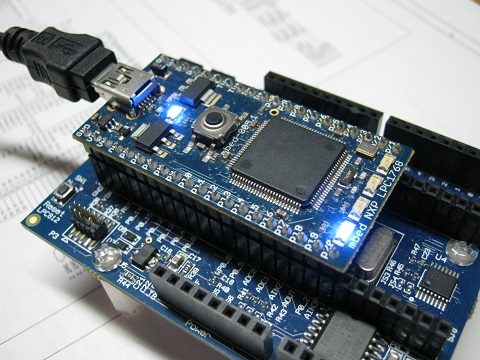

mbed LPC812 emulator pre-alpha version

Dependencies: BaseV6M mbed F12RFileSystem F32RFileSystem ROMSLOT SDStorage

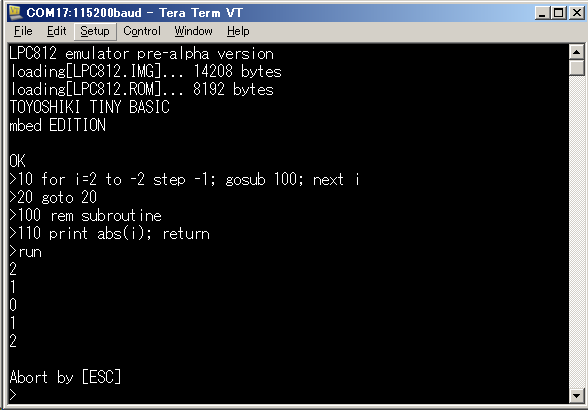

Example

TTB_mbed_LPC812.bin save as "LPC812.IMG" .

internal boot rom image(0x1fff0000-0x1fff1fff) save as "LPC812.ROM".

Tested programs

- TTB_mbed - TOYOSHIKI TINY BASIC mbed Edition

- mbed_blinky - LED1 blinky

EMU81x.h@5:f22e2df90a70, 2016-04-09 (annotated)

- Committer:

- va009039

- Date:

- Sat Apr 09 07:59:56 2016 +0000

- Revision:

- 5:f22e2df90a70

- Parent:

- 2:3f3637d7c2bc

add Nucleo-L152RE.

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| va009039 |

2:3f3637d7c2bc | 1 | // EMU81x.h 2015/8/12 |

| va009039 |

1:913dfd59e25a | 2 | #pragma once |

| va009039 |

1:913dfd59e25a | 3 | #include "BaseV6M.h" |

| va009039 |

1:913dfd59e25a | 4 | #include "EMUInterface.h" |

| va009039 |

1:913dfd59e25a | 5 | |

| va009039 |

1:913dfd59e25a | 6 | class EMU81x; |

| va009039 |

1:913dfd59e25a | 7 | |

| va009039 |

1:913dfd59e25a | 8 | class EMU81x_USART { |

| va009039 |

1:913dfd59e25a | 9 | public: |

| va009039 |

1:913dfd59e25a | 10 | EMU81x_USART(EMU81x& mcu, int ch); |

| va009039 |

1:913dfd59e25a | 11 | void poke32(uint32_t a, uint32_t d); |

| va009039 |

1:913dfd59e25a | 12 | uint32_t peek32(uint32_t a); |

| va009039 |

1:913dfd59e25a | 13 | |

| va009039 |

1:913dfd59e25a | 14 | private: |

| va009039 |

1:913dfd59e25a | 15 | EMU81x& mcu; |

| va009039 |

1:913dfd59e25a | 16 | int ch; |

| va009039 |

2:3f3637d7c2bc | 17 | uint32_t CFG; |

| va009039 |

2:3f3637d7c2bc | 18 | uint32_t STAT; |

| va009039 |

2:3f3637d7c2bc | 19 | uint32_t INTENCLR; |

| va009039 |

2:3f3637d7c2bc | 20 | uint32_t BRG; |

| va009039 |

1:913dfd59e25a | 21 | }; |

| va009039 |

1:913dfd59e25a | 22 | |

| va009039 |

1:913dfd59e25a | 23 | class EMU81x_MRT { |

| va009039 |

1:913dfd59e25a | 24 | public: |

| va009039 |

1:913dfd59e25a | 25 | EMU81x_MRT(); |

| va009039 |

1:913dfd59e25a | 26 | void clock_in(uint32_t n = 1); |

| va009039 |

1:913dfd59e25a | 27 | void poke32(uint32_t a, uint32_t d); |

| va009039 |

1:913dfd59e25a | 28 | uint32_t peek32(uint32_t a); |

| va009039 |

1:913dfd59e25a | 29 | private: |

| va009039 |

1:913dfd59e25a | 30 | uint32_t timer0; |

| va009039 |

1:913dfd59e25a | 31 | }; |

| va009039 |

1:913dfd59e25a | 32 | |

| va009039 |

1:913dfd59e25a | 33 | class EMU81x_IOCON { |

| va009039 |

1:913dfd59e25a | 34 | public: |

| va009039 |

1:913dfd59e25a | 35 | EMU81x_IOCON(); |

| va009039 |

1:913dfd59e25a | 36 | void poke32(uint32_t a, uint32_t d); |

| va009039 |

1:913dfd59e25a | 37 | uint32_t peek32(uint32_t a); |

| va009039 |

1:913dfd59e25a | 38 | |

| va009039 |

1:913dfd59e25a | 39 | private: |

| va009039 |

2:3f3637d7c2bc | 40 | uint32_t PIO0_17; |

| va009039 |

2:3f3637d7c2bc | 41 | uint32_t PIO0_13; |

| va009039 |

2:3f3637d7c2bc | 42 | uint32_t PIO0_12; |

| va009039 |

2:3f3637d7c2bc | 43 | uint32_t PIO0_5; |

| va009039 |

2:3f3637d7c2bc | 44 | uint32_t PIO0_4; |

| va009039 |

2:3f3637d7c2bc | 45 | uint32_t PIO0_3; |

| va009039 |

2:3f3637d7c2bc | 46 | uint32_t PIO0_2; |

| va009039 |

2:3f3637d7c2bc | 47 | uint32_t PIO0_11; |

| va009039 |

2:3f3637d7c2bc | 48 | uint32_t PIO0_10; |

| va009039 |

2:3f3637d7c2bc | 49 | uint32_t PIO0_16; |

| va009039 |

2:3f3637d7c2bc | 50 | uint32_t PIO0_15; |

| va009039 |

2:3f3637d7c2bc | 51 | uint32_t PIO0_1; |

| va009039 |

2:3f3637d7c2bc | 52 | uint32_t PIO0_9; |

| va009039 |

2:3f3637d7c2bc | 53 | uint32_t PIO0_8; |

| va009039 |

2:3f3637d7c2bc | 54 | uint32_t PIO0_7; |

| va009039 |

2:3f3637d7c2bc | 55 | uint32_t PIO0_6; |

| va009039 |

2:3f3637d7c2bc | 56 | uint32_t PIO0_0; |

| va009039 |

2:3f3637d7c2bc | 57 | uint32_t PIO0_14; |

| va009039 |

1:913dfd59e25a | 58 | }; |

| va009039 |

1:913dfd59e25a | 59 | |

| va009039 |

1:913dfd59e25a | 60 | class EMU81x_SYSCON { |

| va009039 |

1:913dfd59e25a | 61 | public: |

| va009039 |

1:913dfd59e25a | 62 | EMU81x_SYSCON(); |

| va009039 |

1:913dfd59e25a | 63 | void poke32(uint32_t a, uint32_t d); |

| va009039 |

1:913dfd59e25a | 64 | uint32_t peek32(uint32_t a); |

| va009039 |

1:913dfd59e25a | 65 | }; |

| va009039 |

1:913dfd59e25a | 66 | |

| va009039 |

1:913dfd59e25a | 67 | class EMU81x_SWM { |

| va009039 |

1:913dfd59e25a | 68 | public: |

| va009039 |

1:913dfd59e25a | 69 | EMU81x_SWM(); |

| va009039 |

1:913dfd59e25a | 70 | void poke32(uint32_t a, uint32_t d); |

| va009039 |

1:913dfd59e25a | 71 | uint32_t peek32(uint32_t a); |

| va009039 |

1:913dfd59e25a | 72 | |

| va009039 |

1:913dfd59e25a | 73 | private: |

| va009039 |

1:913dfd59e25a | 74 | uint32_t pinassign[9]; |

| va009039 |

1:913dfd59e25a | 75 | uint32_t pinenable0; |

| va009039 |

1:913dfd59e25a | 76 | }; |

| va009039 |

1:913dfd59e25a | 77 | |

| va009039 |

1:913dfd59e25a | 78 | class EMU81x_GPIO { |

| va009039 |

1:913dfd59e25a | 79 | public: |

| va009039 |

1:913dfd59e25a | 80 | EMU81x_GPIO(EMU81x& mcu); |

| va009039 |

1:913dfd59e25a | 81 | void poke32(uint32_t a, uint32_t d); |

| va009039 |

1:913dfd59e25a | 82 | uint32_t peek32(uint32_t a); |

| va009039 |

1:913dfd59e25a | 83 | |

| va009039 |

1:913dfd59e25a | 84 | private: |

| va009039 |

1:913dfd59e25a | 85 | uint32_t dir0; |

| va009039 |

1:913dfd59e25a | 86 | uint32_t data0; |

| va009039 |

1:913dfd59e25a | 87 | EMU81x& mcu; |

| va009039 |

1:913dfd59e25a | 88 | }; |

| va009039 |

1:913dfd59e25a | 89 | |

| va009039 |

1:913dfd59e25a | 90 | class EMU81x_I2C { |

| va009039 |

1:913dfd59e25a | 91 | public: |

| va009039 |

1:913dfd59e25a | 92 | EMU81x_I2C(EMU81x& mcu); |

| va009039 |

1:913dfd59e25a | 93 | void poke32(uint32_t a, uint32_t d); |

| va009039 |

1:913dfd59e25a | 94 | uint32_t peek32(uint32_t a); |

| va009039 |

1:913dfd59e25a | 95 | |

| va009039 |

1:913dfd59e25a | 96 | private: |

| va009039 |

1:913dfd59e25a | 97 | EMU81x& mcu; |

| va009039 |

1:913dfd59e25a | 98 | uint32_t cfg; |

| va009039 |

1:913dfd59e25a | 99 | int mststate; |

| va009039 |

1:913dfd59e25a | 100 | uint8_t mstdat; |

| va009039 |

1:913dfd59e25a | 101 | uint8_t i2c_addr; |

| va009039 |

1:913dfd59e25a | 102 | uint8_t i2c_data[16]; |

| va009039 |

1:913dfd59e25a | 103 | int i2c_pos; |

| va009039 |

1:913dfd59e25a | 104 | }; |

| va009039 |

1:913dfd59e25a | 105 | |

| va009039 |

1:913dfd59e25a | 106 | class EMU81x_SPI { |

| va009039 |

1:913dfd59e25a | 107 | public: |

| va009039 |

1:913dfd59e25a | 108 | EMU81x_SPI(EMU81x& mcu, int ch); |

| va009039 |

1:913dfd59e25a | 109 | void poke32(uint32_t a, uint32_t d); |

| va009039 |

1:913dfd59e25a | 110 | uint32_t peek32(uint32_t a); |

| va009039 |

1:913dfd59e25a | 111 | |

| va009039 |

1:913dfd59e25a | 112 | private: |

| va009039 |

1:913dfd59e25a | 113 | EMU81x& mcu; |

| va009039 |

1:913dfd59e25a | 114 | int ch; |

| va009039 |

1:913dfd59e25a | 115 | uint8_t rxdat; |

| va009039 |

1:913dfd59e25a | 116 | }; |

| va009039 |

1:913dfd59e25a | 117 | |

| va009039 |

1:913dfd59e25a | 118 | class EMU81x_NVIC { |

| va009039 |

1:913dfd59e25a | 119 | public: |

| va009039 |

1:913dfd59e25a | 120 | void poke32(uint32_t a, uint32_t d); |

| va009039 |

1:913dfd59e25a | 121 | |

| va009039 |

1:913dfd59e25a | 122 | private: |

| va009039 |

1:913dfd59e25a | 123 | uint32_t iser; |

| va009039 |

1:913dfd59e25a | 124 | }; |

| va009039 |

1:913dfd59e25a | 125 | |

| va009039 |

1:913dfd59e25a | 126 | class EMU81x_SCB { |

| va009039 |

1:913dfd59e25a | 127 | public: |

| va009039 |

1:913dfd59e25a | 128 | EMU81x_SCB(); |

| va009039 |

1:913dfd59e25a | 129 | void poke32(uint32_t a, uint32_t d); |

| va009039 |

1:913dfd59e25a | 130 | uint32_t peek32(uint32_t a); |

| va009039 |

1:913dfd59e25a | 131 | |

| va009039 |

1:913dfd59e25a | 132 | private: |

| va009039 |

1:913dfd59e25a | 133 | uint32_t vtor; |

| va009039 |

1:913dfd59e25a | 134 | }; |

| va009039 |

1:913dfd59e25a | 135 | |

| va009039 |

1:913dfd59e25a | 136 | class EMU81x : public EMUInterface, public BaseV6M { |

| va009039 |

1:913dfd59e25a | 137 | public: |

| va009039 |

1:913dfd59e25a | 138 | EMU81x(); |

| va009039 |

1:913dfd59e25a | 139 | virtual ~EMU81x(); |

| va009039 |

1:913dfd59e25a | 140 | void assign_flash(const uint8_t* addr) { flash = addr; } |

| va009039 |

1:913dfd59e25a | 141 | void assign_rom(const uint8_t* addr) { rom = addr; } |

| va009039 |

1:913dfd59e25a | 142 | void clock_in(uint32_t n); |

| va009039 |

1:913dfd59e25a | 143 | void trace(); |

| va009039 |

1:913dfd59e25a | 144 | |

| va009039 |

1:913dfd59e25a | 145 | protected: |

| va009039 |

1:913dfd59e25a | 146 | virtual void poke32(uint32_t a, uint32_t d); |

| va009039 |

1:913dfd59e25a | 147 | virtual uint32_t peek32(uint32_t a); |

| va009039 |

1:913dfd59e25a | 148 | virtual void poke8(uint32_t a, uint8_t b); |

| va009039 |

1:913dfd59e25a | 149 | virtual uint8_t peek8(uint32_t a); |

| va009039 |

1:913dfd59e25a | 150 | |

| va009039 |

1:913dfd59e25a | 151 | private: |

| va009039 |

1:913dfd59e25a | 152 | const uint8_t* flash; |

| va009039 |

1:913dfd59e25a | 153 | const uint8_t* rom; |

| va009039 |

1:913dfd59e25a | 154 | uint8_t* ram; |

| va009039 |

2:3f3637d7c2bc | 155 | EMU81x_USART _uart0; |

| va009039 |

2:3f3637d7c2bc | 156 | EMU81x_USART _uart1; |

| va009039 |

2:3f3637d7c2bc | 157 | EMU81x_USART _uart2; |

| va009039 |

1:913dfd59e25a | 158 | EMU81x_MRT mrt; |

| va009039 |

1:913dfd59e25a | 159 | EMU81x_IOCON iocon; |

| va009039 |

1:913dfd59e25a | 160 | EMU81x_SYSCON syscon; |

| va009039 |

1:913dfd59e25a | 161 | EMU81x_SWM swm; |

| va009039 |

1:913dfd59e25a | 162 | EMU81x_GPIO gpio; |

| va009039 |

2:3f3637d7c2bc | 163 | EMU81x_I2C _i2c; |

| va009039 |

2:3f3637d7c2bc | 164 | EMU81x_SPI _spi0; |

| va009039 |

2:3f3637d7c2bc | 165 | EMU81x_SPI _spi1; |

| va009039 |

1:913dfd59e25a | 166 | EMU81x_SCB scb; |

| va009039 |

1:913dfd59e25a | 167 | EMU81x_NVIC nvic; |

| va009039 |

1:913dfd59e25a | 168 | |

| va009039 |

1:913dfd59e25a | 169 | friend class EMU81x_USART; |

| va009039 |

1:913dfd59e25a | 170 | friend class EMU81x_GPIO; |

| va009039 |

1:913dfd59e25a | 171 | friend class EMU81x_I2C; |

| va009039 |

1:913dfd59e25a | 172 | friend class EMU81x_SPI; |

| va009039 |

1:913dfd59e25a | 173 | }; |