Fork of mbed-src file paths change. LPC1114FN28 use only.

Fork of mbed-src by

Information

この情報は2013/10/28時点での解決方法です。

現在はmbed-src、標準ライブラリで問題なくコンパイルが可能です。

・使う物

LPC1114FN28

mbed SDK

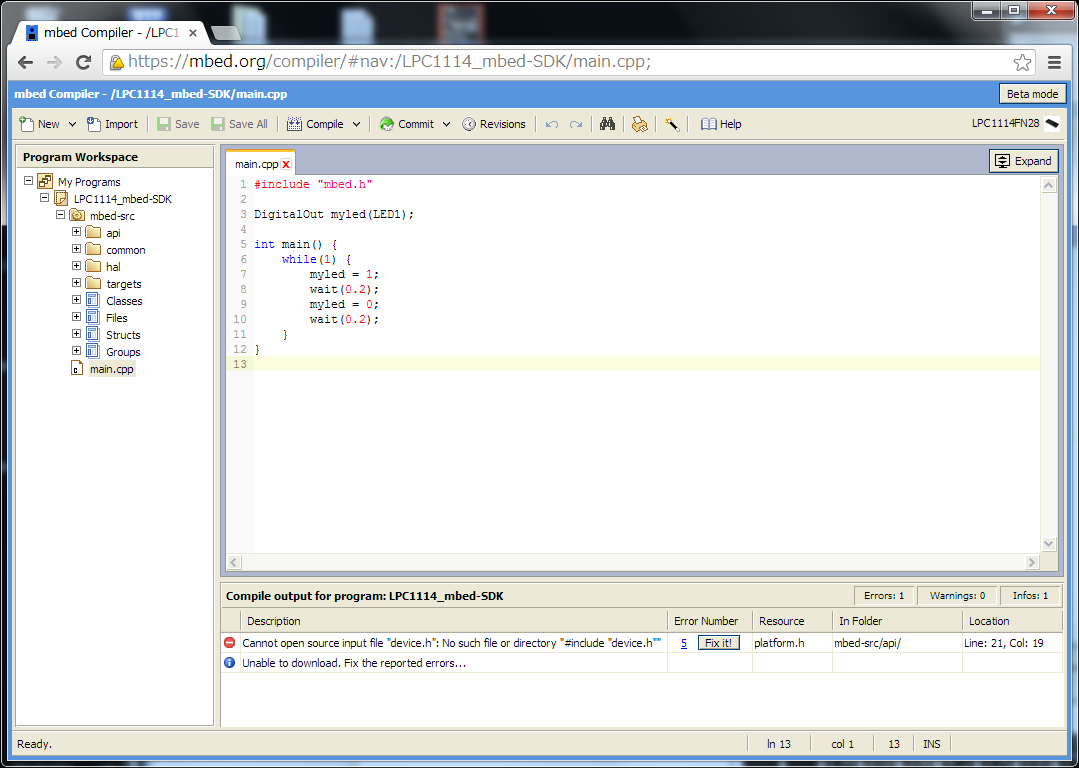

LPC1114FN28でmbed-SDKのLibraryを使うとCompile出来ない。(2013/10/28)

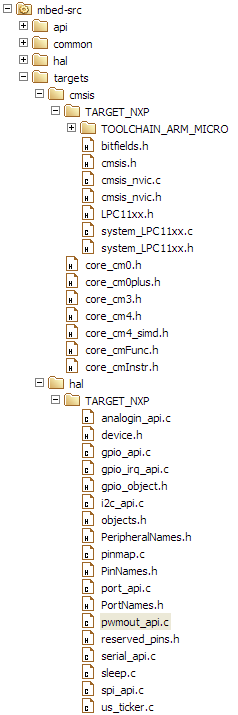

パスが通ってないだけのようなのでファイルを以下に移動する。

| mbed-src\targets\cmsis\TARGET_NXP\TARGET_LPC11XX_11CXX\ mbed-src\targets\cmsis\TARGET_NXP\TARGET_LPC11XX_11CXX\TARGET_LPC11XX\ |

にあるファイルをすべて

| mbed-src\targets\cmsis\TARGET_NXP\ |

へ移動

mbed-src\targets\cmsis\TARGET_NXP\TARGET_LPC11XX_11CXX\にある

| TOOLCHAIN_ARM_MICRO |

をフォルダごと

| mbed-src\targets\cmsis\TARGET_NXP\ |

へ移動

| mbed-src\targets\hal\TARGET_NXP\TARGET_LPC11XX_11CXX\ mbed-src\targets\hal\TARGET_NXP\TARGET_LPC11XX_11CXX\TARGET_LPC11XX\ |

にあるファイルをすべて

| mbed-src\targets\hal\TARGET_NXP\ |

へ移動

移動後は以下のような構成になると思います。

※不要なファイルは削除してあります。

|

ファイルの移動が面倒なので以下に本家からフォークしたライブラリを置いておきます。

Import librarymbed-src-LPC1114FN28

Fork of mbed-src file paths change. LPC1114FN28 use only.

エラーが出力される場合

"TOOLCHAIN_ARM_MICRO"が無いとエラーになる。

| Error: Undefined symbol _initial_sp (referred from entry2.o). Error: Undefined symbol _heap_base (referred from malloc.o). Error: Undefined symbol _heap_limit (referred from malloc.o). |

LPC1114FN28はMicrolibを使ってCompileされるため上記のエラーになるようです。

targets/cmsis/TARGET_Freescale/TARGET_KL46Z/MKL46Z4.h@31:42176bc3c368, 2013-09-25 (annotated)

- Committer:

- mbed_official

- Date:

- Wed Sep 25 11:30:05 2013 +0100

- Revision:

- 31:42176bc3c368

Synchronized with git revision f580c008b139a952d38ac5c7c53bbae375739c67

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| mbed_official | 31:42176bc3c368 | 1 | /* |

| mbed_official | 31:42176bc3c368 | 2 | ** ################################################################### |

| mbed_official | 31:42176bc3c368 | 3 | ** Processor: MKL46Z128VLK4 |

| mbed_official | 31:42176bc3c368 | 4 | ** Compilers: ARM Compiler |

| mbed_official | 31:42176bc3c368 | 5 | ** Freescale C/C++ for Embedded ARM |

| mbed_official | 31:42176bc3c368 | 6 | ** GNU C Compiler |

| mbed_official | 31:42176bc3c368 | 7 | ** IAR ANSI C/C++ Compiler for ARM |

| mbed_official | 31:42176bc3c368 | 8 | ** |

| mbed_official | 31:42176bc3c368 | 9 | ** Reference manual: KL25RM, Rev.1, Jun 2012 |

| mbed_official | 31:42176bc3c368 | 10 | ** Version: rev. 1.1, 2012-06-21 |

| mbed_official | 31:42176bc3c368 | 11 | ** |

| mbed_official | 31:42176bc3c368 | 12 | ** Abstract: |

| mbed_official | 31:42176bc3c368 | 13 | ** CMSIS Peripheral Access Layer for MKL46Z4 |

| mbed_official | 31:42176bc3c368 | 14 | ** |

| mbed_official | 31:42176bc3c368 | 15 | ** Copyright: 1997 - 2012 Freescale Semiconductor, Inc. All Rights Reserved. |

| mbed_official | 31:42176bc3c368 | 16 | ** |

| mbed_official | 31:42176bc3c368 | 17 | ** http: www.freescale.com |

| mbed_official | 31:42176bc3c368 | 18 | ** mail: support@freescale.com |

| mbed_official | 31:42176bc3c368 | 19 | ** |

| mbed_official | 31:42176bc3c368 | 20 | ** Revisions: |

| mbed_official | 31:42176bc3c368 | 21 | ** - rev. 1.0 (2012-06-13) |

| mbed_official | 31:42176bc3c368 | 22 | ** Initial version. |

| mbed_official | 31:42176bc3c368 | 23 | ** - rev. 1.1 (2012-06-21) |

| mbed_official | 31:42176bc3c368 | 24 | ** Update according to reference manual rev. 1. |

| mbed_official | 31:42176bc3c368 | 25 | ** |

| mbed_official | 31:42176bc3c368 | 26 | ** ################################################################### |

| mbed_official | 31:42176bc3c368 | 27 | */ |

| mbed_official | 31:42176bc3c368 | 28 | |

| mbed_official | 31:42176bc3c368 | 29 | /** |

| mbed_official | 31:42176bc3c368 | 30 | * @file MKL46Z4.h |

| mbed_official | 31:42176bc3c368 | 31 | * @version 1.1 |

| mbed_official | 31:42176bc3c368 | 32 | * @date 2012-06-21 |

| mbed_official | 31:42176bc3c368 | 33 | * @brief CMSIS Peripheral Access Layer for MKL46Z4 |

| mbed_official | 31:42176bc3c368 | 34 | * |

| mbed_official | 31:42176bc3c368 | 35 | * CMSIS Peripheral Access Layer for MKL46Z4 |

| mbed_official | 31:42176bc3c368 | 36 | */ |

| mbed_official | 31:42176bc3c368 | 37 | |

| mbed_official | 31:42176bc3c368 | 38 | #if !defined(MKL46Z4_H_) |

| mbed_official | 31:42176bc3c368 | 39 | #define MKL46Z4_H_ /**< Symbol preventing repeated inclusion */ |

| mbed_official | 31:42176bc3c368 | 40 | |

| mbed_official | 31:42176bc3c368 | 41 | /** Memory map major version (memory maps with equal major version number are |

| mbed_official | 31:42176bc3c368 | 42 | * compatible) */ |

| mbed_official | 31:42176bc3c368 | 43 | #define MCU_MEM_MAP_VERSION 0x0100u |

| mbed_official | 31:42176bc3c368 | 44 | /** Memory map minor version */ |

| mbed_official | 31:42176bc3c368 | 45 | #define MCU_MEM_MAP_VERSION_MINOR 0x0001u |

| mbed_official | 31:42176bc3c368 | 46 | |

| mbed_official | 31:42176bc3c368 | 47 | |

| mbed_official | 31:42176bc3c368 | 48 | /* ---------------------------------------------------------------------------- |

| mbed_official | 31:42176bc3c368 | 49 | -- Interrupt vector numbers |

| mbed_official | 31:42176bc3c368 | 50 | ---------------------------------------------------------------------------- */ |

| mbed_official | 31:42176bc3c368 | 51 | |

| mbed_official | 31:42176bc3c368 | 52 | /** |

| mbed_official | 31:42176bc3c368 | 53 | * @addtogroup Interrupt_vector_numbers Interrupt vector numbers |

| mbed_official | 31:42176bc3c368 | 54 | * @{ |

| mbed_official | 31:42176bc3c368 | 55 | */ |

| mbed_official | 31:42176bc3c368 | 56 | |

| mbed_official | 31:42176bc3c368 | 57 | /** Interrupt Number Definitions */ |

| mbed_official | 31:42176bc3c368 | 58 | typedef enum IRQn { |

| mbed_official | 31:42176bc3c368 | 59 | /* Core interrupts */ |

| mbed_official | 31:42176bc3c368 | 60 | NonMaskableInt_IRQn = -14, /**< Non Maskable Interrupt */ |

| mbed_official | 31:42176bc3c368 | 61 | HardFault_IRQn = -13, /**< Cortex-M0 SV Hard Fault Interrupt */ |

| mbed_official | 31:42176bc3c368 | 62 | SVCall_IRQn = -5, /**< Cortex-M0 SV Call Interrupt */ |

| mbed_official | 31:42176bc3c368 | 63 | PendSV_IRQn = -2, /**< Cortex-M0 Pend SV Interrupt */ |

| mbed_official | 31:42176bc3c368 | 64 | SysTick_IRQn = -1, /**< Cortex-M0 System Tick Interrupt */ |

| mbed_official | 31:42176bc3c368 | 65 | |

| mbed_official | 31:42176bc3c368 | 66 | /* Device specific interrupts */ |

| mbed_official | 31:42176bc3c368 | 67 | DMA0_IRQn = 0, /**< DMA channel 0 transfer complete interrupt */ |

| mbed_official | 31:42176bc3c368 | 68 | DMA1_IRQn = 1, /**< DMA channel 1 transfer complete interrupt */ |

| mbed_official | 31:42176bc3c368 | 69 | DMA2_IRQn = 2, /**< DMA channel 2 transfer complete interrupt */ |

| mbed_official | 31:42176bc3c368 | 70 | DMA3_IRQn = 3, /**< DMA channel 3 transfer complete interrupt */ |

| mbed_official | 31:42176bc3c368 | 71 | Reserved20_IRQn = 4, /**< Reserved interrupt 20 */ |

| mbed_official | 31:42176bc3c368 | 72 | FTFA_IRQn = 5, /**< FTFA interrupt */ |

| mbed_official | 31:42176bc3c368 | 73 | LVD_LVW_IRQn = 6, /**< Low Voltage Detect, Low Voltage Warning */ |

| mbed_official | 31:42176bc3c368 | 74 | LLW_IRQn = 7, /**< Low Leakage Wakeup */ |

| mbed_official | 31:42176bc3c368 | 75 | I2C0_IRQn = 8, /**< I2C0 interrupt */ |

| mbed_official | 31:42176bc3c368 | 76 | I2C1_IRQn = 9, /**< I2C0 interrupt 25 */ |

| mbed_official | 31:42176bc3c368 | 77 | SPI0_IRQn = 10, /**< SPI0 interrupt */ |

| mbed_official | 31:42176bc3c368 | 78 | SPI1_IRQn = 11, /**< SPI1 interrupt */ |

| mbed_official | 31:42176bc3c368 | 79 | UART0_IRQn = 12, /**< UART0 status/error interrupt */ |

| mbed_official | 31:42176bc3c368 | 80 | UART1_IRQn = 13, /**< UART1 status/error interrupt */ |

| mbed_official | 31:42176bc3c368 | 81 | UART2_IRQn = 14, /**< UART2 status/error interrupt */ |

| mbed_official | 31:42176bc3c368 | 82 | ADC0_IRQn = 15, /**< ADC0 interrupt */ |

| mbed_official | 31:42176bc3c368 | 83 | CMP0_IRQn = 16, /**< CMP0 interrupt */ |

| mbed_official | 31:42176bc3c368 | 84 | TPM0_IRQn = 17, /**< TPM0 fault, overflow and channels interrupt */ |

| mbed_official | 31:42176bc3c368 | 85 | TPM1_IRQn = 18, /**< TPM1 fault, overflow and channels interrupt */ |

| mbed_official | 31:42176bc3c368 | 86 | TPM2_IRQn = 19, /**< TPM2 fault, overflow and channels interrupt */ |

| mbed_official | 31:42176bc3c368 | 87 | RTC_IRQn = 20, /**< RTC interrupt */ |

| mbed_official | 31:42176bc3c368 | 88 | RTC_Seconds_IRQn = 21, /**< RTC seconds interrupt */ |

| mbed_official | 31:42176bc3c368 | 89 | PIT_IRQn = 22, /**< PIT timer interrupt */ |

| mbed_official | 31:42176bc3c368 | 90 | Reserved39_IRQn = 23, /**< Reserved interrupt 39 */ |

| mbed_official | 31:42176bc3c368 | 91 | USB0_IRQn = 24, /**< USB0 interrupt */ |

| mbed_official | 31:42176bc3c368 | 92 | DAC0_IRQn = 25, /**< DAC interrupt */ |

| mbed_official | 31:42176bc3c368 | 93 | TSI0_IRQn = 26, /**< TSI0 interrupt */ |

| mbed_official | 31:42176bc3c368 | 94 | MCG_IRQn = 27, /**< MCG interrupt */ |

| mbed_official | 31:42176bc3c368 | 95 | LPTimer_IRQn = 28, /**< LPTimer interrupt */ |

| mbed_official | 31:42176bc3c368 | 96 | Reserved45_IRQn = 29, /**< Reserved interrupt 45 */ |

| mbed_official | 31:42176bc3c368 | 97 | PORTA_IRQn = 30, /**< Port A interrupt */ |

| mbed_official | 31:42176bc3c368 | 98 | PORTD_IRQn = 31 /**< Port D interrupt */ |

| mbed_official | 31:42176bc3c368 | 99 | } IRQn_Type; |

| mbed_official | 31:42176bc3c368 | 100 | |

| mbed_official | 31:42176bc3c368 | 101 | /** |

| mbed_official | 31:42176bc3c368 | 102 | * @} |

| mbed_official | 31:42176bc3c368 | 103 | */ /* end of group Interrupt_vector_numbers */ |

| mbed_official | 31:42176bc3c368 | 104 | |

| mbed_official | 31:42176bc3c368 | 105 | |

| mbed_official | 31:42176bc3c368 | 106 | /* ---------------------------------------------------------------------------- |

| mbed_official | 31:42176bc3c368 | 107 | -- Cortex M0 Core Configuration |

| mbed_official | 31:42176bc3c368 | 108 | ---------------------------------------------------------------------------- */ |

| mbed_official | 31:42176bc3c368 | 109 | |

| mbed_official | 31:42176bc3c368 | 110 | /** |

| mbed_official | 31:42176bc3c368 | 111 | * @addtogroup Cortex_Core_Configuration Cortex M0 Core Configuration |

| mbed_official | 31:42176bc3c368 | 112 | * @{ |

| mbed_official | 31:42176bc3c368 | 113 | */ |

| mbed_official | 31:42176bc3c368 | 114 | |

| mbed_official | 31:42176bc3c368 | 115 | #define __CM0PLUS_REV 0x0000 /**< Core revision r0p0 */ |

| mbed_official | 31:42176bc3c368 | 116 | #define __MPU_PRESENT 0 /**< Defines if an MPU is present or not */ |

| mbed_official | 31:42176bc3c368 | 117 | #define __VTOR_PRESENT 1 /**< Defines if an MPU is present or not */ |

| mbed_official | 31:42176bc3c368 | 118 | #define __NVIC_PRIO_BITS 2 /**< Number of priority bits implemented in the NVIC */ |

| mbed_official | 31:42176bc3c368 | 119 | #define __Vendor_SysTickConfig 0 /**< Vendor specific implementation of SysTickConfig is defined */ |

| mbed_official | 31:42176bc3c368 | 120 | |

| mbed_official | 31:42176bc3c368 | 121 | #include "core_cm0plus.h" /* Core Peripheral Access Layer */ |

| mbed_official | 31:42176bc3c368 | 122 | #include "system_MKL46Z4.h" /* Device specific configuration file */ |

| mbed_official | 31:42176bc3c368 | 123 | |

| mbed_official | 31:42176bc3c368 | 124 | /** |

| mbed_official | 31:42176bc3c368 | 125 | * @} |

| mbed_official | 31:42176bc3c368 | 126 | */ /* end of group Cortex_Core_Configuration */ |

| mbed_official | 31:42176bc3c368 | 127 | |

| mbed_official | 31:42176bc3c368 | 128 | |

| mbed_official | 31:42176bc3c368 | 129 | /* ---------------------------------------------------------------------------- |

| mbed_official | 31:42176bc3c368 | 130 | -- Device Peripheral Access Layer |

| mbed_official | 31:42176bc3c368 | 131 | ---------------------------------------------------------------------------- */ |

| mbed_official | 31:42176bc3c368 | 132 | |

| mbed_official | 31:42176bc3c368 | 133 | /** |

| mbed_official | 31:42176bc3c368 | 134 | * @addtogroup Peripheral_access_layer Device Peripheral Access Layer |

| mbed_official | 31:42176bc3c368 | 135 | * @{ |

| mbed_official | 31:42176bc3c368 | 136 | */ |

| mbed_official | 31:42176bc3c368 | 137 | |

| mbed_official | 31:42176bc3c368 | 138 | |

| mbed_official | 31:42176bc3c368 | 139 | /* |

| mbed_official | 31:42176bc3c368 | 140 | ** Start of section using anonymous unions |

| mbed_official | 31:42176bc3c368 | 141 | */ |

| mbed_official | 31:42176bc3c368 | 142 | |

| mbed_official | 31:42176bc3c368 | 143 | #if defined(__ARMCC_VERSION) |

| mbed_official | 31:42176bc3c368 | 144 | #pragma push |

| mbed_official | 31:42176bc3c368 | 145 | #pragma anon_unions |

| mbed_official | 31:42176bc3c368 | 146 | #elif defined(__CWCC__) |

| mbed_official | 31:42176bc3c368 | 147 | #pragma push |

| mbed_official | 31:42176bc3c368 | 148 | #pragma cpp_extensions on |

| mbed_official | 31:42176bc3c368 | 149 | #elif defined(__GNUC__) |

| mbed_official | 31:42176bc3c368 | 150 | /* anonymous unions are enabled by default */ |

| mbed_official | 31:42176bc3c368 | 151 | #elif defined(__IAR_SYSTEMS_ICC__) |

| mbed_official | 31:42176bc3c368 | 152 | #pragma language=extended |

| mbed_official | 31:42176bc3c368 | 153 | #else |

| mbed_official | 31:42176bc3c368 | 154 | #error Not supported compiler type |

| mbed_official | 31:42176bc3c368 | 155 | #endif |

| mbed_official | 31:42176bc3c368 | 156 | |

| mbed_official | 31:42176bc3c368 | 157 | /* ---------------------------------------------------------------------------- |

| mbed_official | 31:42176bc3c368 | 158 | -- ADC Peripheral Access Layer |

| mbed_official | 31:42176bc3c368 | 159 | ---------------------------------------------------------------------------- */ |

| mbed_official | 31:42176bc3c368 | 160 | |

| mbed_official | 31:42176bc3c368 | 161 | /** |

| mbed_official | 31:42176bc3c368 | 162 | * @addtogroup ADC_Peripheral_Access_Layer ADC Peripheral Access Layer |

| mbed_official | 31:42176bc3c368 | 163 | * @{ |

| mbed_official | 31:42176bc3c368 | 164 | */ |

| mbed_official | 31:42176bc3c368 | 165 | |

| mbed_official | 31:42176bc3c368 | 166 | /** ADC - Register Layout Typedef */ |

| mbed_official | 31:42176bc3c368 | 167 | typedef struct { |

| mbed_official | 31:42176bc3c368 | 168 | __IO uint32_t SC1[2]; /**< ADC Status and Control Registers 1, array offset: 0x0, array step: 0x4 */ |

| mbed_official | 31:42176bc3c368 | 169 | __IO uint32_t CFG1; /**< ADC Configuration Register 1, offset: 0x8 */ |

| mbed_official | 31:42176bc3c368 | 170 | __IO uint32_t CFG2; /**< ADC Configuration Register 2, offset: 0xC */ |

| mbed_official | 31:42176bc3c368 | 171 | __I uint32_t R[2]; /**< ADC Data Result Register, array offset: 0x10, array step: 0x4 */ |

| mbed_official | 31:42176bc3c368 | 172 | __IO uint32_t CV1; /**< Compare Value Registers, offset: 0x18 */ |

| mbed_official | 31:42176bc3c368 | 173 | __IO uint32_t CV2; /**< Compare Value Registers, offset: 0x1C */ |

| mbed_official | 31:42176bc3c368 | 174 | __IO uint32_t SC2; /**< Status and Control Register 2, offset: 0x20 */ |

| mbed_official | 31:42176bc3c368 | 175 | __IO uint32_t SC3; /**< Status and Control Register 3, offset: 0x24 */ |

| mbed_official | 31:42176bc3c368 | 176 | __IO uint32_t OFS; /**< ADC Offset Correction Register, offset: 0x28 */ |

| mbed_official | 31:42176bc3c368 | 177 | __IO uint32_t PG; /**< ADC Plus-Side Gain Register, offset: 0x2C */ |

| mbed_official | 31:42176bc3c368 | 178 | __IO uint32_t MG; /**< ADC Minus-Side Gain Register, offset: 0x30 */ |

| mbed_official | 31:42176bc3c368 | 179 | __IO uint32_t CLPD; /**< ADC Plus-Side General Calibration Value Register, offset: 0x34 */ |

| mbed_official | 31:42176bc3c368 | 180 | __IO uint32_t CLPS; /**< ADC Plus-Side General Calibration Value Register, offset: 0x38 */ |

| mbed_official | 31:42176bc3c368 | 181 | __IO uint32_t CLP4; /**< ADC Plus-Side General Calibration Value Register, offset: 0x3C */ |

| mbed_official | 31:42176bc3c368 | 182 | __IO uint32_t CLP3; /**< ADC Plus-Side General Calibration Value Register, offset: 0x40 */ |

| mbed_official | 31:42176bc3c368 | 183 | __IO uint32_t CLP2; /**< ADC Plus-Side General Calibration Value Register, offset: 0x44 */ |

| mbed_official | 31:42176bc3c368 | 184 | __IO uint32_t CLP1; /**< ADC Plus-Side General Calibration Value Register, offset: 0x48 */ |

| mbed_official | 31:42176bc3c368 | 185 | __IO uint32_t CLP0; /**< ADC Plus-Side General Calibration Value Register, offset: 0x4C */ |

| mbed_official | 31:42176bc3c368 | 186 | uint8_t RESERVED_0[4]; |

| mbed_official | 31:42176bc3c368 | 187 | __IO uint32_t CLMD; /**< ADC Minus-Side General Calibration Value Register, offset: 0x54 */ |

| mbed_official | 31:42176bc3c368 | 188 | __IO uint32_t CLMS; /**< ADC Minus-Side General Calibration Value Register, offset: 0x58 */ |

| mbed_official | 31:42176bc3c368 | 189 | __IO uint32_t CLM4; /**< ADC Minus-Side General Calibration Value Register, offset: 0x5C */ |

| mbed_official | 31:42176bc3c368 | 190 | __IO uint32_t CLM3; /**< ADC Minus-Side General Calibration Value Register, offset: 0x60 */ |

| mbed_official | 31:42176bc3c368 | 191 | __IO uint32_t CLM2; /**< ADC Minus-Side General Calibration Value Register, offset: 0x64 */ |

| mbed_official | 31:42176bc3c368 | 192 | __IO uint32_t CLM1; /**< ADC Minus-Side General Calibration Value Register, offset: 0x68 */ |

| mbed_official | 31:42176bc3c368 | 193 | __IO uint32_t CLM0; /**< ADC Minus-Side General Calibration Value Register, offset: 0x6C */ |

| mbed_official | 31:42176bc3c368 | 194 | } ADC_Type; |

| mbed_official | 31:42176bc3c368 | 195 | |

| mbed_official | 31:42176bc3c368 | 196 | /* ---------------------------------------------------------------------------- |

| mbed_official | 31:42176bc3c368 | 197 | -- ADC Register Masks |

| mbed_official | 31:42176bc3c368 | 198 | ---------------------------------------------------------------------------- */ |

| mbed_official | 31:42176bc3c368 | 199 | |

| mbed_official | 31:42176bc3c368 | 200 | /** |

| mbed_official | 31:42176bc3c368 | 201 | * @addtogroup ADC_Register_Masks ADC Register Masks |

| mbed_official | 31:42176bc3c368 | 202 | * @{ |

| mbed_official | 31:42176bc3c368 | 203 | */ |

| mbed_official | 31:42176bc3c368 | 204 | |

| mbed_official | 31:42176bc3c368 | 205 | /* SC1 Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 206 | #define ADC_SC1_ADCH_MASK 0x1Fu |

| mbed_official | 31:42176bc3c368 | 207 | #define ADC_SC1_ADCH_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 208 | #define ADC_SC1_ADCH(x) (((uint32_t)(((uint32_t)(x))<<ADC_SC1_ADCH_SHIFT))&ADC_SC1_ADCH_MASK) |

| mbed_official | 31:42176bc3c368 | 209 | #define ADC_SC1_DIFF_MASK 0x20u |

| mbed_official | 31:42176bc3c368 | 210 | #define ADC_SC1_DIFF_SHIFT 5 |

| mbed_official | 31:42176bc3c368 | 211 | #define ADC_SC1_AIEN_MASK 0x40u |

| mbed_official | 31:42176bc3c368 | 212 | #define ADC_SC1_AIEN_SHIFT 6 |

| mbed_official | 31:42176bc3c368 | 213 | #define ADC_SC1_COCO_MASK 0x80u |

| mbed_official | 31:42176bc3c368 | 214 | #define ADC_SC1_COCO_SHIFT 7 |

| mbed_official | 31:42176bc3c368 | 215 | /* CFG1 Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 216 | #define ADC_CFG1_ADICLK_MASK 0x3u |

| mbed_official | 31:42176bc3c368 | 217 | #define ADC_CFG1_ADICLK_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 218 | #define ADC_CFG1_ADICLK(x) (((uint32_t)(((uint32_t)(x))<<ADC_CFG1_ADICLK_SHIFT))&ADC_CFG1_ADICLK_MASK) |

| mbed_official | 31:42176bc3c368 | 219 | #define ADC_CFG1_MODE_MASK 0xCu |

| mbed_official | 31:42176bc3c368 | 220 | #define ADC_CFG1_MODE_SHIFT 2 |

| mbed_official | 31:42176bc3c368 | 221 | #define ADC_CFG1_MODE(x) (((uint32_t)(((uint32_t)(x))<<ADC_CFG1_MODE_SHIFT))&ADC_CFG1_MODE_MASK) |

| mbed_official | 31:42176bc3c368 | 222 | #define ADC_CFG1_ADLSMP_MASK 0x10u |

| mbed_official | 31:42176bc3c368 | 223 | #define ADC_CFG1_ADLSMP_SHIFT 4 |

| mbed_official | 31:42176bc3c368 | 224 | #define ADC_CFG1_ADIV_MASK 0x60u |

| mbed_official | 31:42176bc3c368 | 225 | #define ADC_CFG1_ADIV_SHIFT 5 |

| mbed_official | 31:42176bc3c368 | 226 | #define ADC_CFG1_ADIV(x) (((uint32_t)(((uint32_t)(x))<<ADC_CFG1_ADIV_SHIFT))&ADC_CFG1_ADIV_MASK) |

| mbed_official | 31:42176bc3c368 | 227 | #define ADC_CFG1_ADLPC_MASK 0x80u |

| mbed_official | 31:42176bc3c368 | 228 | #define ADC_CFG1_ADLPC_SHIFT 7 |

| mbed_official | 31:42176bc3c368 | 229 | /* CFG2 Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 230 | #define ADC_CFG2_ADLSTS_MASK 0x3u |

| mbed_official | 31:42176bc3c368 | 231 | #define ADC_CFG2_ADLSTS_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 232 | #define ADC_CFG2_ADLSTS(x) (((uint32_t)(((uint32_t)(x))<<ADC_CFG2_ADLSTS_SHIFT))&ADC_CFG2_ADLSTS_MASK) |

| mbed_official | 31:42176bc3c368 | 233 | #define ADC_CFG2_ADHSC_MASK 0x4u |

| mbed_official | 31:42176bc3c368 | 234 | #define ADC_CFG2_ADHSC_SHIFT 2 |

| mbed_official | 31:42176bc3c368 | 235 | #define ADC_CFG2_ADACKEN_MASK 0x8u |

| mbed_official | 31:42176bc3c368 | 236 | #define ADC_CFG2_ADACKEN_SHIFT 3 |

| mbed_official | 31:42176bc3c368 | 237 | #define ADC_CFG2_MUXSEL_MASK 0x10u |

| mbed_official | 31:42176bc3c368 | 238 | #define ADC_CFG2_MUXSEL_SHIFT 4 |

| mbed_official | 31:42176bc3c368 | 239 | /* R Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 240 | #define ADC_R_D_MASK 0xFFFFu |

| mbed_official | 31:42176bc3c368 | 241 | #define ADC_R_D_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 242 | #define ADC_R_D(x) (((uint32_t)(((uint32_t)(x))<<ADC_R_D_SHIFT))&ADC_R_D_MASK) |

| mbed_official | 31:42176bc3c368 | 243 | /* CV1 Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 244 | #define ADC_CV1_CV_MASK 0xFFFFu |

| mbed_official | 31:42176bc3c368 | 245 | #define ADC_CV1_CV_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 246 | #define ADC_CV1_CV(x) (((uint32_t)(((uint32_t)(x))<<ADC_CV1_CV_SHIFT))&ADC_CV1_CV_MASK) |

| mbed_official | 31:42176bc3c368 | 247 | /* CV2 Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 248 | #define ADC_CV2_CV_MASK 0xFFFFu |

| mbed_official | 31:42176bc3c368 | 249 | #define ADC_CV2_CV_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 250 | #define ADC_CV2_CV(x) (((uint32_t)(((uint32_t)(x))<<ADC_CV2_CV_SHIFT))&ADC_CV2_CV_MASK) |

| mbed_official | 31:42176bc3c368 | 251 | /* SC2 Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 252 | #define ADC_SC2_REFSEL_MASK 0x3u |

| mbed_official | 31:42176bc3c368 | 253 | #define ADC_SC2_REFSEL_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 254 | #define ADC_SC2_REFSEL(x) (((uint32_t)(((uint32_t)(x))<<ADC_SC2_REFSEL_SHIFT))&ADC_SC2_REFSEL_MASK) |

| mbed_official | 31:42176bc3c368 | 255 | #define ADC_SC2_DMAEN_MASK 0x4u |

| mbed_official | 31:42176bc3c368 | 256 | #define ADC_SC2_DMAEN_SHIFT 2 |

| mbed_official | 31:42176bc3c368 | 257 | #define ADC_SC2_ACREN_MASK 0x8u |

| mbed_official | 31:42176bc3c368 | 258 | #define ADC_SC2_ACREN_SHIFT 3 |

| mbed_official | 31:42176bc3c368 | 259 | #define ADC_SC2_ACFGT_MASK 0x10u |

| mbed_official | 31:42176bc3c368 | 260 | #define ADC_SC2_ACFGT_SHIFT 4 |

| mbed_official | 31:42176bc3c368 | 261 | #define ADC_SC2_ACFE_MASK 0x20u |

| mbed_official | 31:42176bc3c368 | 262 | #define ADC_SC2_ACFE_SHIFT 5 |

| mbed_official | 31:42176bc3c368 | 263 | #define ADC_SC2_ADTRG_MASK 0x40u |

| mbed_official | 31:42176bc3c368 | 264 | #define ADC_SC2_ADTRG_SHIFT 6 |

| mbed_official | 31:42176bc3c368 | 265 | #define ADC_SC2_ADACT_MASK 0x80u |

| mbed_official | 31:42176bc3c368 | 266 | #define ADC_SC2_ADACT_SHIFT 7 |

| mbed_official | 31:42176bc3c368 | 267 | /* SC3 Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 268 | #define ADC_SC3_AVGS_MASK 0x3u |

| mbed_official | 31:42176bc3c368 | 269 | #define ADC_SC3_AVGS_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 270 | #define ADC_SC3_AVGS(x) (((uint32_t)(((uint32_t)(x))<<ADC_SC3_AVGS_SHIFT))&ADC_SC3_AVGS_MASK) |

| mbed_official | 31:42176bc3c368 | 271 | #define ADC_SC3_AVGE_MASK 0x4u |

| mbed_official | 31:42176bc3c368 | 272 | #define ADC_SC3_AVGE_SHIFT 2 |

| mbed_official | 31:42176bc3c368 | 273 | #define ADC_SC3_ADCO_MASK 0x8u |

| mbed_official | 31:42176bc3c368 | 274 | #define ADC_SC3_ADCO_SHIFT 3 |

| mbed_official | 31:42176bc3c368 | 275 | #define ADC_SC3_CALF_MASK 0x40u |

| mbed_official | 31:42176bc3c368 | 276 | #define ADC_SC3_CALF_SHIFT 6 |

| mbed_official | 31:42176bc3c368 | 277 | #define ADC_SC3_CAL_MASK 0x80u |

| mbed_official | 31:42176bc3c368 | 278 | #define ADC_SC3_CAL_SHIFT 7 |

| mbed_official | 31:42176bc3c368 | 279 | /* OFS Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 280 | #define ADC_OFS_OFS_MASK 0xFFFFu |

| mbed_official | 31:42176bc3c368 | 281 | #define ADC_OFS_OFS_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 282 | #define ADC_OFS_OFS(x) (((uint32_t)(((uint32_t)(x))<<ADC_OFS_OFS_SHIFT))&ADC_OFS_OFS_MASK) |

| mbed_official | 31:42176bc3c368 | 283 | /* PG Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 284 | #define ADC_PG_PG_MASK 0xFFFFu |

| mbed_official | 31:42176bc3c368 | 285 | #define ADC_PG_PG_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 286 | #define ADC_PG_PG(x) (((uint32_t)(((uint32_t)(x))<<ADC_PG_PG_SHIFT))&ADC_PG_PG_MASK) |

| mbed_official | 31:42176bc3c368 | 287 | /* MG Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 288 | #define ADC_MG_MG_MASK 0xFFFFu |

| mbed_official | 31:42176bc3c368 | 289 | #define ADC_MG_MG_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 290 | #define ADC_MG_MG(x) (((uint32_t)(((uint32_t)(x))<<ADC_MG_MG_SHIFT))&ADC_MG_MG_MASK) |

| mbed_official | 31:42176bc3c368 | 291 | /* CLPD Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 292 | #define ADC_CLPD_CLPD_MASK 0x3Fu |

| mbed_official | 31:42176bc3c368 | 293 | #define ADC_CLPD_CLPD_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 294 | #define ADC_CLPD_CLPD(x) (((uint32_t)(((uint32_t)(x))<<ADC_CLPD_CLPD_SHIFT))&ADC_CLPD_CLPD_MASK) |

| mbed_official | 31:42176bc3c368 | 295 | /* CLPS Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 296 | #define ADC_CLPS_CLPS_MASK 0x3Fu |

| mbed_official | 31:42176bc3c368 | 297 | #define ADC_CLPS_CLPS_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 298 | #define ADC_CLPS_CLPS(x) (((uint32_t)(((uint32_t)(x))<<ADC_CLPS_CLPS_SHIFT))&ADC_CLPS_CLPS_MASK) |

| mbed_official | 31:42176bc3c368 | 299 | /* CLP4 Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 300 | #define ADC_CLP4_CLP4_MASK 0x3FFu |

| mbed_official | 31:42176bc3c368 | 301 | #define ADC_CLP4_CLP4_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 302 | #define ADC_CLP4_CLP4(x) (((uint32_t)(((uint32_t)(x))<<ADC_CLP4_CLP4_SHIFT))&ADC_CLP4_CLP4_MASK) |

| mbed_official | 31:42176bc3c368 | 303 | /* CLP3 Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 304 | #define ADC_CLP3_CLP3_MASK 0x1FFu |

| mbed_official | 31:42176bc3c368 | 305 | #define ADC_CLP3_CLP3_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 306 | #define ADC_CLP3_CLP3(x) (((uint32_t)(((uint32_t)(x))<<ADC_CLP3_CLP3_SHIFT))&ADC_CLP3_CLP3_MASK) |

| mbed_official | 31:42176bc3c368 | 307 | /* CLP2 Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 308 | #define ADC_CLP2_CLP2_MASK 0xFFu |

| mbed_official | 31:42176bc3c368 | 309 | #define ADC_CLP2_CLP2_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 310 | #define ADC_CLP2_CLP2(x) (((uint32_t)(((uint32_t)(x))<<ADC_CLP2_CLP2_SHIFT))&ADC_CLP2_CLP2_MASK) |

| mbed_official | 31:42176bc3c368 | 311 | /* CLP1 Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 312 | #define ADC_CLP1_CLP1_MASK 0x7Fu |

| mbed_official | 31:42176bc3c368 | 313 | #define ADC_CLP1_CLP1_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 314 | #define ADC_CLP1_CLP1(x) (((uint32_t)(((uint32_t)(x))<<ADC_CLP1_CLP1_SHIFT))&ADC_CLP1_CLP1_MASK) |

| mbed_official | 31:42176bc3c368 | 315 | /* CLP0 Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 316 | #define ADC_CLP0_CLP0_MASK 0x3Fu |

| mbed_official | 31:42176bc3c368 | 317 | #define ADC_CLP0_CLP0_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 318 | #define ADC_CLP0_CLP0(x) (((uint32_t)(((uint32_t)(x))<<ADC_CLP0_CLP0_SHIFT))&ADC_CLP0_CLP0_MASK) |

| mbed_official | 31:42176bc3c368 | 319 | /* CLMD Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 320 | #define ADC_CLMD_CLMD_MASK 0x3Fu |

| mbed_official | 31:42176bc3c368 | 321 | #define ADC_CLMD_CLMD_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 322 | #define ADC_CLMD_CLMD(x) (((uint32_t)(((uint32_t)(x))<<ADC_CLMD_CLMD_SHIFT))&ADC_CLMD_CLMD_MASK) |

| mbed_official | 31:42176bc3c368 | 323 | /* CLMS Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 324 | #define ADC_CLMS_CLMS_MASK 0x3Fu |

| mbed_official | 31:42176bc3c368 | 325 | #define ADC_CLMS_CLMS_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 326 | #define ADC_CLMS_CLMS(x) (((uint32_t)(((uint32_t)(x))<<ADC_CLMS_CLMS_SHIFT))&ADC_CLMS_CLMS_MASK) |

| mbed_official | 31:42176bc3c368 | 327 | /* CLM4 Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 328 | #define ADC_CLM4_CLM4_MASK 0x3FFu |

| mbed_official | 31:42176bc3c368 | 329 | #define ADC_CLM4_CLM4_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 330 | #define ADC_CLM4_CLM4(x) (((uint32_t)(((uint32_t)(x))<<ADC_CLM4_CLM4_SHIFT))&ADC_CLM4_CLM4_MASK) |

| mbed_official | 31:42176bc3c368 | 331 | /* CLM3 Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 332 | #define ADC_CLM3_CLM3_MASK 0x1FFu |

| mbed_official | 31:42176bc3c368 | 333 | #define ADC_CLM3_CLM3_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 334 | #define ADC_CLM3_CLM3(x) (((uint32_t)(((uint32_t)(x))<<ADC_CLM3_CLM3_SHIFT))&ADC_CLM3_CLM3_MASK) |

| mbed_official | 31:42176bc3c368 | 335 | /* CLM2 Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 336 | #define ADC_CLM2_CLM2_MASK 0xFFu |

| mbed_official | 31:42176bc3c368 | 337 | #define ADC_CLM2_CLM2_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 338 | #define ADC_CLM2_CLM2(x) (((uint32_t)(((uint32_t)(x))<<ADC_CLM2_CLM2_SHIFT))&ADC_CLM2_CLM2_MASK) |

| mbed_official | 31:42176bc3c368 | 339 | /* CLM1 Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 340 | #define ADC_CLM1_CLM1_MASK 0x7Fu |

| mbed_official | 31:42176bc3c368 | 341 | #define ADC_CLM1_CLM1_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 342 | #define ADC_CLM1_CLM1(x) (((uint32_t)(((uint32_t)(x))<<ADC_CLM1_CLM1_SHIFT))&ADC_CLM1_CLM1_MASK) |

| mbed_official | 31:42176bc3c368 | 343 | /* CLM0 Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 344 | #define ADC_CLM0_CLM0_MASK 0x3Fu |

| mbed_official | 31:42176bc3c368 | 345 | #define ADC_CLM0_CLM0_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 346 | #define ADC_CLM0_CLM0(x) (((uint32_t)(((uint32_t)(x))<<ADC_CLM0_CLM0_SHIFT))&ADC_CLM0_CLM0_MASK) |

| mbed_official | 31:42176bc3c368 | 347 | |

| mbed_official | 31:42176bc3c368 | 348 | /** |

| mbed_official | 31:42176bc3c368 | 349 | * @} |

| mbed_official | 31:42176bc3c368 | 350 | */ /* end of group ADC_Register_Masks */ |

| mbed_official | 31:42176bc3c368 | 351 | |

| mbed_official | 31:42176bc3c368 | 352 | |

| mbed_official | 31:42176bc3c368 | 353 | /* ADC - Peripheral instance base addresses */ |

| mbed_official | 31:42176bc3c368 | 354 | /** Peripheral ADC0 base address */ |

| mbed_official | 31:42176bc3c368 | 355 | #define ADC0_BASE (0x4003B000u) |

| mbed_official | 31:42176bc3c368 | 356 | /** Peripheral ADC0 base pointer */ |

| mbed_official | 31:42176bc3c368 | 357 | #define ADC0 ((ADC_Type *)ADC0_BASE) |

| mbed_official | 31:42176bc3c368 | 358 | /** Array initializer of ADC peripheral base pointers */ |

| mbed_official | 31:42176bc3c368 | 359 | #define ADC_BASES { ADC0 } |

| mbed_official | 31:42176bc3c368 | 360 | |

| mbed_official | 31:42176bc3c368 | 361 | /** |

| mbed_official | 31:42176bc3c368 | 362 | * @} |

| mbed_official | 31:42176bc3c368 | 363 | */ /* end of group ADC_Peripheral_Access_Layer */ |

| mbed_official | 31:42176bc3c368 | 364 | |

| mbed_official | 31:42176bc3c368 | 365 | |

| mbed_official | 31:42176bc3c368 | 366 | /* ---------------------------------------------------------------------------- |

| mbed_official | 31:42176bc3c368 | 367 | -- CMP Peripheral Access Layer |

| mbed_official | 31:42176bc3c368 | 368 | ---------------------------------------------------------------------------- */ |

| mbed_official | 31:42176bc3c368 | 369 | |

| mbed_official | 31:42176bc3c368 | 370 | /** |

| mbed_official | 31:42176bc3c368 | 371 | * @addtogroup CMP_Peripheral_Access_Layer CMP Peripheral Access Layer |

| mbed_official | 31:42176bc3c368 | 372 | * @{ |

| mbed_official | 31:42176bc3c368 | 373 | */ |

| mbed_official | 31:42176bc3c368 | 374 | |

| mbed_official | 31:42176bc3c368 | 375 | /** CMP - Register Layout Typedef */ |

| mbed_official | 31:42176bc3c368 | 376 | typedef struct { |

| mbed_official | 31:42176bc3c368 | 377 | __IO uint8_t CR0; /**< CMP Control Register 0, offset: 0x0 */ |

| mbed_official | 31:42176bc3c368 | 378 | __IO uint8_t CR1; /**< CMP Control Register 1, offset: 0x1 */ |

| mbed_official | 31:42176bc3c368 | 379 | __IO uint8_t FPR; /**< CMP Filter Period Register, offset: 0x2 */ |

| mbed_official | 31:42176bc3c368 | 380 | __IO uint8_t SCR; /**< CMP Status and Control Register, offset: 0x3 */ |

| mbed_official | 31:42176bc3c368 | 381 | __IO uint8_t DACCR; /**< DAC Control Register, offset: 0x4 */ |

| mbed_official | 31:42176bc3c368 | 382 | __IO uint8_t MUXCR; /**< MUX Control Register, offset: 0x5 */ |

| mbed_official | 31:42176bc3c368 | 383 | } CMP_Type; |

| mbed_official | 31:42176bc3c368 | 384 | |

| mbed_official | 31:42176bc3c368 | 385 | /* ---------------------------------------------------------------------------- |

| mbed_official | 31:42176bc3c368 | 386 | -- CMP Register Masks |

| mbed_official | 31:42176bc3c368 | 387 | ---------------------------------------------------------------------------- */ |

| mbed_official | 31:42176bc3c368 | 388 | |

| mbed_official | 31:42176bc3c368 | 389 | /** |

| mbed_official | 31:42176bc3c368 | 390 | * @addtogroup CMP_Register_Masks CMP Register Masks |

| mbed_official | 31:42176bc3c368 | 391 | * @{ |

| mbed_official | 31:42176bc3c368 | 392 | */ |

| mbed_official | 31:42176bc3c368 | 393 | |

| mbed_official | 31:42176bc3c368 | 394 | /* CR0 Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 395 | #define CMP_CR0_HYSTCTR_MASK 0x3u |

| mbed_official | 31:42176bc3c368 | 396 | #define CMP_CR0_HYSTCTR_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 397 | #define CMP_CR0_HYSTCTR(x) (((uint8_t)(((uint8_t)(x))<<CMP_CR0_HYSTCTR_SHIFT))&CMP_CR0_HYSTCTR_MASK) |

| mbed_official | 31:42176bc3c368 | 398 | #define CMP_CR0_FILTER_CNT_MASK 0x70u |

| mbed_official | 31:42176bc3c368 | 399 | #define CMP_CR0_FILTER_CNT_SHIFT 4 |

| mbed_official | 31:42176bc3c368 | 400 | #define CMP_CR0_FILTER_CNT(x) (((uint8_t)(((uint8_t)(x))<<CMP_CR0_FILTER_CNT_SHIFT))&CMP_CR0_FILTER_CNT_MASK) |

| mbed_official | 31:42176bc3c368 | 401 | /* CR1 Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 402 | #define CMP_CR1_EN_MASK 0x1u |

| mbed_official | 31:42176bc3c368 | 403 | #define CMP_CR1_EN_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 404 | #define CMP_CR1_OPE_MASK 0x2u |

| mbed_official | 31:42176bc3c368 | 405 | #define CMP_CR1_OPE_SHIFT 1 |

| mbed_official | 31:42176bc3c368 | 406 | #define CMP_CR1_COS_MASK 0x4u |

| mbed_official | 31:42176bc3c368 | 407 | #define CMP_CR1_COS_SHIFT 2 |

| mbed_official | 31:42176bc3c368 | 408 | #define CMP_CR1_INV_MASK 0x8u |

| mbed_official | 31:42176bc3c368 | 409 | #define CMP_CR1_INV_SHIFT 3 |

| mbed_official | 31:42176bc3c368 | 410 | #define CMP_CR1_PMODE_MASK 0x10u |

| mbed_official | 31:42176bc3c368 | 411 | #define CMP_CR1_PMODE_SHIFT 4 |

| mbed_official | 31:42176bc3c368 | 412 | #define CMP_CR1_TRIGM_MASK 0x20u |

| mbed_official | 31:42176bc3c368 | 413 | #define CMP_CR1_TRIGM_SHIFT 5 |

| mbed_official | 31:42176bc3c368 | 414 | #define CMP_CR1_WE_MASK 0x40u |

| mbed_official | 31:42176bc3c368 | 415 | #define CMP_CR1_WE_SHIFT 6 |

| mbed_official | 31:42176bc3c368 | 416 | #define CMP_CR1_SE_MASK 0x80u |

| mbed_official | 31:42176bc3c368 | 417 | #define CMP_CR1_SE_SHIFT 7 |

| mbed_official | 31:42176bc3c368 | 418 | /* FPR Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 419 | #define CMP_FPR_FILT_PER_MASK 0xFFu |

| mbed_official | 31:42176bc3c368 | 420 | #define CMP_FPR_FILT_PER_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 421 | #define CMP_FPR_FILT_PER(x) (((uint8_t)(((uint8_t)(x))<<CMP_FPR_FILT_PER_SHIFT))&CMP_FPR_FILT_PER_MASK) |

| mbed_official | 31:42176bc3c368 | 422 | /* SCR Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 423 | #define CMP_SCR_COUT_MASK 0x1u |

| mbed_official | 31:42176bc3c368 | 424 | #define CMP_SCR_COUT_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 425 | #define CMP_SCR_CFF_MASK 0x2u |

| mbed_official | 31:42176bc3c368 | 426 | #define CMP_SCR_CFF_SHIFT 1 |

| mbed_official | 31:42176bc3c368 | 427 | #define CMP_SCR_CFR_MASK 0x4u |

| mbed_official | 31:42176bc3c368 | 428 | #define CMP_SCR_CFR_SHIFT 2 |

| mbed_official | 31:42176bc3c368 | 429 | #define CMP_SCR_IEF_MASK 0x8u |

| mbed_official | 31:42176bc3c368 | 430 | #define CMP_SCR_IEF_SHIFT 3 |

| mbed_official | 31:42176bc3c368 | 431 | #define CMP_SCR_IER_MASK 0x10u |

| mbed_official | 31:42176bc3c368 | 432 | #define CMP_SCR_IER_SHIFT 4 |

| mbed_official | 31:42176bc3c368 | 433 | #define CMP_SCR_DMAEN_MASK 0x40u |

| mbed_official | 31:42176bc3c368 | 434 | #define CMP_SCR_DMAEN_SHIFT 6 |

| mbed_official | 31:42176bc3c368 | 435 | /* DACCR Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 436 | #define CMP_DACCR_VOSEL_MASK 0x3Fu |

| mbed_official | 31:42176bc3c368 | 437 | #define CMP_DACCR_VOSEL_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 438 | #define CMP_DACCR_VOSEL(x) (((uint8_t)(((uint8_t)(x))<<CMP_DACCR_VOSEL_SHIFT))&CMP_DACCR_VOSEL_MASK) |

| mbed_official | 31:42176bc3c368 | 439 | #define CMP_DACCR_VRSEL_MASK 0x40u |

| mbed_official | 31:42176bc3c368 | 440 | #define CMP_DACCR_VRSEL_SHIFT 6 |

| mbed_official | 31:42176bc3c368 | 441 | #define CMP_DACCR_DACEN_MASK 0x80u |

| mbed_official | 31:42176bc3c368 | 442 | #define CMP_DACCR_DACEN_SHIFT 7 |

| mbed_official | 31:42176bc3c368 | 443 | /* MUXCR Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 444 | #define CMP_MUXCR_MSEL_MASK 0x7u |

| mbed_official | 31:42176bc3c368 | 445 | #define CMP_MUXCR_MSEL_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 446 | #define CMP_MUXCR_MSEL(x) (((uint8_t)(((uint8_t)(x))<<CMP_MUXCR_MSEL_SHIFT))&CMP_MUXCR_MSEL_MASK) |

| mbed_official | 31:42176bc3c368 | 447 | #define CMP_MUXCR_PSEL_MASK 0x38u |

| mbed_official | 31:42176bc3c368 | 448 | #define CMP_MUXCR_PSEL_SHIFT 3 |

| mbed_official | 31:42176bc3c368 | 449 | #define CMP_MUXCR_PSEL(x) (((uint8_t)(((uint8_t)(x))<<CMP_MUXCR_PSEL_SHIFT))&CMP_MUXCR_PSEL_MASK) |

| mbed_official | 31:42176bc3c368 | 450 | #define CMP_MUXCR_PSTM_MASK 0x40u |

| mbed_official | 31:42176bc3c368 | 451 | #define CMP_MUXCR_PSTM_SHIFT 6 |

| mbed_official | 31:42176bc3c368 | 452 | |

| mbed_official | 31:42176bc3c368 | 453 | /** |

| mbed_official | 31:42176bc3c368 | 454 | * @} |

| mbed_official | 31:42176bc3c368 | 455 | */ /* end of group CMP_Register_Masks */ |

| mbed_official | 31:42176bc3c368 | 456 | |

| mbed_official | 31:42176bc3c368 | 457 | |

| mbed_official | 31:42176bc3c368 | 458 | /* CMP - Peripheral instance base addresses */ |

| mbed_official | 31:42176bc3c368 | 459 | /** Peripheral CMP0 base address */ |

| mbed_official | 31:42176bc3c368 | 460 | #define CMP0_BASE (0x40073000u) |

| mbed_official | 31:42176bc3c368 | 461 | /** Peripheral CMP0 base pointer */ |

| mbed_official | 31:42176bc3c368 | 462 | #define CMP0 ((CMP_Type *)CMP0_BASE) |

| mbed_official | 31:42176bc3c368 | 463 | /** Array initializer of CMP peripheral base pointers */ |

| mbed_official | 31:42176bc3c368 | 464 | #define CMP_BASES { CMP0 } |

| mbed_official | 31:42176bc3c368 | 465 | |

| mbed_official | 31:42176bc3c368 | 466 | /** |

| mbed_official | 31:42176bc3c368 | 467 | * @} |

| mbed_official | 31:42176bc3c368 | 468 | */ /* end of group CMP_Peripheral_Access_Layer */ |

| mbed_official | 31:42176bc3c368 | 469 | |

| mbed_official | 31:42176bc3c368 | 470 | |

| mbed_official | 31:42176bc3c368 | 471 | /* ---------------------------------------------------------------------------- |

| mbed_official | 31:42176bc3c368 | 472 | -- DAC Peripheral Access Layer |

| mbed_official | 31:42176bc3c368 | 473 | ---------------------------------------------------------------------------- */ |

| mbed_official | 31:42176bc3c368 | 474 | |

| mbed_official | 31:42176bc3c368 | 475 | /** |

| mbed_official | 31:42176bc3c368 | 476 | * @addtogroup DAC_Peripheral_Access_Layer DAC Peripheral Access Layer |

| mbed_official | 31:42176bc3c368 | 477 | * @{ |

| mbed_official | 31:42176bc3c368 | 478 | */ |

| mbed_official | 31:42176bc3c368 | 479 | |

| mbed_official | 31:42176bc3c368 | 480 | /** DAC - Register Layout Typedef */ |

| mbed_official | 31:42176bc3c368 | 481 | typedef struct { |

| mbed_official | 31:42176bc3c368 | 482 | struct { /* offset: 0x0, array step: 0x2 */ |

| mbed_official | 31:42176bc3c368 | 483 | __IO uint8_t DATL; /**< DAC Data Low Register, array offset: 0x0, array step: 0x2 */ |

| mbed_official | 31:42176bc3c368 | 484 | __IO uint8_t DATH; /**< DAC Data High Register, array offset: 0x1, array step: 0x2 */ |

| mbed_official | 31:42176bc3c368 | 485 | } DAT[2]; |

| mbed_official | 31:42176bc3c368 | 486 | uint8_t RESERVED_0[28]; |

| mbed_official | 31:42176bc3c368 | 487 | __IO uint8_t SR; /**< DAC Status Register, offset: 0x20 */ |

| mbed_official | 31:42176bc3c368 | 488 | __IO uint8_t C0; /**< DAC Control Register, offset: 0x21 */ |

| mbed_official | 31:42176bc3c368 | 489 | __IO uint8_t C1; /**< DAC Control Register 1, offset: 0x22 */ |

| mbed_official | 31:42176bc3c368 | 490 | __IO uint8_t C2; /**< DAC Control Register 2, offset: 0x23 */ |

| mbed_official | 31:42176bc3c368 | 491 | } DAC_Type; |

| mbed_official | 31:42176bc3c368 | 492 | |

| mbed_official | 31:42176bc3c368 | 493 | /* ---------------------------------------------------------------------------- |

| mbed_official | 31:42176bc3c368 | 494 | -- DAC Register Masks |

| mbed_official | 31:42176bc3c368 | 495 | ---------------------------------------------------------------------------- */ |

| mbed_official | 31:42176bc3c368 | 496 | |

| mbed_official | 31:42176bc3c368 | 497 | /** |

| mbed_official | 31:42176bc3c368 | 498 | * @addtogroup DAC_Register_Masks DAC Register Masks |

| mbed_official | 31:42176bc3c368 | 499 | * @{ |

| mbed_official | 31:42176bc3c368 | 500 | */ |

| mbed_official | 31:42176bc3c368 | 501 | |

| mbed_official | 31:42176bc3c368 | 502 | /* DATL Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 503 | #define DAC_DATL_DATA0_MASK 0xFFu |

| mbed_official | 31:42176bc3c368 | 504 | #define DAC_DATL_DATA0_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 505 | #define DAC_DATL_DATA0(x) (((uint8_t)(((uint8_t)(x))<<DAC_DATL_DATA0_SHIFT))&DAC_DATL_DATA0_MASK) |

| mbed_official | 31:42176bc3c368 | 506 | /* DATH Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 507 | #define DAC_DATH_DATA1_MASK 0xFu |

| mbed_official | 31:42176bc3c368 | 508 | #define DAC_DATH_DATA1_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 509 | #define DAC_DATH_DATA1(x) (((uint8_t)(((uint8_t)(x))<<DAC_DATH_DATA1_SHIFT))&DAC_DATH_DATA1_MASK) |

| mbed_official | 31:42176bc3c368 | 510 | /* SR Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 511 | #define DAC_SR_DACBFRPBF_MASK 0x1u |

| mbed_official | 31:42176bc3c368 | 512 | #define DAC_SR_DACBFRPBF_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 513 | #define DAC_SR_DACBFRPTF_MASK 0x2u |

| mbed_official | 31:42176bc3c368 | 514 | #define DAC_SR_DACBFRPTF_SHIFT 1 |

| mbed_official | 31:42176bc3c368 | 515 | /* C0 Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 516 | #define DAC_C0_DACBBIEN_MASK 0x1u |

| mbed_official | 31:42176bc3c368 | 517 | #define DAC_C0_DACBBIEN_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 518 | #define DAC_C0_DACBTIEN_MASK 0x2u |

| mbed_official | 31:42176bc3c368 | 519 | #define DAC_C0_DACBTIEN_SHIFT 1 |

| mbed_official | 31:42176bc3c368 | 520 | #define DAC_C0_LPEN_MASK 0x8u |

| mbed_official | 31:42176bc3c368 | 521 | #define DAC_C0_LPEN_SHIFT 3 |

| mbed_official | 31:42176bc3c368 | 522 | #define DAC_C0_DACSWTRG_MASK 0x10u |

| mbed_official | 31:42176bc3c368 | 523 | #define DAC_C0_DACSWTRG_SHIFT 4 |

| mbed_official | 31:42176bc3c368 | 524 | #define DAC_C0_DACTRGSEL_MASK 0x20u |

| mbed_official | 31:42176bc3c368 | 525 | #define DAC_C0_DACTRGSEL_SHIFT 5 |

| mbed_official | 31:42176bc3c368 | 526 | #define DAC_C0_DACRFS_MASK 0x40u |

| mbed_official | 31:42176bc3c368 | 527 | #define DAC_C0_DACRFS_SHIFT 6 |

| mbed_official | 31:42176bc3c368 | 528 | #define DAC_C0_DACEN_MASK 0x80u |

| mbed_official | 31:42176bc3c368 | 529 | #define DAC_C0_DACEN_SHIFT 7 |

| mbed_official | 31:42176bc3c368 | 530 | /* C1 Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 531 | #define DAC_C1_DACBFEN_MASK 0x1u |

| mbed_official | 31:42176bc3c368 | 532 | #define DAC_C1_DACBFEN_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 533 | #define DAC_C1_DACBFMD_MASK 0x4u |

| mbed_official | 31:42176bc3c368 | 534 | #define DAC_C1_DACBFMD_SHIFT 2 |

| mbed_official | 31:42176bc3c368 | 535 | #define DAC_C1_DMAEN_MASK 0x80u |

| mbed_official | 31:42176bc3c368 | 536 | #define DAC_C1_DMAEN_SHIFT 7 |

| mbed_official | 31:42176bc3c368 | 537 | /* C2 Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 538 | #define DAC_C2_DACBFUP_MASK 0x1u |

| mbed_official | 31:42176bc3c368 | 539 | #define DAC_C2_DACBFUP_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 540 | #define DAC_C2_DACBFRP_MASK 0x10u |

| mbed_official | 31:42176bc3c368 | 541 | #define DAC_C2_DACBFRP_SHIFT 4 |

| mbed_official | 31:42176bc3c368 | 542 | |

| mbed_official | 31:42176bc3c368 | 543 | /** |

| mbed_official | 31:42176bc3c368 | 544 | * @} |

| mbed_official | 31:42176bc3c368 | 545 | */ /* end of group DAC_Register_Masks */ |

| mbed_official | 31:42176bc3c368 | 546 | |

| mbed_official | 31:42176bc3c368 | 547 | |

| mbed_official | 31:42176bc3c368 | 548 | /* DAC - Peripheral instance base addresses */ |

| mbed_official | 31:42176bc3c368 | 549 | /** Peripheral DAC0 base address */ |

| mbed_official | 31:42176bc3c368 | 550 | #define DAC0_BASE (0x4003F000u) |

| mbed_official | 31:42176bc3c368 | 551 | /** Peripheral DAC0 base pointer */ |

| mbed_official | 31:42176bc3c368 | 552 | #define DAC0 ((DAC_Type *)DAC0_BASE) |

| mbed_official | 31:42176bc3c368 | 553 | /** Array initializer of DAC peripheral base pointers */ |

| mbed_official | 31:42176bc3c368 | 554 | #define DAC_BASES { DAC0 } |

| mbed_official | 31:42176bc3c368 | 555 | |

| mbed_official | 31:42176bc3c368 | 556 | /** |

| mbed_official | 31:42176bc3c368 | 557 | * @} |

| mbed_official | 31:42176bc3c368 | 558 | */ /* end of group DAC_Peripheral_Access_Layer */ |

| mbed_official | 31:42176bc3c368 | 559 | |

| mbed_official | 31:42176bc3c368 | 560 | |

| mbed_official | 31:42176bc3c368 | 561 | /* ---------------------------------------------------------------------------- |

| mbed_official | 31:42176bc3c368 | 562 | -- DMA Peripheral Access Layer |

| mbed_official | 31:42176bc3c368 | 563 | ---------------------------------------------------------------------------- */ |

| mbed_official | 31:42176bc3c368 | 564 | |

| mbed_official | 31:42176bc3c368 | 565 | /** |

| mbed_official | 31:42176bc3c368 | 566 | * @addtogroup DMA_Peripheral_Access_Layer DMA Peripheral Access Layer |

| mbed_official | 31:42176bc3c368 | 567 | * @{ |

| mbed_official | 31:42176bc3c368 | 568 | */ |

| mbed_official | 31:42176bc3c368 | 569 | |

| mbed_official | 31:42176bc3c368 | 570 | /** DMA - Register Layout Typedef */ |

| mbed_official | 31:42176bc3c368 | 571 | typedef struct { |

| mbed_official | 31:42176bc3c368 | 572 | union { /* offset: 0x0 */ |

| mbed_official | 31:42176bc3c368 | 573 | __IO uint8_t REQC_ARR[4]; /**< DMA_REQC0 register...DMA_REQC3 register., array offset: 0x0, array step: 0x1 */ |

| mbed_official | 31:42176bc3c368 | 574 | }; |

| mbed_official | 31:42176bc3c368 | 575 | uint8_t RESERVED_0[252]; |

| mbed_official | 31:42176bc3c368 | 576 | struct { /* offset: 0x100, array step: 0x10 */ |

| mbed_official | 31:42176bc3c368 | 577 | __IO uint32_t SAR; /**< Source Address Register, array offset: 0x100, array step: 0x10 */ |

| mbed_official | 31:42176bc3c368 | 578 | __IO uint32_t DAR; /**< Destination Address Register, array offset: 0x104, array step: 0x10 */ |

| mbed_official | 31:42176bc3c368 | 579 | union { /* offset: 0x108, array step: 0x10 */ |

| mbed_official | 31:42176bc3c368 | 580 | __IO uint32_t DSR_BCR; /**< DMA Status Register / Byte Count Register, array offset: 0x108, array step: 0x10 */ |

| mbed_official | 31:42176bc3c368 | 581 | struct { /* offset: 0x108, array step: 0x10 */ |

| mbed_official | 31:42176bc3c368 | 582 | uint8_t RESERVED_0[3]; |

| mbed_official | 31:42176bc3c368 | 583 | __IO uint8_t DSR; /**< DMA_DSR0 register...DMA_DSR3 register., array offset: 0x10B, array step: 0x10 */ |

| mbed_official | 31:42176bc3c368 | 584 | } DMA_DSR_ACCESS8BIT; |

| mbed_official | 31:42176bc3c368 | 585 | }; |

| mbed_official | 31:42176bc3c368 | 586 | __IO uint32_t DCR; /**< DMA Control Register, array offset: 0x10C, array step: 0x10 */ |

| mbed_official | 31:42176bc3c368 | 587 | } DMA[4]; |

| mbed_official | 31:42176bc3c368 | 588 | } DMA_Type; |

| mbed_official | 31:42176bc3c368 | 589 | |

| mbed_official | 31:42176bc3c368 | 590 | /* ---------------------------------------------------------------------------- |

| mbed_official | 31:42176bc3c368 | 591 | -- DMA Register Masks |

| mbed_official | 31:42176bc3c368 | 592 | ---------------------------------------------------------------------------- */ |

| mbed_official | 31:42176bc3c368 | 593 | |

| mbed_official | 31:42176bc3c368 | 594 | /** |

| mbed_official | 31:42176bc3c368 | 595 | * @addtogroup DMA_Register_Masks DMA Register Masks |

| mbed_official | 31:42176bc3c368 | 596 | * @{ |

| mbed_official | 31:42176bc3c368 | 597 | */ |

| mbed_official | 31:42176bc3c368 | 598 | |

| mbed_official | 31:42176bc3c368 | 599 | /* REQC_ARR Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 600 | #define DMA_REQC_ARR_DMAC_MASK 0xFu |

| mbed_official | 31:42176bc3c368 | 601 | #define DMA_REQC_ARR_DMAC_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 602 | #define DMA_REQC_ARR_DMAC(x) (((uint8_t)(((uint8_t)(x))<<DMA_REQC_ARR_DMAC_SHIFT))&DMA_REQC_ARR_DMAC_MASK) |

| mbed_official | 31:42176bc3c368 | 603 | #define DMA_REQC_ARR_CFSM_MASK 0x80u |

| mbed_official | 31:42176bc3c368 | 604 | #define DMA_REQC_ARR_CFSM_SHIFT 7 |

| mbed_official | 31:42176bc3c368 | 605 | /* SAR Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 606 | #define DMA_SAR_SAR_MASK 0xFFFFFFFFu |

| mbed_official | 31:42176bc3c368 | 607 | #define DMA_SAR_SAR_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 608 | #define DMA_SAR_SAR(x) (((uint32_t)(((uint32_t)(x))<<DMA_SAR_SAR_SHIFT))&DMA_SAR_SAR_MASK) |

| mbed_official | 31:42176bc3c368 | 609 | /* DAR Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 610 | #define DMA_DAR_DAR_MASK 0xFFFFFFFFu |

| mbed_official | 31:42176bc3c368 | 611 | #define DMA_DAR_DAR_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 612 | #define DMA_DAR_DAR(x) (((uint32_t)(((uint32_t)(x))<<DMA_DAR_DAR_SHIFT))&DMA_DAR_DAR_MASK) |

| mbed_official | 31:42176bc3c368 | 613 | /* DSR_BCR Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 614 | #define DMA_DSR_BCR_BCR_MASK 0xFFFFFFu |

| mbed_official | 31:42176bc3c368 | 615 | #define DMA_DSR_BCR_BCR_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 616 | #define DMA_DSR_BCR_BCR(x) (((uint32_t)(((uint32_t)(x))<<DMA_DSR_BCR_BCR_SHIFT))&DMA_DSR_BCR_BCR_MASK) |

| mbed_official | 31:42176bc3c368 | 617 | #define DMA_DSR_BCR_DONE_MASK 0x1000000u |

| mbed_official | 31:42176bc3c368 | 618 | #define DMA_DSR_BCR_DONE_SHIFT 24 |

| mbed_official | 31:42176bc3c368 | 619 | #define DMA_DSR_BCR_BSY_MASK 0x2000000u |

| mbed_official | 31:42176bc3c368 | 620 | #define DMA_DSR_BCR_BSY_SHIFT 25 |

| mbed_official | 31:42176bc3c368 | 621 | #define DMA_DSR_BCR_REQ_MASK 0x4000000u |

| mbed_official | 31:42176bc3c368 | 622 | #define DMA_DSR_BCR_REQ_SHIFT 26 |

| mbed_official | 31:42176bc3c368 | 623 | #define DMA_DSR_BCR_BED_MASK 0x10000000u |

| mbed_official | 31:42176bc3c368 | 624 | #define DMA_DSR_BCR_BED_SHIFT 28 |

| mbed_official | 31:42176bc3c368 | 625 | #define DMA_DSR_BCR_BES_MASK 0x20000000u |

| mbed_official | 31:42176bc3c368 | 626 | #define DMA_DSR_BCR_BES_SHIFT 29 |

| mbed_official | 31:42176bc3c368 | 627 | #define DMA_DSR_BCR_CE_MASK 0x40000000u |

| mbed_official | 31:42176bc3c368 | 628 | #define DMA_DSR_BCR_CE_SHIFT 30 |

| mbed_official | 31:42176bc3c368 | 629 | /* DCR Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 630 | #define DMA_DCR_LCH2_MASK 0x3u |

| mbed_official | 31:42176bc3c368 | 631 | #define DMA_DCR_LCH2_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 632 | #define DMA_DCR_LCH2(x) (((uint32_t)(((uint32_t)(x))<<DMA_DCR_LCH2_SHIFT))&DMA_DCR_LCH2_MASK) |

| mbed_official | 31:42176bc3c368 | 633 | #define DMA_DCR_LCH1_MASK 0xCu |

| mbed_official | 31:42176bc3c368 | 634 | #define DMA_DCR_LCH1_SHIFT 2 |

| mbed_official | 31:42176bc3c368 | 635 | #define DMA_DCR_LCH1(x) (((uint32_t)(((uint32_t)(x))<<DMA_DCR_LCH1_SHIFT))&DMA_DCR_LCH1_MASK) |

| mbed_official | 31:42176bc3c368 | 636 | #define DMA_DCR_LINKCC_MASK 0x30u |

| mbed_official | 31:42176bc3c368 | 637 | #define DMA_DCR_LINKCC_SHIFT 4 |

| mbed_official | 31:42176bc3c368 | 638 | #define DMA_DCR_LINKCC(x) (((uint32_t)(((uint32_t)(x))<<DMA_DCR_LINKCC_SHIFT))&DMA_DCR_LINKCC_MASK) |

| mbed_official | 31:42176bc3c368 | 639 | #define DMA_DCR_D_REQ_MASK 0x80u |

| mbed_official | 31:42176bc3c368 | 640 | #define DMA_DCR_D_REQ_SHIFT 7 |

| mbed_official | 31:42176bc3c368 | 641 | #define DMA_DCR_DMOD_MASK 0xF00u |

| mbed_official | 31:42176bc3c368 | 642 | #define DMA_DCR_DMOD_SHIFT 8 |

| mbed_official | 31:42176bc3c368 | 643 | #define DMA_DCR_DMOD(x) (((uint32_t)(((uint32_t)(x))<<DMA_DCR_DMOD_SHIFT))&DMA_DCR_DMOD_MASK) |

| mbed_official | 31:42176bc3c368 | 644 | #define DMA_DCR_SMOD_MASK 0xF000u |

| mbed_official | 31:42176bc3c368 | 645 | #define DMA_DCR_SMOD_SHIFT 12 |

| mbed_official | 31:42176bc3c368 | 646 | #define DMA_DCR_SMOD(x) (((uint32_t)(((uint32_t)(x))<<DMA_DCR_SMOD_SHIFT))&DMA_DCR_SMOD_MASK) |

| mbed_official | 31:42176bc3c368 | 647 | #define DMA_DCR_START_MASK 0x10000u |

| mbed_official | 31:42176bc3c368 | 648 | #define DMA_DCR_START_SHIFT 16 |

| mbed_official | 31:42176bc3c368 | 649 | #define DMA_DCR_DSIZE_MASK 0x60000u |

| mbed_official | 31:42176bc3c368 | 650 | #define DMA_DCR_DSIZE_SHIFT 17 |

| mbed_official | 31:42176bc3c368 | 651 | #define DMA_DCR_DSIZE(x) (((uint32_t)(((uint32_t)(x))<<DMA_DCR_DSIZE_SHIFT))&DMA_DCR_DSIZE_MASK) |

| mbed_official | 31:42176bc3c368 | 652 | #define DMA_DCR_DINC_MASK 0x80000u |

| mbed_official | 31:42176bc3c368 | 653 | #define DMA_DCR_DINC_SHIFT 19 |

| mbed_official | 31:42176bc3c368 | 654 | #define DMA_DCR_SSIZE_MASK 0x300000u |

| mbed_official | 31:42176bc3c368 | 655 | #define DMA_DCR_SSIZE_SHIFT 20 |

| mbed_official | 31:42176bc3c368 | 656 | #define DMA_DCR_SSIZE(x) (((uint32_t)(((uint32_t)(x))<<DMA_DCR_SSIZE_SHIFT))&DMA_DCR_SSIZE_MASK) |

| mbed_official | 31:42176bc3c368 | 657 | #define DMA_DCR_SINC_MASK 0x400000u |

| mbed_official | 31:42176bc3c368 | 658 | #define DMA_DCR_SINC_SHIFT 22 |

| mbed_official | 31:42176bc3c368 | 659 | #define DMA_DCR_EADREQ_MASK 0x800000u |

| mbed_official | 31:42176bc3c368 | 660 | #define DMA_DCR_EADREQ_SHIFT 23 |

| mbed_official | 31:42176bc3c368 | 661 | #define DMA_DCR_AA_MASK 0x10000000u |

| mbed_official | 31:42176bc3c368 | 662 | #define DMA_DCR_AA_SHIFT 28 |

| mbed_official | 31:42176bc3c368 | 663 | #define DMA_DCR_CS_MASK 0x20000000u |

| mbed_official | 31:42176bc3c368 | 664 | #define DMA_DCR_CS_SHIFT 29 |

| mbed_official | 31:42176bc3c368 | 665 | #define DMA_DCR_ERQ_MASK 0x40000000u |

| mbed_official | 31:42176bc3c368 | 666 | #define DMA_DCR_ERQ_SHIFT 30 |

| mbed_official | 31:42176bc3c368 | 667 | #define DMA_DCR_EINT_MASK 0x80000000u |

| mbed_official | 31:42176bc3c368 | 668 | #define DMA_DCR_EINT_SHIFT 31 |

| mbed_official | 31:42176bc3c368 | 669 | |

| mbed_official | 31:42176bc3c368 | 670 | /** |

| mbed_official | 31:42176bc3c368 | 671 | * @} |

| mbed_official | 31:42176bc3c368 | 672 | */ /* end of group DMA_Register_Masks */ |

| mbed_official | 31:42176bc3c368 | 673 | |

| mbed_official | 31:42176bc3c368 | 674 | |

| mbed_official | 31:42176bc3c368 | 675 | /* DMA - Peripheral instance base addresses */ |

| mbed_official | 31:42176bc3c368 | 676 | /** Peripheral DMA base address */ |

| mbed_official | 31:42176bc3c368 | 677 | #define DMA_BASE (0x40008000u) |

| mbed_official | 31:42176bc3c368 | 678 | /** Peripheral DMA base pointer */ |

| mbed_official | 31:42176bc3c368 | 679 | #define DMA0 ((DMA_Type *)DMA_BASE) |

| mbed_official | 31:42176bc3c368 | 680 | /** Array initializer of DMA peripheral base pointers */ |

| mbed_official | 31:42176bc3c368 | 681 | #define DMA_BASES { DMA0 } |

| mbed_official | 31:42176bc3c368 | 682 | |

| mbed_official | 31:42176bc3c368 | 683 | /** |

| mbed_official | 31:42176bc3c368 | 684 | * @} |

| mbed_official | 31:42176bc3c368 | 685 | */ /* end of group DMA_Peripheral_Access_Layer */ |

| mbed_official | 31:42176bc3c368 | 686 | |

| mbed_official | 31:42176bc3c368 | 687 | |

| mbed_official | 31:42176bc3c368 | 688 | /* ---------------------------------------------------------------------------- |

| mbed_official | 31:42176bc3c368 | 689 | -- DMAMUX Peripheral Access Layer |

| mbed_official | 31:42176bc3c368 | 690 | ---------------------------------------------------------------------------- */ |

| mbed_official | 31:42176bc3c368 | 691 | |

| mbed_official | 31:42176bc3c368 | 692 | /** |

| mbed_official | 31:42176bc3c368 | 693 | * @addtogroup DMAMUX_Peripheral_Access_Layer DMAMUX Peripheral Access Layer |

| mbed_official | 31:42176bc3c368 | 694 | * @{ |

| mbed_official | 31:42176bc3c368 | 695 | */ |

| mbed_official | 31:42176bc3c368 | 696 | |

| mbed_official | 31:42176bc3c368 | 697 | /** DMAMUX - Register Layout Typedef */ |

| mbed_official | 31:42176bc3c368 | 698 | typedef struct { |

| mbed_official | 31:42176bc3c368 | 699 | __IO uint8_t CHCFG[4]; /**< Channel Configuration register, array offset: 0x0, array step: 0x1 */ |

| mbed_official | 31:42176bc3c368 | 700 | } DMAMUX_Type; |

| mbed_official | 31:42176bc3c368 | 701 | |

| mbed_official | 31:42176bc3c368 | 702 | /* ---------------------------------------------------------------------------- |

| mbed_official | 31:42176bc3c368 | 703 | -- DMAMUX Register Masks |

| mbed_official | 31:42176bc3c368 | 704 | ---------------------------------------------------------------------------- */ |

| mbed_official | 31:42176bc3c368 | 705 | |

| mbed_official | 31:42176bc3c368 | 706 | /** |

| mbed_official | 31:42176bc3c368 | 707 | * @addtogroup DMAMUX_Register_Masks DMAMUX Register Masks |

| mbed_official | 31:42176bc3c368 | 708 | * @{ |

| mbed_official | 31:42176bc3c368 | 709 | */ |

| mbed_official | 31:42176bc3c368 | 710 | |

| mbed_official | 31:42176bc3c368 | 711 | /* CHCFG Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 712 | #define DMAMUX_CHCFG_SOURCE_MASK 0x3Fu |

| mbed_official | 31:42176bc3c368 | 713 | #define DMAMUX_CHCFG_SOURCE_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 714 | #define DMAMUX_CHCFG_SOURCE(x) (((uint8_t)(((uint8_t)(x))<<DMAMUX_CHCFG_SOURCE_SHIFT))&DMAMUX_CHCFG_SOURCE_MASK) |

| mbed_official | 31:42176bc3c368 | 715 | #define DMAMUX_CHCFG_TRIG_MASK 0x40u |

| mbed_official | 31:42176bc3c368 | 716 | #define DMAMUX_CHCFG_TRIG_SHIFT 6 |

| mbed_official | 31:42176bc3c368 | 717 | #define DMAMUX_CHCFG_ENBL_MASK 0x80u |

| mbed_official | 31:42176bc3c368 | 718 | #define DMAMUX_CHCFG_ENBL_SHIFT 7 |

| mbed_official | 31:42176bc3c368 | 719 | |

| mbed_official | 31:42176bc3c368 | 720 | /** |

| mbed_official | 31:42176bc3c368 | 721 | * @} |

| mbed_official | 31:42176bc3c368 | 722 | */ /* end of group DMAMUX_Register_Masks */ |

| mbed_official | 31:42176bc3c368 | 723 | |

| mbed_official | 31:42176bc3c368 | 724 | |

| mbed_official | 31:42176bc3c368 | 725 | /* DMAMUX - Peripheral instance base addresses */ |

| mbed_official | 31:42176bc3c368 | 726 | /** Peripheral DMAMUX0 base address */ |

| mbed_official | 31:42176bc3c368 | 727 | #define DMAMUX0_BASE (0x40021000u) |

| mbed_official | 31:42176bc3c368 | 728 | /** Peripheral DMAMUX0 base pointer */ |

| mbed_official | 31:42176bc3c368 | 729 | #define DMAMUX0 ((DMAMUX_Type *)DMAMUX0_BASE) |

| mbed_official | 31:42176bc3c368 | 730 | /** Array initializer of DMAMUX peripheral base pointers */ |

| mbed_official | 31:42176bc3c368 | 731 | #define DMAMUX_BASES { DMAMUX0 } |

| mbed_official | 31:42176bc3c368 | 732 | |

| mbed_official | 31:42176bc3c368 | 733 | /** |

| mbed_official | 31:42176bc3c368 | 734 | * @} |

| mbed_official | 31:42176bc3c368 | 735 | */ /* end of group DMAMUX_Peripheral_Access_Layer */ |

| mbed_official | 31:42176bc3c368 | 736 | |

| mbed_official | 31:42176bc3c368 | 737 | |

| mbed_official | 31:42176bc3c368 | 738 | /* ---------------------------------------------------------------------------- |

| mbed_official | 31:42176bc3c368 | 739 | -- FGPIO Peripheral Access Layer |

| mbed_official | 31:42176bc3c368 | 740 | ---------------------------------------------------------------------------- */ |

| mbed_official | 31:42176bc3c368 | 741 | |

| mbed_official | 31:42176bc3c368 | 742 | /** |

| mbed_official | 31:42176bc3c368 | 743 | * @addtogroup FGPIO_Peripheral_Access_Layer FGPIO Peripheral Access Layer |

| mbed_official | 31:42176bc3c368 | 744 | * @{ |

| mbed_official | 31:42176bc3c368 | 745 | */ |

| mbed_official | 31:42176bc3c368 | 746 | |

| mbed_official | 31:42176bc3c368 | 747 | /** FGPIO - Register Layout Typedef */ |

| mbed_official | 31:42176bc3c368 | 748 | typedef struct { |

| mbed_official | 31:42176bc3c368 | 749 | __IO uint32_t PDOR; /**< Port Data Output Register, offset: 0x0 */ |

| mbed_official | 31:42176bc3c368 | 750 | __O uint32_t PSOR; /**< Port Set Output Register, offset: 0x4 */ |

| mbed_official | 31:42176bc3c368 | 751 | __O uint32_t PCOR; /**< Port Clear Output Register, offset: 0x8 */ |

| mbed_official | 31:42176bc3c368 | 752 | __O uint32_t PTOR; /**< Port Toggle Output Register, offset: 0xC */ |

| mbed_official | 31:42176bc3c368 | 753 | __I uint32_t PDIR; /**< Port Data Input Register, offset: 0x10 */ |

| mbed_official | 31:42176bc3c368 | 754 | __IO uint32_t PDDR; /**< Port Data Direction Register, offset: 0x14 */ |

| mbed_official | 31:42176bc3c368 | 755 | } FGPIO_Type; |

| mbed_official | 31:42176bc3c368 | 756 | |

| mbed_official | 31:42176bc3c368 | 757 | /* ---------------------------------------------------------------------------- |

| mbed_official | 31:42176bc3c368 | 758 | -- FGPIO Register Masks |

| mbed_official | 31:42176bc3c368 | 759 | ---------------------------------------------------------------------------- */ |

| mbed_official | 31:42176bc3c368 | 760 | |

| mbed_official | 31:42176bc3c368 | 761 | /** |

| mbed_official | 31:42176bc3c368 | 762 | * @addtogroup FGPIO_Register_Masks FGPIO Register Masks |

| mbed_official | 31:42176bc3c368 | 763 | * @{ |

| mbed_official | 31:42176bc3c368 | 764 | */ |

| mbed_official | 31:42176bc3c368 | 765 | |

| mbed_official | 31:42176bc3c368 | 766 | /* PDOR Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 767 | #define FGPIO_PDOR_PDO_MASK 0xFFFFFFFFu |

| mbed_official | 31:42176bc3c368 | 768 | #define FGPIO_PDOR_PDO_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 769 | #define FGPIO_PDOR_PDO(x) (((uint32_t)(((uint32_t)(x))<<FGPIO_PDOR_PDO_SHIFT))&FGPIO_PDOR_PDO_MASK) |

| mbed_official | 31:42176bc3c368 | 770 | /* PSOR Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 771 | #define FGPIO_PSOR_PTSO_MASK 0xFFFFFFFFu |

| mbed_official | 31:42176bc3c368 | 772 | #define FGPIO_PSOR_PTSO_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 773 | #define FGPIO_PSOR_PTSO(x) (((uint32_t)(((uint32_t)(x))<<FGPIO_PSOR_PTSO_SHIFT))&FGPIO_PSOR_PTSO_MASK) |

| mbed_official | 31:42176bc3c368 | 774 | /* PCOR Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 775 | #define FGPIO_PCOR_PTCO_MASK 0xFFFFFFFFu |

| mbed_official | 31:42176bc3c368 | 776 | #define FGPIO_PCOR_PTCO_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 777 | #define FGPIO_PCOR_PTCO(x) (((uint32_t)(((uint32_t)(x))<<FGPIO_PCOR_PTCO_SHIFT))&FGPIO_PCOR_PTCO_MASK) |

| mbed_official | 31:42176bc3c368 | 778 | /* PTOR Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 779 | #define FGPIO_PTOR_PTTO_MASK 0xFFFFFFFFu |

| mbed_official | 31:42176bc3c368 | 780 | #define FGPIO_PTOR_PTTO_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 781 | #define FGPIO_PTOR_PTTO(x) (((uint32_t)(((uint32_t)(x))<<FGPIO_PTOR_PTTO_SHIFT))&FGPIO_PTOR_PTTO_MASK) |

| mbed_official | 31:42176bc3c368 | 782 | /* PDIR Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 783 | #define FGPIO_PDIR_PDI_MASK 0xFFFFFFFFu |

| mbed_official | 31:42176bc3c368 | 784 | #define FGPIO_PDIR_PDI_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 785 | #define FGPIO_PDIR_PDI(x) (((uint32_t)(((uint32_t)(x))<<FGPIO_PDIR_PDI_SHIFT))&FGPIO_PDIR_PDI_MASK) |

| mbed_official | 31:42176bc3c368 | 786 | /* PDDR Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 787 | #define FGPIO_PDDR_PDD_MASK 0xFFFFFFFFu |

| mbed_official | 31:42176bc3c368 | 788 | #define FGPIO_PDDR_PDD_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 789 | #define FGPIO_PDDR_PDD(x) (((uint32_t)(((uint32_t)(x))<<FGPIO_PDDR_PDD_SHIFT))&FGPIO_PDDR_PDD_MASK) |

| mbed_official | 31:42176bc3c368 | 790 | |

| mbed_official | 31:42176bc3c368 | 791 | /** |

| mbed_official | 31:42176bc3c368 | 792 | * @} |

| mbed_official | 31:42176bc3c368 | 793 | */ /* end of group FGPIO_Register_Masks */ |

| mbed_official | 31:42176bc3c368 | 794 | |

| mbed_official | 31:42176bc3c368 | 795 | |

| mbed_official | 31:42176bc3c368 | 796 | /* FGPIO - Peripheral instance base addresses */ |

| mbed_official | 31:42176bc3c368 | 797 | /** Peripheral FPTA base address */ |

| mbed_official | 31:42176bc3c368 | 798 | #define FPTA_BASE (0xF80FF000u) |

| mbed_official | 31:42176bc3c368 | 799 | /** Peripheral FPTA base pointer */ |

| mbed_official | 31:42176bc3c368 | 800 | #define FPTA ((FGPIO_Type *)FPTA_BASE) |

| mbed_official | 31:42176bc3c368 | 801 | /** Peripheral FPTB base address */ |

| mbed_official | 31:42176bc3c368 | 802 | #define FPTB_BASE (0xF80FF040u) |

| mbed_official | 31:42176bc3c368 | 803 | /** Peripheral FPTB base pointer */ |

| mbed_official | 31:42176bc3c368 | 804 | #define FPTB ((FGPIO_Type *)FPTB_BASE) |

| mbed_official | 31:42176bc3c368 | 805 | /** Peripheral FPTC base address */ |

| mbed_official | 31:42176bc3c368 | 806 | #define FPTC_BASE (0xF80FF080u) |

| mbed_official | 31:42176bc3c368 | 807 | /** Peripheral FPTC base pointer */ |

| mbed_official | 31:42176bc3c368 | 808 | #define FPTC ((FGPIO_Type *)FPTC_BASE) |

| mbed_official | 31:42176bc3c368 | 809 | /** Peripheral FPTD base address */ |

| mbed_official | 31:42176bc3c368 | 810 | #define FPTD_BASE (0xF80FF0C0u) |

| mbed_official | 31:42176bc3c368 | 811 | /** Peripheral FPTD base pointer */ |

| mbed_official | 31:42176bc3c368 | 812 | #define FPTD ((FGPIO_Type *)FPTD_BASE) |

| mbed_official | 31:42176bc3c368 | 813 | /** Peripheral FPTE base address */ |

| mbed_official | 31:42176bc3c368 | 814 | #define FPTE_BASE (0xF80FF100u) |

| mbed_official | 31:42176bc3c368 | 815 | /** Peripheral FPTE base pointer */ |

| mbed_official | 31:42176bc3c368 | 816 | #define FPTE ((FGPIO_Type *)FPTE_BASE) |

| mbed_official | 31:42176bc3c368 | 817 | /** Array initializer of FGPIO peripheral base pointers */ |

| mbed_official | 31:42176bc3c368 | 818 | #define FGPIO_BASES { FPTA, FPTB, FPTC, FPTD, FPTE } |

| mbed_official | 31:42176bc3c368 | 819 | |

| mbed_official | 31:42176bc3c368 | 820 | /** |

| mbed_official | 31:42176bc3c368 | 821 | * @} |

| mbed_official | 31:42176bc3c368 | 822 | */ /* end of group FGPIO_Peripheral_Access_Layer */ |

| mbed_official | 31:42176bc3c368 | 823 | |

| mbed_official | 31:42176bc3c368 | 824 | |

| mbed_official | 31:42176bc3c368 | 825 | /* ---------------------------------------------------------------------------- |

| mbed_official | 31:42176bc3c368 | 826 | -- FTFA Peripheral Access Layer |

| mbed_official | 31:42176bc3c368 | 827 | ---------------------------------------------------------------------------- */ |

| mbed_official | 31:42176bc3c368 | 828 | |

| mbed_official | 31:42176bc3c368 | 829 | /** |

| mbed_official | 31:42176bc3c368 | 830 | * @addtogroup FTFA_Peripheral_Access_Layer FTFA Peripheral Access Layer |

| mbed_official | 31:42176bc3c368 | 831 | * @{ |

| mbed_official | 31:42176bc3c368 | 832 | */ |

| mbed_official | 31:42176bc3c368 | 833 | |

| mbed_official | 31:42176bc3c368 | 834 | /** FTFA - Register Layout Typedef */ |

| mbed_official | 31:42176bc3c368 | 835 | typedef struct { |

| mbed_official | 31:42176bc3c368 | 836 | __IO uint8_t FSTAT; /**< Flash Status Register, offset: 0x0 */ |

| mbed_official | 31:42176bc3c368 | 837 | __IO uint8_t FCNFG; /**< Flash Configuration Register, offset: 0x1 */ |

| mbed_official | 31:42176bc3c368 | 838 | __I uint8_t FSEC; /**< Flash Security Register, offset: 0x2 */ |

| mbed_official | 31:42176bc3c368 | 839 | __I uint8_t FOPT; /**< Flash Option Register, offset: 0x3 */ |

| mbed_official | 31:42176bc3c368 | 840 | __IO uint8_t FCCOB3; /**< Flash Common Command Object Registers, offset: 0x4 */ |

| mbed_official | 31:42176bc3c368 | 841 | __IO uint8_t FCCOB2; /**< Flash Common Command Object Registers, offset: 0x5 */ |

| mbed_official | 31:42176bc3c368 | 842 | __IO uint8_t FCCOB1; /**< Flash Common Command Object Registers, offset: 0x6 */ |

| mbed_official | 31:42176bc3c368 | 843 | __IO uint8_t FCCOB0; /**< Flash Common Command Object Registers, offset: 0x7 */ |

| mbed_official | 31:42176bc3c368 | 844 | __IO uint8_t FCCOB7; /**< Flash Common Command Object Registers, offset: 0x8 */ |

| mbed_official | 31:42176bc3c368 | 845 | __IO uint8_t FCCOB6; /**< Flash Common Command Object Registers, offset: 0x9 */ |

| mbed_official | 31:42176bc3c368 | 846 | __IO uint8_t FCCOB5; /**< Flash Common Command Object Registers, offset: 0xA */ |

| mbed_official | 31:42176bc3c368 | 847 | __IO uint8_t FCCOB4; /**< Flash Common Command Object Registers, offset: 0xB */ |

| mbed_official | 31:42176bc3c368 | 848 | __IO uint8_t FCCOBB; /**< Flash Common Command Object Registers, offset: 0xC */ |

| mbed_official | 31:42176bc3c368 | 849 | __IO uint8_t FCCOBA; /**< Flash Common Command Object Registers, offset: 0xD */ |

| mbed_official | 31:42176bc3c368 | 850 | __IO uint8_t FCCOB9; /**< Flash Common Command Object Registers, offset: 0xE */ |

| mbed_official | 31:42176bc3c368 | 851 | __IO uint8_t FCCOB8; /**< Flash Common Command Object Registers, offset: 0xF */ |

| mbed_official | 31:42176bc3c368 | 852 | __IO uint8_t FPROT3; /**< Program Flash Protection Registers, offset: 0x10 */ |

| mbed_official | 31:42176bc3c368 | 853 | __IO uint8_t FPROT2; /**< Program Flash Protection Registers, offset: 0x11 */ |

| mbed_official | 31:42176bc3c368 | 854 | __IO uint8_t FPROT1; /**< Program Flash Protection Registers, offset: 0x12 */ |

| mbed_official | 31:42176bc3c368 | 855 | __IO uint8_t FPROT0; /**< Program Flash Protection Registers, offset: 0x13 */ |

| mbed_official | 31:42176bc3c368 | 856 | } FTFA_Type; |

| mbed_official | 31:42176bc3c368 | 857 | |

| mbed_official | 31:42176bc3c368 | 858 | /* ---------------------------------------------------------------------------- |

| mbed_official | 31:42176bc3c368 | 859 | -- FTFA Register Masks |

| mbed_official | 31:42176bc3c368 | 860 | ---------------------------------------------------------------------------- */ |

| mbed_official | 31:42176bc3c368 | 861 | |

| mbed_official | 31:42176bc3c368 | 862 | /** |

| mbed_official | 31:42176bc3c368 | 863 | * @addtogroup FTFA_Register_Masks FTFA Register Masks |

| mbed_official | 31:42176bc3c368 | 864 | * @{ |

| mbed_official | 31:42176bc3c368 | 865 | */ |

| mbed_official | 31:42176bc3c368 | 866 | |

| mbed_official | 31:42176bc3c368 | 867 | /* FSTAT Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 868 | #define FTFA_FSTAT_MGSTAT0_MASK 0x1u |

| mbed_official | 31:42176bc3c368 | 869 | #define FTFA_FSTAT_MGSTAT0_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 870 | #define FTFA_FSTAT_FPVIOL_MASK 0x10u |

| mbed_official | 31:42176bc3c368 | 871 | #define FTFA_FSTAT_FPVIOL_SHIFT 4 |

| mbed_official | 31:42176bc3c368 | 872 | #define FTFA_FSTAT_ACCERR_MASK 0x20u |

| mbed_official | 31:42176bc3c368 | 873 | #define FTFA_FSTAT_ACCERR_SHIFT 5 |

| mbed_official | 31:42176bc3c368 | 874 | #define FTFA_FSTAT_RDCOLERR_MASK 0x40u |

| mbed_official | 31:42176bc3c368 | 875 | #define FTFA_FSTAT_RDCOLERR_SHIFT 6 |

| mbed_official | 31:42176bc3c368 | 876 | #define FTFA_FSTAT_CCIF_MASK 0x80u |

| mbed_official | 31:42176bc3c368 | 877 | #define FTFA_FSTAT_CCIF_SHIFT 7 |

| mbed_official | 31:42176bc3c368 | 878 | /* FCNFG Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 879 | #define FTFA_FCNFG_ERSSUSP_MASK 0x10u |

| mbed_official | 31:42176bc3c368 | 880 | #define FTFA_FCNFG_ERSSUSP_SHIFT 4 |

| mbed_official | 31:42176bc3c368 | 881 | #define FTFA_FCNFG_ERSAREQ_MASK 0x20u |

| mbed_official | 31:42176bc3c368 | 882 | #define FTFA_FCNFG_ERSAREQ_SHIFT 5 |

| mbed_official | 31:42176bc3c368 | 883 | #define FTFA_FCNFG_RDCOLLIE_MASK 0x40u |

| mbed_official | 31:42176bc3c368 | 884 | #define FTFA_FCNFG_RDCOLLIE_SHIFT 6 |

| mbed_official | 31:42176bc3c368 | 885 | #define FTFA_FCNFG_CCIE_MASK 0x80u |

| mbed_official | 31:42176bc3c368 | 886 | #define FTFA_FCNFG_CCIE_SHIFT 7 |

| mbed_official | 31:42176bc3c368 | 887 | /* FSEC Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 888 | #define FTFA_FSEC_SEC_MASK 0x3u |

| mbed_official | 31:42176bc3c368 | 889 | #define FTFA_FSEC_SEC_SHIFT 0 |

| mbed_official | 31:42176bc3c368 | 890 | #define FTFA_FSEC_SEC(x) (((uint8_t)(((uint8_t)(x))<<FTFA_FSEC_SEC_SHIFT))&FTFA_FSEC_SEC_MASK) |

| mbed_official | 31:42176bc3c368 | 891 | #define FTFA_FSEC_FSLACC_MASK 0xCu |

| mbed_official | 31:42176bc3c368 | 892 | #define FTFA_FSEC_FSLACC_SHIFT 2 |

| mbed_official | 31:42176bc3c368 | 893 | #define FTFA_FSEC_FSLACC(x) (((uint8_t)(((uint8_t)(x))<<FTFA_FSEC_FSLACC_SHIFT))&FTFA_FSEC_FSLACC_MASK) |

| mbed_official | 31:42176bc3c368 | 894 | #define FTFA_FSEC_MEEN_MASK 0x30u |

| mbed_official | 31:42176bc3c368 | 895 | #define FTFA_FSEC_MEEN_SHIFT 4 |

| mbed_official | 31:42176bc3c368 | 896 | #define FTFA_FSEC_MEEN(x) (((uint8_t)(((uint8_t)(x))<<FTFA_FSEC_MEEN_SHIFT))&FTFA_FSEC_MEEN_MASK) |

| mbed_official | 31:42176bc3c368 | 897 | #define FTFA_FSEC_KEYEN_MASK 0xC0u |

| mbed_official | 31:42176bc3c368 | 898 | #define FTFA_FSEC_KEYEN_SHIFT 6 |

| mbed_official | 31:42176bc3c368 | 899 | #define FTFA_FSEC_KEYEN(x) (((uint8_t)(((uint8_t)(x))<<FTFA_FSEC_KEYEN_SHIFT))&FTFA_FSEC_KEYEN_MASK) |

| mbed_official | 31:42176bc3c368 | 900 | /* FOPT Bit Fields */ |

| mbed_official | 31:42176bc3c368 | 901 | #define FTFA_FOPT_OPT_MASK 0xFFu |