Nucleo-F303K8 HSE Clock

Trouble

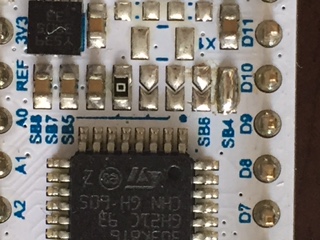

Nucleo-F303K8 board can change a system clock setting using a hardware configuration as follows.

| MODE | SB4 | SB6 | REMARKS |

|---|---|---|---|

| HSI (Internal CR Osc) | OPEN | SHORT | -2.8% to +3.8% accuracy at -40 to 150 degC |

| HSE(8MHz MCO from I/F chip) | SHORT | OPEN | *Not Xtal mode (I have NOT check this configuration) |

Trouble is that SB4=Short, SB6=open configuration cannot start HSE mode and stay in HSI mode.

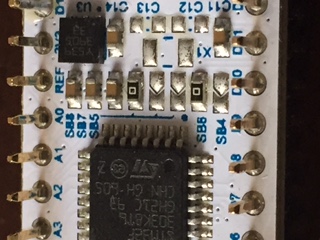

............................Original...................................................................... Modified...........................

Solution

I'm not sure but need to modify following file.

\targets\TARGET_STM\TARGET_STM32F3\device\stm32f3xx_hal_rcc.c

During transient between HSIand PLL to HSE PLL, system needs to disable PLL.

Current control program cannot take over the system clock from HSI+PLL to HSE+PLL then return without successful condition.

Tentative solution

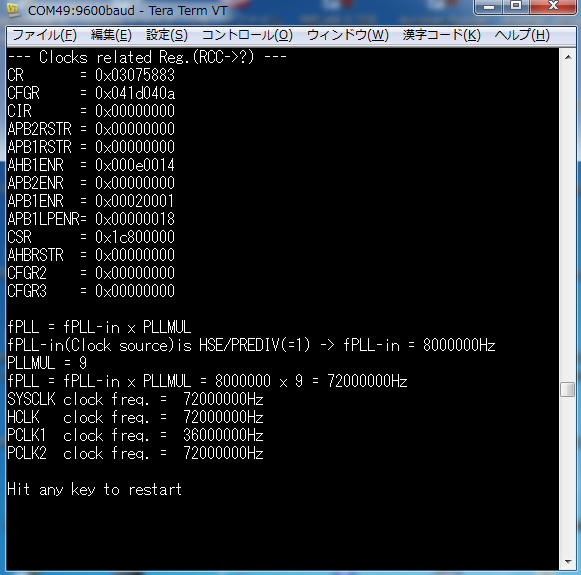

Start form HSI+PLL then set HSI without PLL (8MHz clock), after those step change to HSE+PLL

Import programcheck_SysClk_for_F303K8

Check program for STM32F303K8 System Clock

Permanent solution

I would like to ask ST team to improve this issue.

ST team point of view, this is not a bug but specification.

Because you can see following program.

When PLL is running, following program give up PLL setting.

\targets\TARGET_STM\TARGET_STM32F3\device\stm32f3xx_hal_rcc.c

HAL_StatusTypeDef HAL_RCC_OscConfig(RCC_OscInitTypeDef *RCC_OscInitStruct)

{

; // Omitted

/*-------------------------------- PLL Configuration -----------------------*/

/* Check the parameters */

assert_param(IS_RCC_PLL(RCC_OscInitStruct->PLL.PLLState));

if ((RCC_OscInitStruct->PLL.PLLState) != RCC_PLL_NONE)

{

/* Check if the PLL is used as system clock or not */

if(__HAL_RCC_GET_SYSCLK_SOURCE() != RCC_SYSCLKSOURCE_STATUS_PLLCLK)

{

; // Omitted

}

else

{

return HAL_ERROR;

}

return HAL_OK;

}

I hope they can put good code into line 18 to resetting PLL even PLL is running.

Thanks in advance.

Please log in to post comments.