Check System frequency of Nucleo F411RE board. Also F401RE.

<May 12th, 2015>

I have confirmed that both mbed lib. and mbed-src lib. have updated to change F411RE mbed System clock and USB clock as below.

fVCO = fPLL-in x (PLLN/PLLM), fPLL-out = fVCO/PLLP, fUSB-out = fVCO/PLLQ Use PLL with PLLN=192, PLLM=4 Use HSE(not Xtal but External Clock)=8000000Hz PLL/Base freq= 384000000Hz Use PLL with PLLP=4, PLLQ=8 PLL/System freq= 96000000Hz PLL/USB freq= 48000000Hz SYSCLK clock freq. = 96000000Hz HCLK clock freq. = 96000000Hz PCLK1 clock freq. = 48000000Hz PCLK2 clock freq. = 96000000Hz

mbed lib. Rev. -> 98 & mbed-src lib. Rev. ->539

We can use USB with proper colok!.

If you would like to use 100MHz System clock, please refer updated "Nucleo_F411RE_SysClk".

--------

I made a clock checking program for Nucleo F411RE and F401 mbed board.

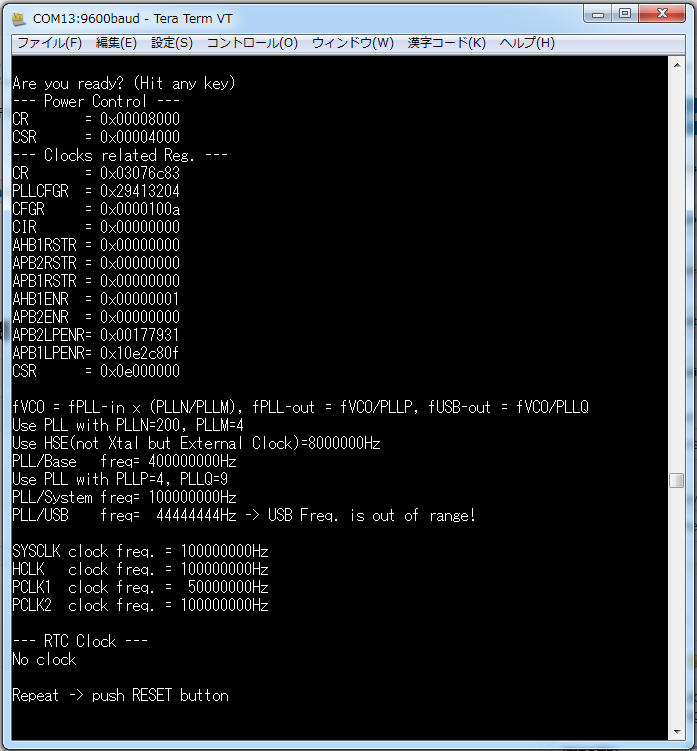

Picture shows F411RE example.

System frequency is 100MHz. Looks okay for me.

USB frequency is 44.4MHz? -> USB clock needs accurate frequency 48MHz.

Once keeping 100MHz system clock freq., we can select PLLQ value only 9 or 8.

If PLLQ=9, USB Freq. is 44.4MHz (current setting).

If PLLQ=8, USB Freq. is 50.0MHz.

Best selection looks follows.

PLL clock -> HSE = 8MHz

PLLN= 192, PLLM = 4

PLL Freq. = (PLL Clock)*(PLLN/PLLM) = 8MHz * 192 / 4 = 384MHz

System clock = (PLL Freq.)/PLLP = 384MHz/4 = 96MHz

USB clock = (PLL Freq.)/PLLQ = 384MHz/8 = 48MHz

Is this result okay?

or

Is my program wrong?

Revision 2:e530159dd7aa, committed 2015-05-12

- Comitter:

- kenjiArai

- Date:

- Tue May 12 10:20:38 2015 +0000

- Parent:

- 1:2d6d2ccd87f8

- Commit message:

- Added note text

Changed in this revision

| mbed.bld | Show annotated file Show diff for this revision Revisions of this file |

| sys_clock_100MHz_note.h | Show annotated file Show diff for this revision Revisions of this file |

diff -r 2d6d2ccd87f8 -r e530159dd7aa mbed.bld --- a/mbed.bld Sun Nov 02 05:11:28 2014 +0000 +++ b/mbed.bld Tue May 12 10:20:38 2015 +0000 @@ -1,1 +1,1 @@ -http://mbed.org/users/mbed_official/code/mbed/builds/031413cf7a89 \ No newline at end of file +http://mbed.org/users/mbed_official/code/mbed/builds/8ab26030e058 \ No newline at end of file

diff -r 2d6d2ccd87f8 -r e530159dd7aa sys_clock_100MHz_note.h

--- /dev/null Thu Jan 01 00:00:00 1970 +0000

+++ b/sys_clock_100MHz_note.h Tue May 12 10:20:38 2015 +0000

@@ -0,0 +1,55 @@

+/*

+ * mbed Application program for the mbed

+ * Nucleo F411RE USB clock sets 48MHz

+ *

+ * Copyright (c) 2015 Kenji Arai / JH1PJL

+ * http://www.page.sannet.ne.jp/kenjia/index.html

+ * http://mbed.org/users/kenjiArai/

+ * Created: May 12th, 2015

+ * Revised: May 12th, 2015

+ *

+ * THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR IMPLIED,

+ * INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE

+ * AND NONINFRINGEMENT. IN NO EVENT SHALL THE AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM,

+ * DAMAGES OR OTHER LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM,

+ * OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE SOFTWARE.

+ */

+

+#if 0

+// file: /mbed-src/targets/cmsis/TARGET_STM/TARGET_STM32F4/TARGET_NUCLEO_F411RE/system_stmf4xx.c

+// line: 611 and floows

+

+<Original>

+ RCC_OscInitStruct.PLL.PLLState = RCC_PLL_ON;

+ RCC_OscInitStruct.PLL.PLLSource = RCC_PLLSOURCE_HSE;

+ //RCC_OscInitStruct.PLL.PLLM = 8; // VCO input clock = 1 MHz (8 MHz / 8)

+ //RCC_OscInitStruct.PLL.PLLN = 384; // VCO output clock = 384 MHz (1 MHz * 384)

+ RCC_OscInitStruct.PLL.PLLM = 4; // VCO input clock = 2 MHz (8 MHz / 4)

+ RCC_OscInitStruct.PLL.PLLN = 192; // VCO output clock = 384 MHz (2 MHz * 192)

+ RCC_OscInitStruct.PLL.PLLP = RCC_PLLP_DIV4; // PLLCLK = 96 MHz (384 MHz / 4)

+ RCC_OscInitStruct.PLL.PLLQ = 8; // USB clock = 48 MHz (384 MHz / 8) --> Good for USB

+ if (HAL_RCC_OscConfig(&RCC_OscInitStruct) != HAL_OK)

+ {

+ return 0; // FAIL

+ }

+

+<Modified>

+ RCC_OscInitStruct.PLL.PLLState = RCC_PLL_ON;

+ RCC_OscInitStruct.PLL.PLLSource = RCC_PLLSOURCE_HSE;

+ //RCC_OscInitStruct.PLL.PLLM = 8; // VCO input clock = 1 MHz (8 MHz / 8)

+ //RCC_OscInitStruct.PLL.PLLN = 384; // VCO output clock = 384 MHz (1 MHz * 384)

+ RCC_OscInitStruct.PLL.PLLM = 4; // VCO input clock = 2 MHz (8 MHz / 4)

+#if 0

+ RCC_OscInitStruct.PLL.PLLN = 192; // VCO output clock = 384 MHz (2 MHz * 192)

+ RCC_OscInitStruct.PLL.PLLP = RCC_PLLP_DIV4; // PLLCLK = 96 MHz (384 MHz / 4)

+ RCC_OscInitStruct.PLL.PLLQ = 8; // USB clock = 48 MHz (384 MHz / 8) --> Good for USB

+#else

+ RCC_OscInitStruct.PLL.PLLN = 200; // VCO output clock = 400 MHz (2 MHz * 200)

+ RCC_OscInitStruct.PLL.PLLP = RCC_PLLP_DIV4; // PLLCLK = 100 MHz (400 MHz / 4)

+ RCC_OscInitStruct.PLL.PLLQ = 9; // USB clock = 44.44 MHz (400 MHz / 9) --> Bad for USB

+#endif

+ if (HAL_RCC_OscConfig(&RCC_OscInitStruct) != HAL_OK)

+ {

+ return 0; // FAIL

+ }

+#endif

\ No newline at end of file