The official mbed C/C SDK provides the software platform and libraries to build your applications.

Fork of mbed by

(01.May.2014) started sales! http://www.switch-science.com/catalog/1717/

(13.March.2014) updated to 0.5.0

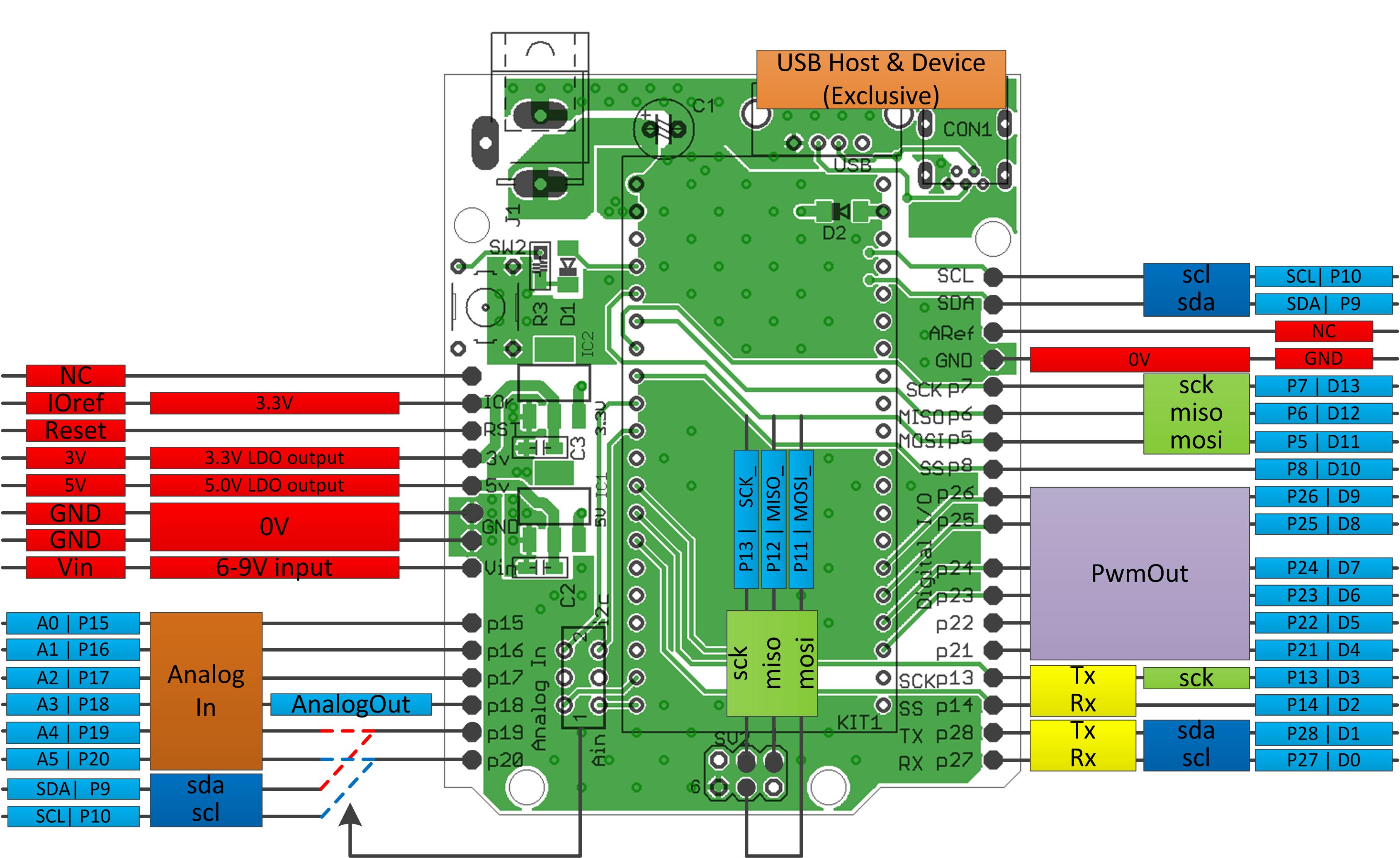

This is a pin conversion PCB from mbed 1768/11U24 to arduino UNO.

- So if you have both mbed and arduino shields, I guess you would be happy with such a conversion board :)

Photos

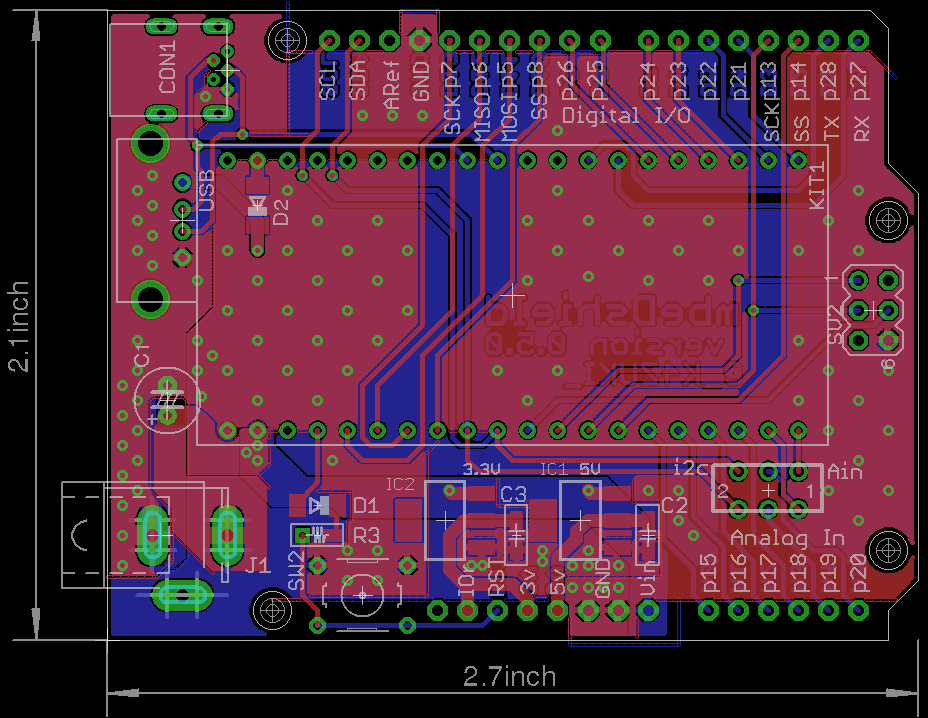

- Board photo vvv

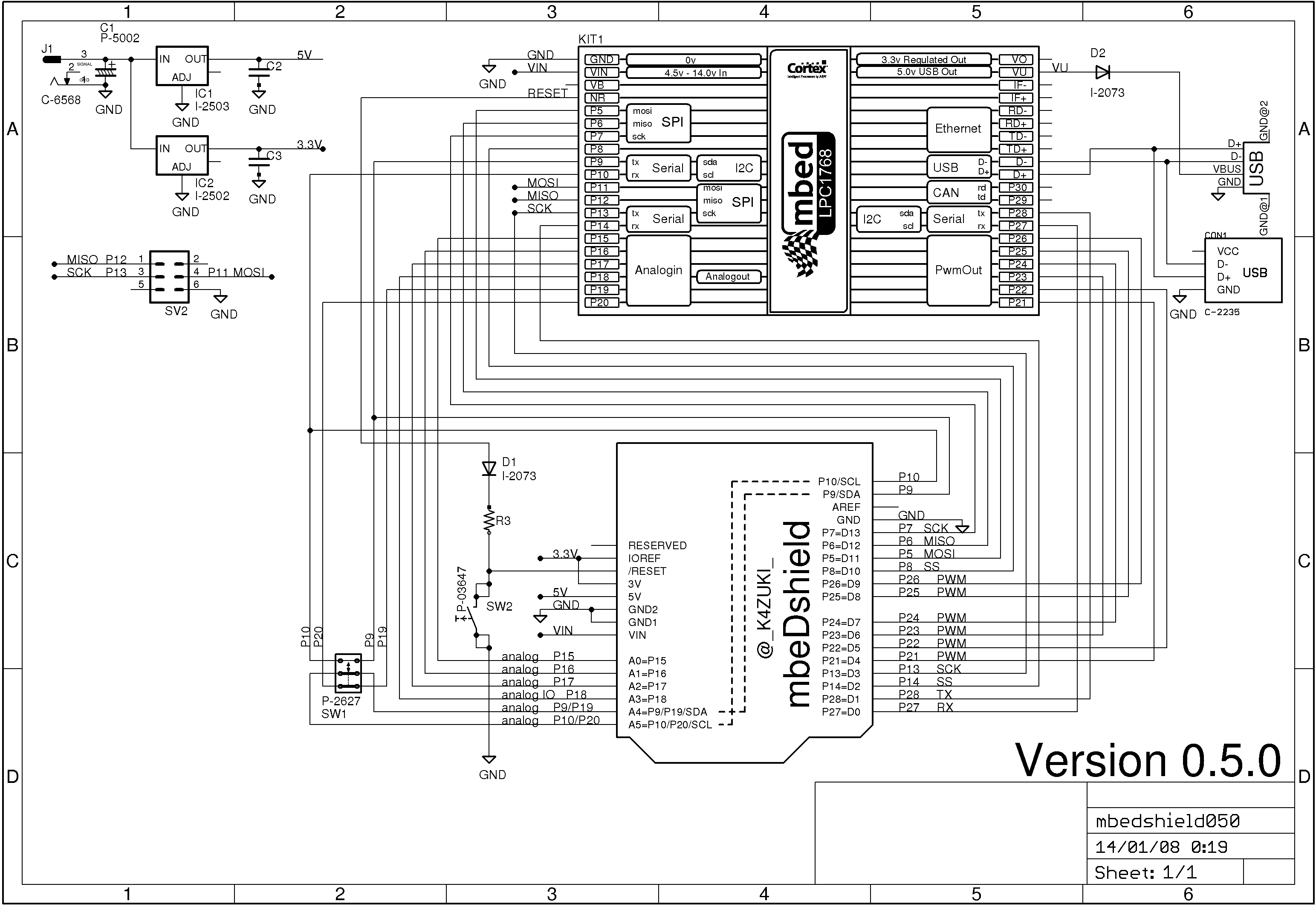

- Schematic photo vvv

- Functionality photo vvv

Latest eagle files

PCB >> /media/uploads/k4zuki/mbedshield050.brd

SCH >> /media/uploads/k4zuki/mbedshield050.sch

BIG changes from previous version

- Ethernet RJ45 connector is removed.

- http://mbed.org/components/Seeed-Ethernet-Shield-V20/ is the biggest hint to use Ethernet!

MostALL of components can be bought at Akizuki http://akizukidenshi.com/- But sorry, they do not send parts to abroad

- Pinout is changed!

| arduino | 0.4.0 | 0.5.0 |

|---|---|---|

| D4 | p12 | p21 |

| D5 | p11 | p22 |

| MOSI_ | none | p11 |

| MISO_ | none | p12 |

| SCK_ | none | p13 |

This design has bug(s)

- I2C functional pin differs between 1768 and 11U24.

Fixed bugs here

- MiniUSB cable cannot be connected on mbed if you solder high-height electrolytic capacitor on C3.

- http://akizukidenshi.com/catalog/g/gP-05002/ is the solution to make this 100% AKIZUKI parts!

- the 6-pin ISP port is not inprimented in version 0.4.0

it will be fixed in later version 0.4.1/0.4.2/0.5.0This has beenfixed

I am doing some porting to use existing arduino shields but it may faster if you do it by yourself...

you can use arduino PinName "A0-A5,D0-D13" plus backside SPI port for easier porting.

To do this you have to edit PinName enum in

- "mbed/TARGET_LPC1768/PinNames.h" or

- "mbed/TARGET_LPC11U24/PinNames.h" as per your target mbed.

here is the actual list: This list includes define switch to switch pin assignment

part_of_PinNames.h

USBTX = P0_2,

USBRX = P0_3,

//from here mbeDshield mod

D0=p27,

D1=p28,

D2=p14,

D3=p13,

#ifdef MBEDSHIELD_050

MOSI_=p11,

MISO_=p12,

SCK_=p13,

D4=p21,

D5=p22,

#else

D4=p12,

D5=p11,

#endif

D6=p23,

D7=p24,

D8=p25,

D9=p26,

D10=p8,

D11=p5,

D12=p6,

D13=p7,

A0=p15,

A1=p16,

A2=p17,

A3=p18,

A4=p19,

A5=p20,

SDA=p9,

SCL=p10,

//mbeDshield mod ends here

// Not connected

NC = (int)0xFFFFFFFF

TARGET_LPC1768/TOOLCHAIN_GCC_CR/LPC1768.ld@64:e3affc9e7238, 2013-08-05 (annotated)

- Committer:

- bogdanm

- Date:

- Mon Aug 05 12:28:09 2013 +0300

- Revision:

- 64:e3affc9e7238

- Parent:

- LPC1768/GCC_CR/LPC1768.ld@27:7110ebee3484

- Child:

- 65:5798e58a58b1

New build system structure, new target (LPC1347), bug fixes (I2C read/write errors, LPC11U24 memory map and others)

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| emilmont | 27:7110ebee3484 | 1 | /* mbed - LPC1768 linker script |

| emilmont | 27:7110ebee3484 | 2 | * Based linker script generated by Code Red Technologies Red Suite 4.1 |

| emilmont | 27:7110ebee3484 | 3 | */ |

| emilmont | 27:7110ebee3484 | 4 | GROUP(libgcc.a libc.a libstdc++.a libm.a libcr_newlib_nohost.a crti.o crtn.o crtbegin.o crtend.o) |

| emilmont | 27:7110ebee3484 | 5 | |

| emilmont | 27:7110ebee3484 | 6 | MEMORY |

| emilmont | 27:7110ebee3484 | 7 | { |

| emilmont | 27:7110ebee3484 | 8 | /* Define each memory region */ |

| emilmont | 27:7110ebee3484 | 9 | MFlash512 (rx) : ORIGIN = 0x0, LENGTH = 0x80000 /* 512k */ |

| emilmont | 27:7110ebee3484 | 10 | RamLoc32 (rwx) : ORIGIN = 0x100000C8, LENGTH = 0x7F38 /* 32k */ |

| emilmont | 27:7110ebee3484 | 11 | RamAHB32 (rwx) : ORIGIN = 0x2007c000, LENGTH = 0x8000 /* 32k */ |

| emilmont | 27:7110ebee3484 | 12 | |

| emilmont | 27:7110ebee3484 | 13 | } |

| emilmont | 27:7110ebee3484 | 14 | /* Define a symbol for the top of each memory region */ |

| emilmont | 27:7110ebee3484 | 15 | __top_MFlash512 = 0x0 + 0x80000; |

| emilmont | 27:7110ebee3484 | 16 | __top_RamLoc32 = 0x10000000 + 0x8000; |

| emilmont | 27:7110ebee3484 | 17 | __top_RamAHB32 = 0x2007c000 + 0x8000; |

| emilmont | 27:7110ebee3484 | 18 | |

| emilmont | 27:7110ebee3484 | 19 | ENTRY(ResetISR) |

| emilmont | 27:7110ebee3484 | 20 | |

| emilmont | 27:7110ebee3484 | 21 | SECTIONS |

| emilmont | 27:7110ebee3484 | 22 | { |

| emilmont | 27:7110ebee3484 | 23 | |

| emilmont | 27:7110ebee3484 | 24 | /* MAIN TEXT SECTION */ |

| emilmont | 27:7110ebee3484 | 25 | .text : ALIGN(4) |

| emilmont | 27:7110ebee3484 | 26 | { |

| emilmont | 27:7110ebee3484 | 27 | FILL(0xff) |

| emilmont | 27:7110ebee3484 | 28 | KEEP(*(.isr_vector)) |

| emilmont | 27:7110ebee3484 | 29 | |

| emilmont | 27:7110ebee3484 | 30 | /* Global Section Table */ |

| emilmont | 27:7110ebee3484 | 31 | . = ALIGN(4) ; |

| emilmont | 27:7110ebee3484 | 32 | __section_table_start = .; |

| emilmont | 27:7110ebee3484 | 33 | __data_section_table = .; |

| emilmont | 27:7110ebee3484 | 34 | LONG(LOADADDR(.data)); |

| emilmont | 27:7110ebee3484 | 35 | LONG( ADDR(.data)) ; |

| emilmont | 27:7110ebee3484 | 36 | LONG( SIZEOF(.data)); |

| emilmont | 27:7110ebee3484 | 37 | LONG(LOADADDR(.data_RAM2)); |

| emilmont | 27:7110ebee3484 | 38 | LONG( ADDR(.data_RAM2)) ; |

| emilmont | 27:7110ebee3484 | 39 | LONG( SIZEOF(.data_RAM2)); |

| emilmont | 27:7110ebee3484 | 40 | __data_section_table_end = .; |

| emilmont | 27:7110ebee3484 | 41 | __bss_section_table = .; |

| emilmont | 27:7110ebee3484 | 42 | LONG( ADDR(.bss)); |

| emilmont | 27:7110ebee3484 | 43 | LONG( SIZEOF(.bss)); |

| emilmont | 27:7110ebee3484 | 44 | LONG( ADDR(.bss_RAM2)); |

| emilmont | 27:7110ebee3484 | 45 | LONG( SIZEOF(.bss_RAM2)); |

| emilmont | 27:7110ebee3484 | 46 | __bss_section_table_end = .; |

| emilmont | 27:7110ebee3484 | 47 | __section_table_end = . ; |

| emilmont | 27:7110ebee3484 | 48 | /* End of Global Section Table */ |

| emilmont | 27:7110ebee3484 | 49 | |

| emilmont | 27:7110ebee3484 | 50 | |

| emilmont | 27:7110ebee3484 | 51 | *(.after_vectors*) |

| emilmont | 27:7110ebee3484 | 52 | |

| emilmont | 27:7110ebee3484 | 53 | *(.text*) |

| emilmont | 27:7110ebee3484 | 54 | *(.rodata .rodata.*) |

| emilmont | 27:7110ebee3484 | 55 | . = ALIGN(4); |

| emilmont | 27:7110ebee3484 | 56 | |

| emilmont | 27:7110ebee3484 | 57 | /* C++ constructors etc */ |

| emilmont | 27:7110ebee3484 | 58 | . = ALIGN(4); |

| emilmont | 27:7110ebee3484 | 59 | KEEP(*(.init)) |

| emilmont | 27:7110ebee3484 | 60 | |

| emilmont | 27:7110ebee3484 | 61 | . = ALIGN(4); |

| emilmont | 27:7110ebee3484 | 62 | __preinit_array_start = .; |

| emilmont | 27:7110ebee3484 | 63 | KEEP (*(.preinit_array)) |

| emilmont | 27:7110ebee3484 | 64 | __preinit_array_end = .; |

| emilmont | 27:7110ebee3484 | 65 | |

| emilmont | 27:7110ebee3484 | 66 | . = ALIGN(4); |

| emilmont | 27:7110ebee3484 | 67 | __init_array_start = .; |

| emilmont | 27:7110ebee3484 | 68 | KEEP (*(SORT(.init_array.*))) |

| emilmont | 27:7110ebee3484 | 69 | KEEP (*(.init_array)) |

| emilmont | 27:7110ebee3484 | 70 | __init_array_end = .; |

| emilmont | 27:7110ebee3484 | 71 | |

| emilmont | 27:7110ebee3484 | 72 | KEEP(*(.fini)); |

| emilmont | 27:7110ebee3484 | 73 | |

| emilmont | 27:7110ebee3484 | 74 | . = ALIGN(0x4); |

| emilmont | 27:7110ebee3484 | 75 | KEEP (*crtbegin.o(.ctors)) |

| emilmont | 27:7110ebee3484 | 76 | KEEP (*(EXCLUDE_FILE (*crtend.o) .ctors)) |

| emilmont | 27:7110ebee3484 | 77 | KEEP (*(SORT(.ctors.*))) |

| emilmont | 27:7110ebee3484 | 78 | KEEP (*crtend.o(.ctors)) |

| emilmont | 27:7110ebee3484 | 79 | |

| emilmont | 27:7110ebee3484 | 80 | . = ALIGN(0x4); |

| emilmont | 27:7110ebee3484 | 81 | KEEP (*crtbegin.o(.dtors)) |

| emilmont | 27:7110ebee3484 | 82 | KEEP (*(EXCLUDE_FILE (*crtend.o) .dtors)) |

| emilmont | 27:7110ebee3484 | 83 | KEEP (*(SORT(.dtors.*))) |

| emilmont | 27:7110ebee3484 | 84 | KEEP (*crtend.o(.dtors)) |

| emilmont | 27:7110ebee3484 | 85 | /* End C++ */ |

| emilmont | 27:7110ebee3484 | 86 | } > MFlash512 |

| emilmont | 27:7110ebee3484 | 87 | |

| emilmont | 27:7110ebee3484 | 88 | /* |

| emilmont | 27:7110ebee3484 | 89 | * for exception handling/unwind - some Newlib functions (in common |

| emilmont | 27:7110ebee3484 | 90 | * with C++ and STDC++) use this. |

| emilmont | 27:7110ebee3484 | 91 | */ |

| emilmont | 27:7110ebee3484 | 92 | .ARM.extab : ALIGN(4) |

| emilmont | 27:7110ebee3484 | 93 | { |

| emilmont | 27:7110ebee3484 | 94 | *(.ARM.extab* .gnu.linkonce.armextab.*) |

| emilmont | 27:7110ebee3484 | 95 | } > MFlash512 |

| emilmont | 27:7110ebee3484 | 96 | __exidx_start = .; |

| emilmont | 27:7110ebee3484 | 97 | |

| emilmont | 27:7110ebee3484 | 98 | .ARM.exidx : ALIGN(4) |

| emilmont | 27:7110ebee3484 | 99 | { |

| emilmont | 27:7110ebee3484 | 100 | *(.ARM.exidx* .gnu.linkonce.armexidx.*) |

| emilmont | 27:7110ebee3484 | 101 | } > MFlash512 |

| emilmont | 27:7110ebee3484 | 102 | __exidx_end = .; |

| emilmont | 27:7110ebee3484 | 103 | |

| emilmont | 27:7110ebee3484 | 104 | _etext = .; |

| emilmont | 27:7110ebee3484 | 105 | |

| emilmont | 27:7110ebee3484 | 106 | |

| emilmont | 27:7110ebee3484 | 107 | .data_RAM2 : ALIGN(4) |

| emilmont | 27:7110ebee3484 | 108 | { |

| emilmont | 27:7110ebee3484 | 109 | FILL(0xff) |

| emilmont | 27:7110ebee3484 | 110 | *(.data.$RAM2*) |

| emilmont | 27:7110ebee3484 | 111 | *(.data.$RamAHB32*) |

| emilmont | 27:7110ebee3484 | 112 | . = ALIGN(4) ; |

| emilmont | 27:7110ebee3484 | 113 | } > RamAHB32 AT>MFlash512 |

| emilmont | 27:7110ebee3484 | 114 | |

| emilmont | 27:7110ebee3484 | 115 | /* MAIN DATA SECTION */ |

| emilmont | 27:7110ebee3484 | 116 | |

| emilmont | 27:7110ebee3484 | 117 | .uninit_RESERVED : ALIGN(4) |

| emilmont | 27:7110ebee3484 | 118 | { |

| emilmont | 27:7110ebee3484 | 119 | KEEP(*(.bss.$RESERVED*)) |

| emilmont | 27:7110ebee3484 | 120 | } > RamLoc32 |

| emilmont | 27:7110ebee3484 | 121 | |

| emilmont | 27:7110ebee3484 | 122 | .data : ALIGN(4) |

| emilmont | 27:7110ebee3484 | 123 | { |

| emilmont | 27:7110ebee3484 | 124 | FILL(0xff) |

| emilmont | 27:7110ebee3484 | 125 | _data = .; |

| emilmont | 27:7110ebee3484 | 126 | *(vtable) |

| emilmont | 27:7110ebee3484 | 127 | *(.data*) |

| emilmont | 27:7110ebee3484 | 128 | . = ALIGN(4) ; |

| emilmont | 27:7110ebee3484 | 129 | _edata = .; |

| emilmont | 27:7110ebee3484 | 130 | } > RamLoc32 AT>MFlash512 |

| emilmont | 27:7110ebee3484 | 131 | |

| emilmont | 27:7110ebee3484 | 132 | |

| emilmont | 27:7110ebee3484 | 133 | .bss_RAM2 : ALIGN(4) |

| emilmont | 27:7110ebee3484 | 134 | { |

| emilmont | 27:7110ebee3484 | 135 | *(.bss.$RAM2*) |

| emilmont | 27:7110ebee3484 | 136 | *(.bss.$RamAHB32*) |

| emilmont | 27:7110ebee3484 | 137 | . = ALIGN(4) ; |

| emilmont | 27:7110ebee3484 | 138 | } > RamAHB32 |

| emilmont | 27:7110ebee3484 | 139 | |

| emilmont | 27:7110ebee3484 | 140 | /* MAIN BSS SECTION */ |

| emilmont | 27:7110ebee3484 | 141 | .bss : ALIGN(4) |

| emilmont | 27:7110ebee3484 | 142 | { |

| emilmont | 27:7110ebee3484 | 143 | _bss = .; |

| emilmont | 27:7110ebee3484 | 144 | *(.bss*) |

| emilmont | 27:7110ebee3484 | 145 | *(COMMON) |

| emilmont | 27:7110ebee3484 | 146 | . = ALIGN(4) ; |

| emilmont | 27:7110ebee3484 | 147 | _ebss = .; |

| emilmont | 27:7110ebee3484 | 148 | PROVIDE(end = .); |

| emilmont | 27:7110ebee3484 | 149 | } > RamLoc32 |

| emilmont | 27:7110ebee3484 | 150 | |

| emilmont | 27:7110ebee3484 | 151 | PROVIDE(_pvHeapStart = .); |

| emilmont | 27:7110ebee3484 | 152 | PROVIDE(_vStackTop = __top_RamLoc32 - 0); |

| emilmont | 27:7110ebee3484 | 153 | } |