BLACKPILL custom target.

BLACKPILL custom target

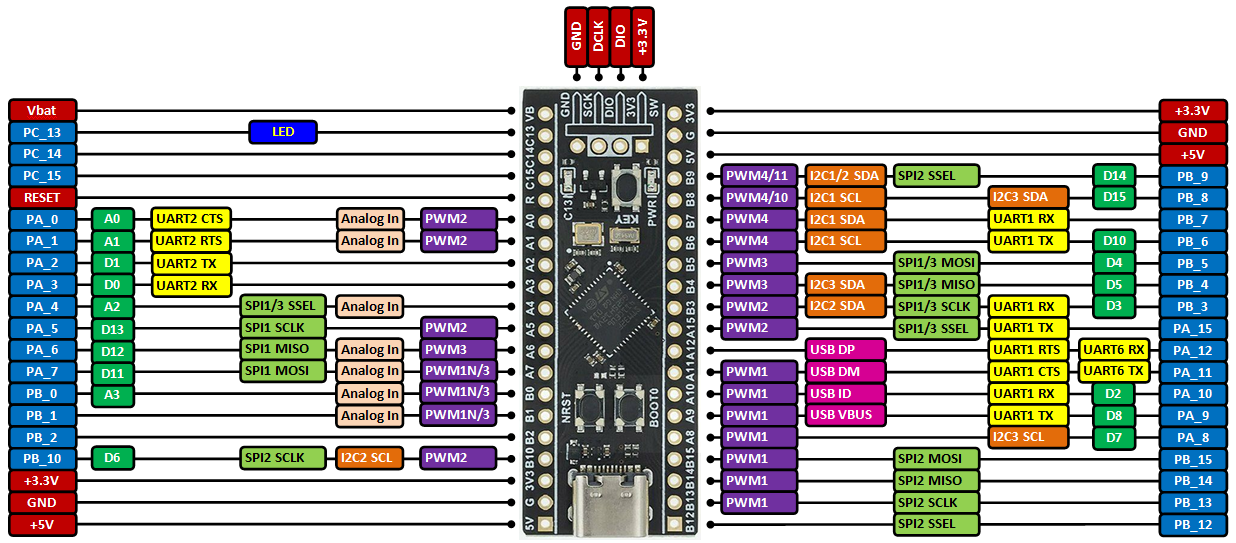

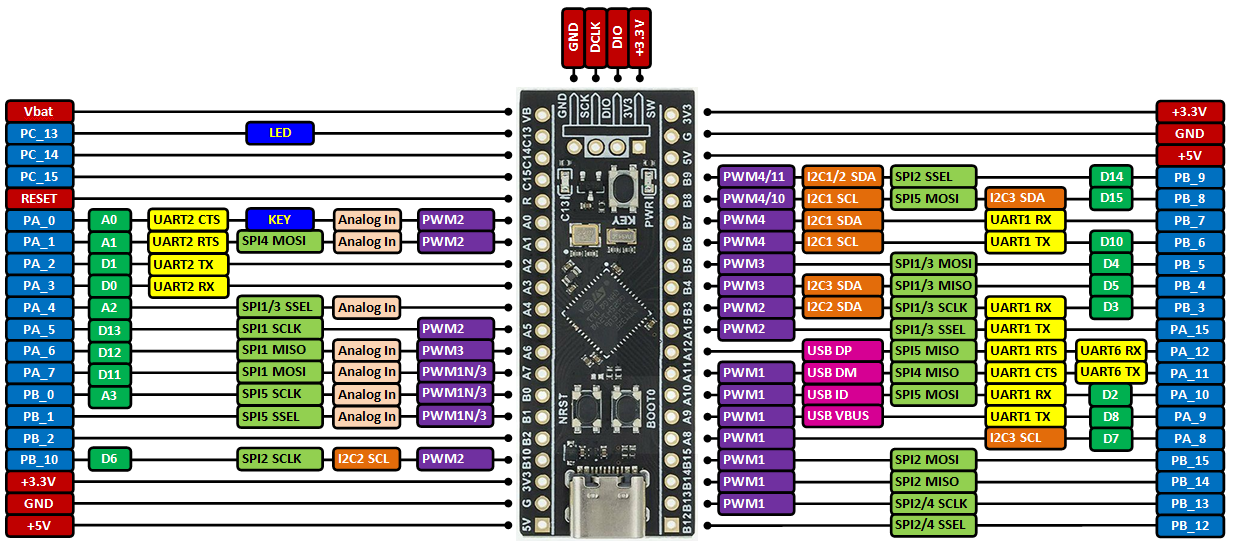

Board pinout

When equipped with STM32F401CCU6:

When equipped with STM32F411CEU6:

Advantages of the BLACKPILL custom target over the NUCLEO_F401RE/ NUCLEO_F411RE

- The onboard external 25 MHz crystal is used as system clock source rather than the less precise internal 16 MHz RC oscillator.

- The onboard LED works as LED1 in programs.

- The onboard KEY on STM32F411CEU6 boards works as USER_BUTTON pin in programs.

- You can use the USB peripheral in your programs and connect the board to the PC over the onboard USB connector. An example of using the USB peripheral as USBSerial (12 Mbit/s) is available here.

Building programs for the BLACKPILL custom target in Mbed Studio

- Connect an STM32 ST-Link programmer to your BLACKPILL board and PC (see below for more details).

- Create a new program in the Mbed Studio IDE.

- Right-click on the program's root folder and in the popup window select

Add library...

- Copy&paste the text https://os.mbed.com/users/hudakz/code/BLACKPILL_Custom_Target into the

Git or os.mbed.com URLedit box and click on theNextbutton.

- Open the drop-list and select

defaultasBranch or tagand click on theFinishbutton.

- Open the

BLACKPILL_Custom_Targetfolder and according to you board drag&drop theTARGET_BLACKPILL_F401CCor theTARGET_BLACKPILL_F411CEfolder and thecustom_targets.jsonfile one by one to the root folder of your program.

- Delete the

BLACKPILL_Custom_Targetfolder from your project. (Right-click and select delete).

- Open the

Targetdrop-list and click on the button with a "chip" icon on it (Manage custom targets) .

- Open the

USB devicedrop-list and select your STM32 ST-Link programmer.

- Open the

Build targetdrop-list and according to your board selectBLACKPILL_F401CCorBLACKPILL_F411CE.

- Click on the

Save Allbutton.

- Build your program (click on hammer button).

For more info visit

Import programBlackpill_Hello

Using low cost Blackpill (STM32F411CEU6) boards with mbed.

TARGET_BLACKPILL_F401CC/system_clock.c@7:3a74f7149fa4, 2022-03-19 (annotated)

- Committer:

- hudakz

- Date:

- Sat Mar 19 10:08:40 2022 +0000

- Revision:

- 7:3a74f7149fa4

Added support for boards equipped with STM32F401CC.

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| hudakz | 7:3a74f7149fa4 | 1 | /* mbed Microcontroller Library |

| hudakz | 7:3a74f7149fa4 | 2 | * SPDX-License-Identifier: BSD-3-Clause |

| hudakz | 7:3a74f7149fa4 | 3 | ****************************************************************************** |

| hudakz | 7:3a74f7149fa4 | 4 | * |

| hudakz | 7:3a74f7149fa4 | 5 | * Copyright (c) 2015-2021 STMicroelectronics. |

| hudakz | 7:3a74f7149fa4 | 6 | * All rights reserved. |

| hudakz | 7:3a74f7149fa4 | 7 | * |

| hudakz | 7:3a74f7149fa4 | 8 | * This software component is licensed by ST under BSD 3-Clause license, |

| hudakz | 7:3a74f7149fa4 | 9 | * the "License"; You may not use this file except in compliance with the |

| hudakz | 7:3a74f7149fa4 | 10 | * License. You may obtain a copy of the License at: |

| hudakz | 7:3a74f7149fa4 | 11 | * opensource.org/licenses/BSD-3-Clause |

| hudakz | 7:3a74f7149fa4 | 12 | * |

| hudakz | 7:3a74f7149fa4 | 13 | ****************************************************************************** |

| hudakz | 7:3a74f7149fa4 | 14 | */ |

| hudakz | 7:3a74f7149fa4 | 15 | |

| hudakz | 7:3a74f7149fa4 | 16 | /** |

| hudakz | 7:3a74f7149fa4 | 17 | * This file configures the system clock as follows: |

| hudakz | 7:3a74f7149fa4 | 18 | *---------------------------------------------------------------------- |

| hudakz | 7:3a74f7149fa4 | 19 | * System clock source | 1- USE_PLL_HSE_XTAL | 2- USE_PLL_HSI |

| hudakz | 7:3a74f7149fa4 | 20 | * (external 25 MHz xtal) | (internal 16 MHz) |

| hudakz | 7:3a74f7149fa4 | 21 | *---------------------------------------------------------------------- |

| hudakz | 7:3a74f7149fa4 | 22 | * USB enabled | NO | YES | NO | YES |

| hudakz | 7:3a74f7149fa4 | 23 | *---------------------------------------------------------------------- |

| hudakz | 7:3a74f7149fa4 | 24 | * SYSCLK(MHz) | 100 | 96 | 100 | 96 |

| hudakz | 7:3a74f7149fa4 | 25 | * AHBCLK (MHz) | 100 | 96 | 100 | 96 |

| hudakz | 7:3a74f7149fa4 | 26 | * APB1CLK (MHz) | 50 | 48 | 50 | 48 |

| hudakz | 7:3a74f7149fa4 | 27 | * APB2CLK (MHz) | 100 | 96 | 100 | 96 |

| hudakz | 7:3a74f7149fa4 | 28 | *---------------------------------------------------------------------- |

| hudakz | 7:3a74f7149fa4 | 29 | **/ |

| hudakz | 7:3a74f7149fa4 | 30 | |

| hudakz | 7:3a74f7149fa4 | 31 | #include "stm32f4xx.h" |

| hudakz | 7:3a74f7149fa4 | 32 | #include "mbed_error.h" |

| hudakz | 7:3a74f7149fa4 | 33 | |

| hudakz | 7:3a74f7149fa4 | 34 | // clock source is selected with CLOCK_SOURCE in json config |

| hudakz | 7:3a74f7149fa4 | 35 | #define USE_PLL_HSE_EXTC 0x8 // Use external clock (ST Link MCO) |

| hudakz | 7:3a74f7149fa4 | 36 | #define USE_PLL_HSE_XTAL 0x4 // Use external xtal (X3 on board - not provided by default) |

| hudakz | 7:3a74f7149fa4 | 37 | #define USE_PLL_HSI 0x2 // Use HSI internal clock |

| hudakz | 7:3a74f7149fa4 | 38 | |

| hudakz | 7:3a74f7149fa4 | 39 | #if ( ((CLOCK_SOURCE) & USE_PLL_HSE_XTAL) || ((CLOCK_SOURCE) & USE_PLL_HSE_EXTC) ) |

| hudakz | 7:3a74f7149fa4 | 40 | uint8_t SetSysClock_PLL_HSE(uint8_t bypass); |

| hudakz | 7:3a74f7149fa4 | 41 | #endif /* ((CLOCK_SOURCE) & USE_PLL_HSE_XTAL) || ((CLOCK_SOURCE) & USE_PLL_HSE_EXTC) */ |

| hudakz | 7:3a74f7149fa4 | 42 | |

| hudakz | 7:3a74f7149fa4 | 43 | #if ((CLOCK_SOURCE) & USE_PLL_HSI) |

| hudakz | 7:3a74f7149fa4 | 44 | uint8_t SetSysClock_PLL_HSI(void); |

| hudakz | 7:3a74f7149fa4 | 45 | #endif /* ((CLOCK_SOURCE) & USE_PLL_HSI) */ |

| hudakz | 7:3a74f7149fa4 | 46 | |

| hudakz | 7:3a74f7149fa4 | 47 | |

| hudakz | 7:3a74f7149fa4 | 48 | /** |

| hudakz | 7:3a74f7149fa4 | 49 | * @brief Configures the System clock source, PLL Multiplier and Divider factors, |

| hudakz | 7:3a74f7149fa4 | 50 | * AHB/APBx prescalers and Flash settings |

| hudakz | 7:3a74f7149fa4 | 51 | * @note This function should be called only once the RCC clock configuration |

| hudakz | 7:3a74f7149fa4 | 52 | * is reset to the default reset state (done in SystemInit() function). |

| hudakz | 7:3a74f7149fa4 | 53 | * @param None |

| hudakz | 7:3a74f7149fa4 | 54 | * @retval None |

| hudakz | 7:3a74f7149fa4 | 55 | */ |

| hudakz | 7:3a74f7149fa4 | 56 | |

| hudakz | 7:3a74f7149fa4 | 57 | MBED_WEAK void SetSysClock(void) |

| hudakz | 7:3a74f7149fa4 | 58 | { |

| hudakz | 7:3a74f7149fa4 | 59 | #if ((CLOCK_SOURCE) & USE_PLL_HSE_EXTC) |

| hudakz | 7:3a74f7149fa4 | 60 | /* 1- Try to start with HSE and external clock */ |

| hudakz | 7:3a74f7149fa4 | 61 | if (SetSysClock_PLL_HSE(1) == 0) |

| hudakz | 7:3a74f7149fa4 | 62 | #endif |

| hudakz | 7:3a74f7149fa4 | 63 | { |

| hudakz | 7:3a74f7149fa4 | 64 | #if ((CLOCK_SOURCE) & USE_PLL_HSE_XTAL) |

| hudakz | 7:3a74f7149fa4 | 65 | /* 2- If fail try to start with HSE and external xtal */ |

| hudakz | 7:3a74f7149fa4 | 66 | if (SetSysClock_PLL_HSE(0) == 0) |

| hudakz | 7:3a74f7149fa4 | 67 | #endif |

| hudakz | 7:3a74f7149fa4 | 68 | { |

| hudakz | 7:3a74f7149fa4 | 69 | #if ((CLOCK_SOURCE) & USE_PLL_HSI) |

| hudakz | 7:3a74f7149fa4 | 70 | /* 3- If fail start with HSI clock */ |

| hudakz | 7:3a74f7149fa4 | 71 | if (SetSysClock_PLL_HSI() == 0) |

| hudakz | 7:3a74f7149fa4 | 72 | #endif |

| hudakz | 7:3a74f7149fa4 | 73 | { |

| hudakz | 7:3a74f7149fa4 | 74 | { |

| hudakz | 7:3a74f7149fa4 | 75 | error("SetSysClock failed\n"); |

| hudakz | 7:3a74f7149fa4 | 76 | } |

| hudakz | 7:3a74f7149fa4 | 77 | } |

| hudakz | 7:3a74f7149fa4 | 78 | } |

| hudakz | 7:3a74f7149fa4 | 79 | } |

| hudakz | 7:3a74f7149fa4 | 80 | |

| hudakz | 7:3a74f7149fa4 | 81 | /* Output clock on MCO2 pin(PC9) for debugging purpose */ |

| hudakz | 7:3a74f7149fa4 | 82 | //HAL_RCC_MCOConfig(RCC_MCO2, RCC_MCO2SOURCE_SYSCLK, RCC_MCODIV_4); |

| hudakz | 7:3a74f7149fa4 | 83 | } |

| hudakz | 7:3a74f7149fa4 | 84 | |

| hudakz | 7:3a74f7149fa4 | 85 | #if ( ((CLOCK_SOURCE) & USE_PLL_HSE_XTAL) || ((CLOCK_SOURCE) & USE_PLL_HSE_EXTC) ) |

| hudakz | 7:3a74f7149fa4 | 86 | /******************************************************************************/ |

| hudakz | 7:3a74f7149fa4 | 87 | /* PLL (clocked by HSE) used as System clock source */ |

| hudakz | 7:3a74f7149fa4 | 88 | /******************************************************************************/ |

| hudakz | 7:3a74f7149fa4 | 89 | MBED_WEAK uint8_t SetSysClock_PLL_HSE(uint8_t bypass) |

| hudakz | 7:3a74f7149fa4 | 90 | { |

| hudakz | 7:3a74f7149fa4 | 91 | RCC_OscInitTypeDef RCC_OscInitStruct; |

| hudakz | 7:3a74f7149fa4 | 92 | RCC_ClkInitTypeDef RCC_ClkInitStruct; |

| hudakz | 7:3a74f7149fa4 | 93 | |

| hudakz | 7:3a74f7149fa4 | 94 | /* The voltage scaling allows optimizing the power consumption when the device is |

| hudakz | 7:3a74f7149fa4 | 95 | clocked below the maximum system frequency, to update the voltage scaling value |

| hudakz | 7:3a74f7149fa4 | 96 | regarding system frequency refer to product datasheet. */ |

| hudakz | 7:3a74f7149fa4 | 97 | __HAL_RCC_PWR_CLK_ENABLE(); |

| hudakz | 7:3a74f7149fa4 | 98 | __HAL_PWR_VOLTAGESCALING_CONFIG(PWR_REGULATOR_VOLTAGE_SCALE2); |

| hudakz | 7:3a74f7149fa4 | 99 | |

| hudakz | 7:3a74f7149fa4 | 100 | /* Get the Clocks configuration according to the internal RCC registers */ |

| hudakz | 7:3a74f7149fa4 | 101 | HAL_RCC_GetOscConfig(&RCC_OscInitStruct); |

| hudakz | 7:3a74f7149fa4 | 102 | |

| hudakz | 7:3a74f7149fa4 | 103 | /* PLL could be already configured by bootlader */ |

| hudakz | 7:3a74f7149fa4 | 104 | if (RCC_OscInitStruct.PLL.PLLState != RCC_PLL_ON) { |

| hudakz | 7:3a74f7149fa4 | 105 | |

| hudakz | 7:3a74f7149fa4 | 106 | // Enable HSE oscillator and activate PLL with HSE as source |

| hudakz | 7:3a74f7149fa4 | 107 | RCC_OscInitStruct.OscillatorType = RCC_OSCILLATORTYPE_HSE; |

| hudakz | 7:3a74f7149fa4 | 108 | if (bypass == 0) { |

| hudakz | 7:3a74f7149fa4 | 109 | RCC_OscInitStruct.HSEState = RCC_HSE_ON; // External 25 MHz xtal on OSC_IN/OSC_OUT |

| hudakz | 7:3a74f7149fa4 | 110 | } else { |

| hudakz | 7:3a74f7149fa4 | 111 | RCC_OscInitStruct.HSEState = RCC_HSE_BYPASS; // External 25 MHz clock on OSC_IN |

| hudakz | 7:3a74f7149fa4 | 112 | } |

| hudakz | 7:3a74f7149fa4 | 113 | |

| hudakz | 7:3a74f7149fa4 | 114 | RCC_OscInitStruct.PLL.PLLState = RCC_PLL_ON; |

| hudakz | 7:3a74f7149fa4 | 115 | RCC_OscInitStruct.PLL.PLLSource = RCC_PLLSOURCE_HSE; |

| hudakz | 7:3a74f7149fa4 | 116 | #if (CLOCK_SOURCE_USB) |

| hudakz | 7:3a74f7149fa4 | 117 | RCC_OscInitStruct.PLL.PLLM = 25; // VCO input clock = 1 MHz (25 MHz / 25) |

| hudakz | 7:3a74f7149fa4 | 118 | RCC_OscInitStruct.PLL.PLLN = 192; // VCO output clock = 192 MHz (1 MHz * 192) |

| hudakz | 7:3a74f7149fa4 | 119 | RCC_OscInitStruct.PLL.PLLP = RCC_PLLP_DIV2;// PLLCLK = 96 MHz (192 / 2) |

| hudakz | 7:3a74f7149fa4 | 120 | RCC_OscInitStruct.PLL.PLLQ = 4; // USB clock = 48 MHz (192 / 4, CLOCK_SOURCE_USB = 1) |

| hudakz | 7:3a74f7149fa4 | 121 | #else |

| hudakz | 7:3a74f7149fa4 | 122 | RCC_OscInitStruct.PLL.PLLM = 12; // VCO input clock = 2.0833 MHz (25 MHz / 12) |

| hudakz | 7:3a74f7149fa4 | 123 | RCC_OscInitStruct.PLL.PLLN = 96; // VCO output clock = 200 MHz (2.0833 MHz * 96) |

| hudakz | 7:3a74f7149fa4 | 124 | RCC_OscInitStruct.PLL.PLLP = RCC_PLLP_DIV2;// PLLCLK = 100 MHz (200 / 2) |

| hudakz | 7:3a74f7149fa4 | 125 | RCC_OscInitStruct.PLL.PLLQ = 4; // USB clock = 50 MHz (200 / 4 -> USB not available) |

| hudakz | 7:3a74f7149fa4 | 126 | #endif |

| hudakz | 7:3a74f7149fa4 | 127 | if (HAL_RCC_OscConfig(&RCC_OscInitStruct) != HAL_OK) { |

| hudakz | 7:3a74f7149fa4 | 128 | return 0; // FAIL |

| hudakz | 7:3a74f7149fa4 | 129 | } |

| hudakz | 7:3a74f7149fa4 | 130 | } |

| hudakz | 7:3a74f7149fa4 | 131 | |

| hudakz | 7:3a74f7149fa4 | 132 | // Select PLL as system clock source and configure the HCLK, PCLK1 and PCLK2 clocks dividers |

| hudakz | 7:3a74f7149fa4 | 133 | RCC_ClkInitStruct.ClockType = RCC_CLOCKTYPE_SYSCLK | RCC_CLOCKTYPE_HCLK | RCC_CLOCKTYPE_PCLK1 | RCC_CLOCKTYPE_PCLK2; |

| hudakz | 7:3a74f7149fa4 | 134 | RCC_ClkInitStruct.SYSCLKSource = RCC_SYSCLKSOURCE_PLLCLK; // 100/96 MHz |

| hudakz | 7:3a74f7149fa4 | 135 | RCC_ClkInitStruct.AHBCLKDivider = RCC_SYSCLK_DIV1; // 100/96 MHz |

| hudakz | 7:3a74f7149fa4 | 136 | RCC_ClkInitStruct.APB1CLKDivider = RCC_HCLK_DIV2; // 50/48 MHz |

| hudakz | 7:3a74f7149fa4 | 137 | RCC_ClkInitStruct.APB2CLKDivider = RCC_HCLK_DIV1; // 100/96 MHz |

| hudakz | 7:3a74f7149fa4 | 138 | if (HAL_RCC_ClockConfig(&RCC_ClkInitStruct, FLASH_LATENCY_3) != HAL_OK) { |

| hudakz | 7:3a74f7149fa4 | 139 | return 0; // FAIL |

| hudakz | 7:3a74f7149fa4 | 140 | } |

| hudakz | 7:3a74f7149fa4 | 141 | |

| hudakz | 7:3a74f7149fa4 | 142 | /* Output clock on MCO1 pin(PA8) for debugging purpose */ |

| hudakz | 7:3a74f7149fa4 | 143 | //if (bypass == 0) |

| hudakz | 7:3a74f7149fa4 | 144 | // HAL_RCC_MCOConfig(RCC_MCO1, RCC_MCO1SOURCE_HSE, RCC_MCODIV_2); // 4 MHz with xtal |

| hudakz | 7:3a74f7149fa4 | 145 | //else |

| hudakz | 7:3a74f7149fa4 | 146 | // HAL_RCC_MCOConfig(RCC_MCO1, RCC_MCO1SOURCE_HSE, RCC_MCODIV_1); // 8 MHz with external clock |

| hudakz | 7:3a74f7149fa4 | 147 | |

| hudakz | 7:3a74f7149fa4 | 148 | return 1; // OK |

| hudakz | 7:3a74f7149fa4 | 149 | } |

| hudakz | 7:3a74f7149fa4 | 150 | #endif /* ((CLOCK_SOURCE) & USE_PLL_HSE_XTAL) || ((CLOCK_SOURCE) & USE_PLL_HSE_EXTC) */ |

| hudakz | 7:3a74f7149fa4 | 151 | |

| hudakz | 7:3a74f7149fa4 | 152 | #if ((CLOCK_SOURCE) & USE_PLL_HSI) |

| hudakz | 7:3a74f7149fa4 | 153 | /******************************************************************************/ |

| hudakz | 7:3a74f7149fa4 | 154 | /* PLL (clocked by HSI) used as System clock source */ |

| hudakz | 7:3a74f7149fa4 | 155 | /******************************************************************************/ |

| hudakz | 7:3a74f7149fa4 | 156 | uint8_t SetSysClock_PLL_HSI(void) |

| hudakz | 7:3a74f7149fa4 | 157 | { |

| hudakz | 7:3a74f7149fa4 | 158 | RCC_OscInitTypeDef RCC_OscInitStruct; |

| hudakz | 7:3a74f7149fa4 | 159 | RCC_ClkInitTypeDef RCC_ClkInitStruct; |

| hudakz | 7:3a74f7149fa4 | 160 | |

| hudakz | 7:3a74f7149fa4 | 161 | /* The voltage scaling allows optimizing the power consumption when the device is |

| hudakz | 7:3a74f7149fa4 | 162 | clocked below the maximum system frequency, to update the voltage scaling value |

| hudakz | 7:3a74f7149fa4 | 163 | regarding system frequency refer to product datasheet. */ |

| hudakz | 7:3a74f7149fa4 | 164 | __HAL_RCC_PWR_CLK_ENABLE(); |

| hudakz | 7:3a74f7149fa4 | 165 | __HAL_PWR_VOLTAGESCALING_CONFIG(PWR_REGULATOR_VOLTAGE_SCALE2); |

| hudakz | 7:3a74f7149fa4 | 166 | |

| hudakz | 7:3a74f7149fa4 | 167 | // Enable HSI oscillator and activate PLL with HSI as source |

| hudakz | 7:3a74f7149fa4 | 168 | RCC_OscInitStruct.OscillatorType = RCC_OSCILLATORTYPE_HSI | RCC_OSCILLATORTYPE_HSE; |

| hudakz | 7:3a74f7149fa4 | 169 | RCC_OscInitStruct.HSIState = RCC_HSI_ON; |

| hudakz | 7:3a74f7149fa4 | 170 | RCC_OscInitStruct.HSEState = RCC_HSE_OFF; |

| hudakz | 7:3a74f7149fa4 | 171 | RCC_OscInitStruct.HSICalibrationValue = RCC_HSICALIBRATION_DEFAULT; |

| hudakz | 7:3a74f7149fa4 | 172 | RCC_OscInitStruct.PLL.PLLState = RCC_PLL_ON; |

| hudakz | 7:3a74f7149fa4 | 173 | RCC_OscInitStruct.PLL.PLLSource = RCC_PLLSOURCE_HSI; |

| hudakz | 7:3a74f7149fa4 | 174 | RCC_OscInitStruct.PLL.PLLM = 8; // VCO input clock = 2 MHz (16 MHz / 8) |

| hudakz | 7:3a74f7149fa4 | 175 | #if (DEVICE_USBDEVICE) |

| hudakz | 7:3a74f7149fa4 | 176 | RCC_OscInitStruct.PLL.PLLN = 192; // VCO output clock = 384 MHz (2 MHz * 192) |

| hudakz | 7:3a74f7149fa4 | 177 | #else /* DEVICE_USBDEVICE */ |

| hudakz | 7:3a74f7149fa4 | 178 | RCC_OscInitStruct.PLL.PLLN = 200; // VCO output clock = 400 MHz (2 MHz * 200) |

| hudakz | 7:3a74f7149fa4 | 179 | #endif /* DEVICE_USBDEVICE */ |

| hudakz | 7:3a74f7149fa4 | 180 | RCC_OscInitStruct.PLL.PLLP = RCC_PLLP_DIV4; // PLLCLK = 100 MHz or 96 MHz (depending on DEVICE_USBDEVICE) |

| hudakz | 7:3a74f7149fa4 | 181 | RCC_OscInitStruct.PLL.PLLQ = 8; // USB clock = 48 MHz (DEVICE_USBDEVICE=1) |

| hudakz | 7:3a74f7149fa4 | 182 | if (HAL_RCC_OscConfig(&RCC_OscInitStruct) != HAL_OK) { |

| hudakz | 7:3a74f7149fa4 | 183 | return 0; // FAIL |

| hudakz | 7:3a74f7149fa4 | 184 | } |

| hudakz | 7:3a74f7149fa4 | 185 | |

| hudakz | 7:3a74f7149fa4 | 186 | /* Select PLL as system clock source and configure the HCLK, PCLK1 and PCLK2 clocks dividers */ |

| hudakz | 7:3a74f7149fa4 | 187 | RCC_ClkInitStruct.ClockType = (RCC_CLOCKTYPE_SYSCLK | RCC_CLOCKTYPE_HCLK | RCC_CLOCKTYPE_PCLK1 | RCC_CLOCKTYPE_PCLK2); |

| hudakz | 7:3a74f7149fa4 | 188 | RCC_ClkInitStruct.SYSCLKSource = RCC_SYSCLKSOURCE_PLLCLK; |

| hudakz | 7:3a74f7149fa4 | 189 | RCC_ClkInitStruct.AHBCLKDivider = RCC_SYSCLK_DIV1; |

| hudakz | 7:3a74f7149fa4 | 190 | RCC_ClkInitStruct.APB1CLKDivider = RCC_HCLK_DIV2; |

| hudakz | 7:3a74f7149fa4 | 191 | RCC_ClkInitStruct.APB2CLKDivider = RCC_HCLK_DIV1; |

| hudakz | 7:3a74f7149fa4 | 192 | if (HAL_RCC_ClockConfig(&RCC_ClkInitStruct, FLASH_LATENCY_3) != HAL_OK) { |

| hudakz | 7:3a74f7149fa4 | 193 | return 0; // FAIL |

| hudakz | 7:3a74f7149fa4 | 194 | } |

| hudakz | 7:3a74f7149fa4 | 195 | |

| hudakz | 7:3a74f7149fa4 | 196 | /* Output clock on MCO1 pin(PA8) for debugging purpose */ |

| hudakz | 7:3a74f7149fa4 | 197 | //HAL_RCC_MCOConfig(RCC_MCO1, RCC_MCO1SOURCE_HSI, RCC_MCODIV_1); // 16 MHz |

| hudakz | 7:3a74f7149fa4 | 198 | |

| hudakz | 7:3a74f7149fa4 | 199 | return 1; // OK |

| hudakz | 7:3a74f7149fa4 | 200 | } |

| hudakz | 7:3a74f7149fa4 | 201 | #endif /* ((CLOCK_SOURCE) & USE_PLL_HSI) */ |