driver for SX1232 transceiver

summary

The SX1232 is a fully integrated ISM band transceiver optimized for use in the (EN 300 220-1) 868 MHz band in Europe and the (FCC Part 15) 915 MHz band in the US with a minimum of external components. It offers a combination of high link budget and low current consumption in all operating modes.

features

This part offers similar functionality to XBee PRO 900 modules, except RF performance would be improved, especially at slower data-rates. This is due to available narrower receiver bandwidths, and higher TX power, among other things. Additionally, its probably redundant to have a microcontroller on your wireless module, since the mbed cpu can drive radio directly.

This version of driver library supports packet size up to FIFO size (64bytes) to keep it simple and small. For larger packet sizes, a different driver could support the FIFO flow control pins.

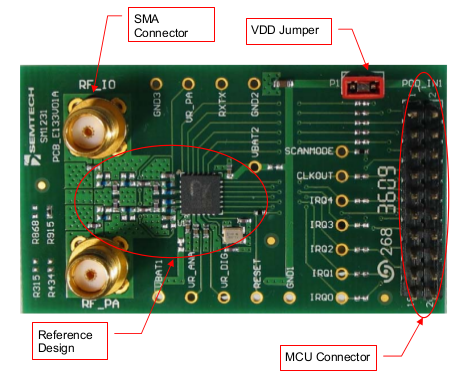

wiring connections

Minimum required connections are SPI: mosi, miso, sclk, cs, one interrupt pin, and optional hardware reset pin.

example code

For example usage see Demo Chat Application.

specification of chip

Information on device.

sx1232.h@1:67a841d57890, 2013-05-01 (annotated)

- Committer:

- dudmuck

- Date:

- Wed May 01 23:42:35 2013 +0000

- Revision:

- 1:67a841d57890

- Parent:

- 0:06cc2cd9f340

- Child:

- 2:8717baf6e00a

apache license

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| dudmuck | 1:67a841d57890 | 1 | /* SX1232 driver |

| dudmuck | 1:67a841d57890 | 2 | * Copyright (c) 2013 Semtech |

| dudmuck | 1:67a841d57890 | 3 | * |

| dudmuck | 1:67a841d57890 | 4 | * Licensed under the Apache License, Version 2.0 (the "License"); |

| dudmuck | 1:67a841d57890 | 5 | * you may not use this file except in compliance with the License. |

| dudmuck | 1:67a841d57890 | 6 | * You may obtain a copy of the License at |

| dudmuck | 1:67a841d57890 | 7 | * |

| dudmuck | 1:67a841d57890 | 8 | * http://www.apache.org/licenses/LICENSE-2.0 |

| dudmuck | 1:67a841d57890 | 9 | * |

| dudmuck | 1:67a841d57890 | 10 | * Unless required by applicable law or agreed to in writing, software |

| dudmuck | 1:67a841d57890 | 11 | * distributed under the License is distributed on an "AS IS" BASIS, |

| dudmuck | 1:67a841d57890 | 12 | * WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied. |

| dudmuck | 1:67a841d57890 | 13 | * See the License for the specific language governing permissions and |

| dudmuck | 1:67a841d57890 | 14 | * limitations under the License. |

| dudmuck | 1:67a841d57890 | 15 | */ |

| dudmuck | 1:67a841d57890 | 16 | |

| dudmuck | 0:06cc2cd9f340 | 17 | #ifndef SX1232_H |

| dudmuck | 0:06cc2cd9f340 | 18 | #define SX1232_H |

| dudmuck | 0:06cc2cd9f340 | 19 | |

| dudmuck | 0:06cc2cd9f340 | 20 | #include "mbed.h" |

| dudmuck | 0:06cc2cd9f340 | 21 | |

| dudmuck | 0:06cc2cd9f340 | 22 | #define XTAL_FREQ 32000000 |

| dudmuck | 0:06cc2cd9f340 | 23 | |

| dudmuck | 0:06cc2cd9f340 | 24 | #define FREQ_STEP_MHZ 61.03515625e-6 |

| dudmuck | 0:06cc2cd9f340 | 25 | #define FREQ_STEP_KHZ 61.03515625e-3 |

| dudmuck | 0:06cc2cd9f340 | 26 | #define FREQ_STEP_HZ 61.03515625 |

| dudmuck | 0:06cc2cd9f340 | 27 | |

| dudmuck | 0:06cc2cd9f340 | 28 | /******************************************************************************/ |

| dudmuck | 0:06cc2cd9f340 | 29 | /*! |

| dudmuck | 0:06cc2cd9f340 | 30 | * SX1232 Internal registers Address |

| dudmuck | 0:06cc2cd9f340 | 31 | */ |

| dudmuck | 0:06cc2cd9f340 | 32 | #define REG_FIFO 0x00 |

| dudmuck | 0:06cc2cd9f340 | 33 | // Common settings |

| dudmuck | 0:06cc2cd9f340 | 34 | #define REG_OPMODE 0x01 |

| dudmuck | 0:06cc2cd9f340 | 35 | #define REG_BITRATEMSB 0x02 |

| dudmuck | 0:06cc2cd9f340 | 36 | #define REG_BITRATELSB 0x03 |

| dudmuck | 0:06cc2cd9f340 | 37 | #define REG_FDEVMSB 0x04 |

| dudmuck | 0:06cc2cd9f340 | 38 | #define REG_FDEVLSB 0x05 |

| dudmuck | 0:06cc2cd9f340 | 39 | #define REG_FRFMSB 0x06 |

| dudmuck | 0:06cc2cd9f340 | 40 | #define REG_FRFMID 0x07 |

| dudmuck | 0:06cc2cd9f340 | 41 | #define REG_FRFLSB 0x08 |

| dudmuck | 0:06cc2cd9f340 | 42 | // Tx settings |

| dudmuck | 0:06cc2cd9f340 | 43 | #define REG_PACONFIG 0x09 |

| dudmuck | 0:06cc2cd9f340 | 44 | #define REG_PARAMP 0x0A |

| dudmuck | 0:06cc2cd9f340 | 45 | #define REG_OCP 0x0B |

| dudmuck | 0:06cc2cd9f340 | 46 | // Rx settings |

| dudmuck | 0:06cc2cd9f340 | 47 | #define REG_LNA 0x0C |

| dudmuck | 0:06cc2cd9f340 | 48 | #define REG_RXCONFIG 0x0D |

| dudmuck | 0:06cc2cd9f340 | 49 | #define REG_RSSICONFIG 0x0E |

| dudmuck | 0:06cc2cd9f340 | 50 | #define REG_RSSICOLLISION 0x0F |

| dudmuck | 0:06cc2cd9f340 | 51 | #define REG_RSSITHRESH 0x10 |

| dudmuck | 0:06cc2cd9f340 | 52 | #define REG_RSSIVALUE 0x11 |

| dudmuck | 0:06cc2cd9f340 | 53 | #define REG_RXBW 0x12 |

| dudmuck | 0:06cc2cd9f340 | 54 | #define REG_AFCBW 0x13 |

| dudmuck | 0:06cc2cd9f340 | 55 | #define REG_OOKPEAK 0x14 |

| dudmuck | 0:06cc2cd9f340 | 56 | #define REG_OOKFIX 0x15 |

| dudmuck | 0:06cc2cd9f340 | 57 | #define REG_OOKAVG 0x16 |

| dudmuck | 0:06cc2cd9f340 | 58 | #define REG_RES17 0x17 |

| dudmuck | 0:06cc2cd9f340 | 59 | #define REG_RES18 0x18 |

| dudmuck | 0:06cc2cd9f340 | 60 | #define REG_RES19 0x19 |

| dudmuck | 0:06cc2cd9f340 | 61 | #define REG_AFCFEI 0x1A |

| dudmuck | 0:06cc2cd9f340 | 62 | #define REG_AFCMSB 0x1B |

| dudmuck | 0:06cc2cd9f340 | 63 | #define REG_AFCLSB 0x1C |

| dudmuck | 0:06cc2cd9f340 | 64 | #define REG_FEIMSB 0x1D |

| dudmuck | 0:06cc2cd9f340 | 65 | #define REG_FEILSB 0x1E |

| dudmuck | 0:06cc2cd9f340 | 66 | #define REG_PREAMBLEDETECT 0x1F |

| dudmuck | 0:06cc2cd9f340 | 67 | #define REG_RXTIMEOUT1 0x20 |

| dudmuck | 0:06cc2cd9f340 | 68 | #define REG_RXTIMEOUT2 0x21 |

| dudmuck | 0:06cc2cd9f340 | 69 | #define REG_RXTIMEOUT3 0x22 |

| dudmuck | 0:06cc2cd9f340 | 70 | #define REG_RXDELAY 0x23 |

| dudmuck | 0:06cc2cd9f340 | 71 | // Oscillator settings |

| dudmuck | 0:06cc2cd9f340 | 72 | #define REG_OSC 0x24 |

| dudmuck | 0:06cc2cd9f340 | 73 | // Packet handler settings |

| dudmuck | 0:06cc2cd9f340 | 74 | #define REG_PREAMBLEMSB 0x25 |

| dudmuck | 0:06cc2cd9f340 | 75 | #define REG_PREAMBLELSB 0x26 |

| dudmuck | 0:06cc2cd9f340 | 76 | #define REG_SYNCCONFIG 0x27 |

| dudmuck | 0:06cc2cd9f340 | 77 | #define REG_SYNCVALUE1 0x28 |

| dudmuck | 0:06cc2cd9f340 | 78 | #define REG_SYNCVALUE2 0x29 |

| dudmuck | 0:06cc2cd9f340 | 79 | #define REG_SYNCVALUE3 0x2A |

| dudmuck | 0:06cc2cd9f340 | 80 | #define REG_SYNCVALUE4 0x2B |

| dudmuck | 0:06cc2cd9f340 | 81 | #define REG_SYNCVALUE5 0x2C |

| dudmuck | 0:06cc2cd9f340 | 82 | #define REG_SYNCVALUE6 0x2D |

| dudmuck | 0:06cc2cd9f340 | 83 | #define REG_SYNCVALUE7 0x2E |

| dudmuck | 0:06cc2cd9f340 | 84 | #define REG_SYNCVALUE8 0x2F |

| dudmuck | 0:06cc2cd9f340 | 85 | #define REG_PACKETCONFIG1 0x30 |

| dudmuck | 0:06cc2cd9f340 | 86 | #define REG_PACKETCONFIG2 0x31 |

| dudmuck | 0:06cc2cd9f340 | 87 | #define REG_PAYLOADLENGTH 0x32 |

| dudmuck | 0:06cc2cd9f340 | 88 | #define REG_NODEADRS 0x33 |

| dudmuck | 0:06cc2cd9f340 | 89 | #define REG_BROADCASTADRS 0x34 |

| dudmuck | 0:06cc2cd9f340 | 90 | #define REG_FIFOTHRESH 0x35 |

| dudmuck | 0:06cc2cd9f340 | 91 | // SM settings |

| dudmuck | 0:06cc2cd9f340 | 92 | #define REG_SEQCONFIG1 0x36 |

| dudmuck | 0:06cc2cd9f340 | 93 | #define REG_SEQCONFIG2 0x37 |

| dudmuck | 0:06cc2cd9f340 | 94 | #define REG_TIMERRESOL 0x38 |

| dudmuck | 0:06cc2cd9f340 | 95 | #define REG_TIMER1COEF 0x39 |

| dudmuck | 0:06cc2cd9f340 | 96 | #define REG_TIMER2COEF 0x3A |

| dudmuck | 0:06cc2cd9f340 | 97 | // Service settings |

| dudmuck | 0:06cc2cd9f340 | 98 | #define REG_IMAGECAL 0x3B |

| dudmuck | 0:06cc2cd9f340 | 99 | #define REG_TEMP 0x3C |

| dudmuck | 0:06cc2cd9f340 | 100 | #define REG_LOWBAT 0x3D |

| dudmuck | 0:06cc2cd9f340 | 101 | // Status |

| dudmuck | 0:06cc2cd9f340 | 102 | #define REG_IRQFLAGS1 0x3E |

| dudmuck | 0:06cc2cd9f340 | 103 | #define REG_IRQFLAGS2 0x3F |

| dudmuck | 0:06cc2cd9f340 | 104 | // I/O settings |

| dudmuck | 0:06cc2cd9f340 | 105 | #define REG_DIOMAPPING1 0x40 |

| dudmuck | 0:06cc2cd9f340 | 106 | #define REG_DIOMAPPING2 0x41 |

| dudmuck | 0:06cc2cd9f340 | 107 | // Version |

| dudmuck | 0:06cc2cd9f340 | 108 | #define REG_VERSION 0x42 |

| dudmuck | 0:06cc2cd9f340 | 109 | // Additional settings |

| dudmuck | 0:06cc2cd9f340 | 110 | #define REG_AGCREF 0x43 |

| dudmuck | 0:06cc2cd9f340 | 111 | #define REG_AGCTHRESH1 0x44 |

| dudmuck | 0:06cc2cd9f340 | 112 | #define REG_AGCTHRESH2 0x45 |

| dudmuck | 0:06cc2cd9f340 | 113 | #define REG_AGCTHRESH3 0x46 |

| dudmuck | 0:06cc2cd9f340 | 114 | #define REG_PLLHOP 0x4B |

| dudmuck | 0:06cc2cd9f340 | 115 | #define REG_TCXO 0x58 |

| dudmuck | 0:06cc2cd9f340 | 116 | #define REG_PADAC 0x5A |

| dudmuck | 0:06cc2cd9f340 | 117 | #define REG_PLL 0x5C |

| dudmuck | 0:06cc2cd9f340 | 118 | #define REG_PLLLOWPN 0x5E |

| dudmuck | 0:06cc2cd9f340 | 119 | #define REG_FORMERTEMP 0x6C |

| dudmuck | 0:06cc2cd9f340 | 120 | #define REG_BITRATEFRAC 0x70 |

| dudmuck | 0:06cc2cd9f340 | 121 | |

| dudmuck | 0:06cc2cd9f340 | 122 | /******************************************************************************/ |

| dudmuck | 0:06cc2cd9f340 | 123 | |

| dudmuck | 0:06cc2cd9f340 | 124 | typedef enum { |

| dudmuck | 0:06cc2cd9f340 | 125 | RF_OPMODE_SLEEP = 0, |

| dudmuck | 0:06cc2cd9f340 | 126 | RF_OPMODE_STANDBY, |

| dudmuck | 0:06cc2cd9f340 | 127 | RF_OPMODE_SYNTHESIZER_TX, |

| dudmuck | 0:06cc2cd9f340 | 128 | RF_OPMODE_TRANSMITTER, |

| dudmuck | 0:06cc2cd9f340 | 129 | RF_OPMODE_SYNTHESIZER_RX, |

| dudmuck | 0:06cc2cd9f340 | 130 | RF_OPMODE_RECEIVER |

| dudmuck | 0:06cc2cd9f340 | 131 | } chip_mode_e; |

| dudmuck | 0:06cc2cd9f340 | 132 | |

| dudmuck | 0:06cc2cd9f340 | 133 | /******************************************************************************/ |

| dudmuck | 0:06cc2cd9f340 | 134 | |

| dudmuck | 0:06cc2cd9f340 | 135 | typedef union { |

| dudmuck | 0:06cc2cd9f340 | 136 | struct { // sx1232 register 0x01 |

| dudmuck | 0:06cc2cd9f340 | 137 | uint8_t Mode : 3; // 0,1,2 |

| dudmuck | 0:06cc2cd9f340 | 138 | uint8_t ModulationShaping : 2; // 3,4 FSK/OOK |

| dudmuck | 0:06cc2cd9f340 | 139 | uint8_t ModulationType : 2; // 5,6 FSK/OOK |

| dudmuck | 0:06cc2cd9f340 | 140 | uint8_t LongRangeMode : 1; // 7 change this bit only in sleep mode |

| dudmuck | 0:06cc2cd9f340 | 141 | } bits; |

| dudmuck | 0:06cc2cd9f340 | 142 | uint8_t octet; |

| dudmuck | 0:06cc2cd9f340 | 143 | } RegOpMode_t; |

| dudmuck | 0:06cc2cd9f340 | 144 | |

| dudmuck | 0:06cc2cd9f340 | 145 | typedef union { |

| dudmuck | 0:06cc2cd9f340 | 146 | struct { // sx1232 register 0x09 |

| dudmuck | 0:06cc2cd9f340 | 147 | uint8_t OutputPower : 4; // 0,1,2,3 |

| dudmuck | 0:06cc2cd9f340 | 148 | uint8_t unused : 3; // 4,5,6 |

| dudmuck | 0:06cc2cd9f340 | 149 | uint8_t PaSelect : 1; // 7 1=PA_BOOST |

| dudmuck | 0:06cc2cd9f340 | 150 | } bits; |

| dudmuck | 0:06cc2cd9f340 | 151 | uint8_t octet; |

| dudmuck | 0:06cc2cd9f340 | 152 | } RegPaConfig_t; |

| dudmuck | 0:06cc2cd9f340 | 153 | |

| dudmuck | 0:06cc2cd9f340 | 154 | typedef union { |

| dudmuck | 0:06cc2cd9f340 | 155 | struct { // sx1232 register 0x0c |

| dudmuck | 0:06cc2cd9f340 | 156 | uint8_t lna_i_boost : 2; // 0,1 |

| dudmuck | 0:06cc2cd9f340 | 157 | uint8_t unused : 1; // 2 |

| dudmuck | 0:06cc2cd9f340 | 158 | uint8_t trim_rx_crfo : 2; // 3,4 add caps to RFo |

| dudmuck | 0:06cc2cd9f340 | 159 | uint8_t rxfe_gain : 3; // 5,6,7 1=PA_BOOST |

| dudmuck | 0:06cc2cd9f340 | 160 | } bits; |

| dudmuck | 0:06cc2cd9f340 | 161 | uint8_t octet; |

| dudmuck | 0:06cc2cd9f340 | 162 | } RegLna_t; // RXFE |

| dudmuck | 0:06cc2cd9f340 | 163 | |

| dudmuck | 0:06cc2cd9f340 | 164 | typedef union { |

| dudmuck | 0:06cc2cd9f340 | 165 | struct { // sx1232 register 0x0d |

| dudmuck | 0:06cc2cd9f340 | 166 | uint8_t RxTrigger : 3; // 0,1,2: 0=none 1=rssiInt 6=preambleDet 7=both |

| dudmuck | 0:06cc2cd9f340 | 167 | uint8_t AgcAutoOn : 1; // 3 |

| dudmuck | 0:06cc2cd9f340 | 168 | uint8_t AfcAutoOn : 1; // 4 |

| dudmuck | 0:06cc2cd9f340 | 169 | uint8_t RestartRxWithPllLock : 1; // 5 manual rx restart, for use with FHSS |

| dudmuck | 0:06cc2cd9f340 | 170 | uint8_t RestartRxWithoutPllLock : 1; // 6 manual rx restart |

| dudmuck | 0:06cc2cd9f340 | 171 | uint8_t RestartRxOnCollision : 1; // 7 collision detector (see RegRssiCollision at 0x0f) |

| dudmuck | 0:06cc2cd9f340 | 172 | } bits; |

| dudmuck | 0:06cc2cd9f340 | 173 | uint8_t octet; |

| dudmuck | 0:06cc2cd9f340 | 174 | } RegRxConfig_t; |

| dudmuck | 0:06cc2cd9f340 | 175 | |

| dudmuck | 0:06cc2cd9f340 | 176 | typedef union { |

| dudmuck | 0:06cc2cd9f340 | 177 | struct { // sx1232 register 0x14 |

| dudmuck | 0:06cc2cd9f340 | 178 | uint8_t OokPeakThreshStep : 3; // 0,1,2 |

| dudmuck | 0:06cc2cd9f340 | 179 | uint8_t OokThreshType : 2; // 3,4 |

| dudmuck | 0:06cc2cd9f340 | 180 | uint8_t BitSyncOn : 1; // 5 |

| dudmuck | 0:06cc2cd9f340 | 181 | uint8_t barker_en : 1; // 6 |

| dudmuck | 0:06cc2cd9f340 | 182 | uint8_t bsync_opt : 1; // 7 not used |

| dudmuck | 0:06cc2cd9f340 | 183 | } bits; |

| dudmuck | 0:06cc2cd9f340 | 184 | uint8_t octet; |

| dudmuck | 0:06cc2cd9f340 | 185 | } RegOokPeak_t; // DEMOD1 0x14 |

| dudmuck | 0:06cc2cd9f340 | 186 | |

| dudmuck | 0:06cc2cd9f340 | 187 | typedef union { |

| dudmuck | 0:06cc2cd9f340 | 188 | struct { // sx1232 register 0x1a |

| dudmuck | 0:06cc2cd9f340 | 189 | uint8_t AfcAutoClearOn : 1; // 0 |

| dudmuck | 0:06cc2cd9f340 | 190 | uint8_t AfcClear : 1; // 1 manual clear |

| dudmuck | 0:06cc2cd9f340 | 191 | uint8_t unused1 : 1; // 2 |

| dudmuck | 0:06cc2cd9f340 | 192 | uint8_t fei_range : 1; // 3 FEI range limited by: 0=rxbw 1=fs/2 |

| dudmuck | 0:06cc2cd9f340 | 193 | uint8_t AgcStart : 1; // 4 manual trigger AGC |

| dudmuck | 0:06cc2cd9f340 | 194 | uint8_t unused : 3; // 5,6,7 |

| dudmuck | 0:06cc2cd9f340 | 195 | } bits; |

| dudmuck | 0:06cc2cd9f340 | 196 | uint8_t octet; |

| dudmuck | 0:06cc2cd9f340 | 197 | } RegAfcFei_t; |

| dudmuck | 0:06cc2cd9f340 | 198 | |

| dudmuck | 0:06cc2cd9f340 | 199 | typedef union { |

| dudmuck | 0:06cc2cd9f340 | 200 | struct { // sx1232 register 0x1f |

| dudmuck | 0:06cc2cd9f340 | 201 | uint8_t PreambleDetectorTol : 5; // 0,1,2,3,4 allowed chip errors |

| dudmuck | 0:06cc2cd9f340 | 202 | uint8_t PreambleDetectorSize : 2; // 5,6 00b=1bytes... 11b=4bytes |

| dudmuck | 0:06cc2cd9f340 | 203 | uint8_t PreambleDetectorOn : 1; // 7 |

| dudmuck | 0:06cc2cd9f340 | 204 | } bits; |

| dudmuck | 0:06cc2cd9f340 | 205 | uint8_t octet; |

| dudmuck | 0:06cc2cd9f340 | 206 | } RegPreambleDetect_t; |

| dudmuck | 0:06cc2cd9f340 | 207 | |

| dudmuck | 0:06cc2cd9f340 | 208 | typedef union { |

| dudmuck | 0:06cc2cd9f340 | 209 | struct { // sx1232 register 0x27 |

| dudmuck | 0:06cc2cd9f340 | 210 | uint8_t SyncSize : 3; // 0,1,2 |

| dudmuck | 0:06cc2cd9f340 | 211 | uint8_t FifoFillCondition : 1; // 3 rx fifo fill starting 0=start-on-sync |

| dudmuck | 0:06cc2cd9f340 | 212 | uint8_t SyncOn : 1; // 4 enable pattern recognition |

| dudmuck | 0:06cc2cd9f340 | 213 | uint8_t PreamblePolarity : 1; // 5 0=0xaa 1=0x55 |

| dudmuck | 0:06cc2cd9f340 | 214 | uint8_t AutoRestartRxMode : 2; // 6,7 00b=manual restart, 01b=auto-restart after fifo pulled, and 10b=add wait-for-pll |

| dudmuck | 0:06cc2cd9f340 | 215 | } bits; // manual Rx restart is in RegRxConfig |

| dudmuck | 0:06cc2cd9f340 | 216 | uint8_t octet; |

| dudmuck | 0:06cc2cd9f340 | 217 | } RegSyncConfig_t; |

| dudmuck | 0:06cc2cd9f340 | 218 | |

| dudmuck | 0:06cc2cd9f340 | 219 | typedef union { |

| dudmuck | 0:06cc2cd9f340 | 220 | struct { // sx1232 register 0x30 |

| dudmuck | 0:06cc2cd9f340 | 221 | uint8_t CrCWhiteningType : 1; // 0 1=IBM-crc 0=ccitt-crc |

| dudmuck | 0:06cc2cd9f340 | 222 | uint8_t AddressFiltering : 2; // 1,2 11b = two-byte nodeadrs at 0x2c->0x2f |

| dudmuck | 0:06cc2cd9f340 | 223 | uint8_t CrcAutoClearOff : 1; // 3 |

| dudmuck | 0:06cc2cd9f340 | 224 | uint8_t CrcOn : 1; // 4 |

| dudmuck | 0:06cc2cd9f340 | 225 | uint8_t DcFree : 2; // 5,6 |

| dudmuck | 0:06cc2cd9f340 | 226 | uint8_t PacketFormatVariable : 1; // 7 1=variable length, 0=fixed |

| dudmuck | 0:06cc2cd9f340 | 227 | } bits; |

| dudmuck | 0:06cc2cd9f340 | 228 | uint8_t octet; |

| dudmuck | 0:06cc2cd9f340 | 229 | } RegPktConfig1_t; |

| dudmuck | 0:06cc2cd9f340 | 230 | |

| dudmuck | 0:06cc2cd9f340 | 231 | typedef union { |

| dudmuck | 0:06cc2cd9f340 | 232 | struct { // sx1232 register 0x31 |

| dudmuck | 0:06cc2cd9f340 | 233 | uint8_t PayloadLengthHi : 3; // 0,1,2 PayloadLength(10:8) |

| dudmuck | 0:06cc2cd9f340 | 234 | uint8_t BeaconOn : 1; // 3 |

| dudmuck | 0:06cc2cd9f340 | 235 | uint8_t IoHomePowerFrame : 1; // 4 CRC LFSR init: 0=0x1d0f, 1=0x0000=powerlink |

| dudmuck | 0:06cc2cd9f340 | 236 | uint8_t IoHomeOn : 1; // 5 |

| dudmuck | 0:06cc2cd9f340 | 237 | uint8_t DataModePacket : 1; // 6 1=packet mode, 0=continuous mode |

| dudmuck | 0:06cc2cd9f340 | 238 | uint8_t unused : 1; // 7 |

| dudmuck | 0:06cc2cd9f340 | 239 | } bits; |

| dudmuck | 0:06cc2cd9f340 | 240 | uint8_t octet; |

| dudmuck | 0:06cc2cd9f340 | 241 | } RegPktConfig2_t; |

| dudmuck | 0:06cc2cd9f340 | 242 | |

| dudmuck | 0:06cc2cd9f340 | 243 | typedef union { |

| dudmuck | 0:06cc2cd9f340 | 244 | struct { // sx1232 register 0x35 |

| dudmuck | 0:06cc2cd9f340 | 245 | uint8_t FifoThreshold : 6; // 0,1,2,3,4,5 PayloadLength(10:8) |

| dudmuck | 0:06cc2cd9f340 | 246 | uint8_t unused : 1; // 6 |

| dudmuck | 0:06cc2cd9f340 | 247 | uint8_t TxStartCondition : 1; // 7 0=fifoThresh 1=fifoNotEmpty |

| dudmuck | 0:06cc2cd9f340 | 248 | } bits; |

| dudmuck | 0:06cc2cd9f340 | 249 | uint8_t octet; |

| dudmuck | 0:06cc2cd9f340 | 250 | } RegFifoThreshold_t; |

| dudmuck | 0:06cc2cd9f340 | 251 | |

| dudmuck | 0:06cc2cd9f340 | 252 | typedef union { |

| dudmuck | 0:06cc2cd9f340 | 253 | struct { // sx1232 register 0x36 |

| dudmuck | 0:06cc2cd9f340 | 254 | uint8_t FromTransmit : 1; // 0 |

| dudmuck | 0:06cc2cd9f340 | 255 | uint8_t FromIdle : 1; // 1 |

| dudmuck | 0:06cc2cd9f340 | 256 | uint8_t LowPowerSelection : 1; // 2 |

| dudmuck | 0:06cc2cd9f340 | 257 | uint8_t FromStart : 2; // 3,4 |

| dudmuck | 0:06cc2cd9f340 | 258 | uint8_t IdleMode : 1; // 5 |

| dudmuck | 0:06cc2cd9f340 | 259 | uint8_t SequencerStop : 1; // 6 |

| dudmuck | 0:06cc2cd9f340 | 260 | uint8_t SequencerStart : 1; // 7 |

| dudmuck | 0:06cc2cd9f340 | 261 | } bits; |

| dudmuck | 0:06cc2cd9f340 | 262 | uint8_t octet; |

| dudmuck | 0:06cc2cd9f340 | 263 | } RegSeqConfig1_t; // @0x36 |

| dudmuck | 0:06cc2cd9f340 | 264 | |

| dudmuck | 0:06cc2cd9f340 | 265 | typedef union { |

| dudmuck | 0:06cc2cd9f340 | 266 | struct { // sx1232 register 0x37 |

| dudmuck | 0:06cc2cd9f340 | 267 | uint8_t FromPacketReceived : 3; // 0,1,2 |

| dudmuck | 0:06cc2cd9f340 | 268 | uint8_t FromRxTimeout : 2; // 3,4 |

| dudmuck | 0:06cc2cd9f340 | 269 | uint8_t FromReceive : 3; // 5,6,7 |

| dudmuck | 0:06cc2cd9f340 | 270 | } bits; |

| dudmuck | 0:06cc2cd9f340 | 271 | uint8_t octet; |

| dudmuck | 0:06cc2cd9f340 | 272 | } RegSeqConfig2_t; // @0x37 |

| dudmuck | 0:06cc2cd9f340 | 273 | |

| dudmuck | 0:06cc2cd9f340 | 274 | typedef union { |

| dudmuck | 0:06cc2cd9f340 | 275 | struct { // sx1232 register 0x38 |

| dudmuck | 0:06cc2cd9f340 | 276 | uint8_t timer2_resol : 2; // 0,1 |

| dudmuck | 0:06cc2cd9f340 | 277 | uint8_t timer1_resol : 2; // 2,3 |

| dudmuck | 0:06cc2cd9f340 | 278 | uint8_t force_hlm_irq : 1; // 4 |

| dudmuck | 0:06cc2cd9f340 | 279 | uint8_t hlm_started : 1; // 5 |

| dudmuck | 0:06cc2cd9f340 | 280 | uint8_t unused : 2; // 6,7 |

| dudmuck | 0:06cc2cd9f340 | 281 | } bits; |

| dudmuck | 0:06cc2cd9f340 | 282 | uint8_t octet; |

| dudmuck | 0:06cc2cd9f340 | 283 | } RegTimerResol_t ; // HL42 @0x38 |

| dudmuck | 0:06cc2cd9f340 | 284 | |

| dudmuck | 0:06cc2cd9f340 | 285 | typedef union { |

| dudmuck | 0:06cc2cd9f340 | 286 | struct { // sx1232 register 0x3e |

| dudmuck | 0:06cc2cd9f340 | 287 | uint8_t SyncAddressMatch : 1; // 0 |

| dudmuck | 0:06cc2cd9f340 | 288 | uint8_t PreambleDetect : 1; // 1 |

| dudmuck | 0:06cc2cd9f340 | 289 | uint8_t Timeout : 1; // 2 rx-timeout |

| dudmuck | 0:06cc2cd9f340 | 290 | uint8_t Rssi : 1; // 3 |

| dudmuck | 0:06cc2cd9f340 | 291 | uint8_t PllLock : 1; // 4 |

| dudmuck | 0:06cc2cd9f340 | 292 | uint8_t TxReady : 1; // 5 |

| dudmuck | 0:06cc2cd9f340 | 293 | uint8_t RxReady : 1; // 6 |

| dudmuck | 0:06cc2cd9f340 | 294 | uint8_t ModeReady : 1; // 7 |

| dudmuck | 0:06cc2cd9f340 | 295 | } bits; |

| dudmuck | 0:06cc2cd9f340 | 296 | uint8_t octet; |

| dudmuck | 0:06cc2cd9f340 | 297 | } RegIrqFlags1_t; // STAT0 |

| dudmuck | 0:06cc2cd9f340 | 298 | |

| dudmuck | 0:06cc2cd9f340 | 299 | typedef union { |

| dudmuck | 0:06cc2cd9f340 | 300 | struct { // sx1232 register 0x3f |

| dudmuck | 0:06cc2cd9f340 | 301 | uint8_t LowBat : 1; // 0 "eol" |

| dudmuck | 0:06cc2cd9f340 | 302 | uint8_t CrcOk : 1; // 1 |

| dudmuck | 0:06cc2cd9f340 | 303 | uint8_t PayloadReady : 1; // 2 |

| dudmuck | 0:06cc2cd9f340 | 304 | uint8_t PacketSent : 1; // 3 |

| dudmuck | 0:06cc2cd9f340 | 305 | uint8_t FifoOverrun : 1; // 4 |

| dudmuck | 0:06cc2cd9f340 | 306 | uint8_t FifoLevel : 1; // 5 |

| dudmuck | 0:06cc2cd9f340 | 307 | uint8_t FifoEmpty : 1; // 6 |

| dudmuck | 0:06cc2cd9f340 | 308 | uint8_t FifoFull : 1; // 7 |

| dudmuck | 0:06cc2cd9f340 | 309 | } bits; |

| dudmuck | 0:06cc2cd9f340 | 310 | uint8_t octet; |

| dudmuck | 0:06cc2cd9f340 | 311 | } RegIrqFlags2_t; // STAT1 @0x3f |

| dudmuck | 0:06cc2cd9f340 | 312 | |

| dudmuck | 0:06cc2cd9f340 | 313 | typedef union { |

| dudmuck | 0:06cc2cd9f340 | 314 | struct { // sx1232 register 0x40 |

| dudmuck | 0:06cc2cd9f340 | 315 | uint8_t Dio3Mapping : 2; // 0,1 |

| dudmuck | 0:06cc2cd9f340 | 316 | uint8_t Dio2Mapping : 2; // 2,3 |

| dudmuck | 0:06cc2cd9f340 | 317 | uint8_t Dio1Mapping : 2; // 4,5 |

| dudmuck | 0:06cc2cd9f340 | 318 | uint8_t Dio0Mapping : 2; // 6,7 |

| dudmuck | 0:06cc2cd9f340 | 319 | } bits; |

| dudmuck | 0:06cc2cd9f340 | 320 | uint8_t octet; |

| dudmuck | 0:06cc2cd9f340 | 321 | } RegDioMapping1_t; |

| dudmuck | 0:06cc2cd9f340 | 322 | |

| dudmuck | 0:06cc2cd9f340 | 323 | typedef union { |

| dudmuck | 0:06cc2cd9f340 | 324 | struct { // sx1232 register 0x41 |

| dudmuck | 0:06cc2cd9f340 | 325 | uint8_t MapPreambleDetect : 1; // 0 //DIO4 assign: 1b=preambleDet 0b=rssiThresh |

| dudmuck | 0:06cc2cd9f340 | 326 | uint8_t io_mode : 3; // 1,2,3 //0=normal,1=debug,2=fpga,3=pll_tx,4=pll_rx,5=analog |

| dudmuck | 0:06cc2cd9f340 | 327 | uint8_t Dio5Mapping : 2; // 4,5 |

| dudmuck | 0:06cc2cd9f340 | 328 | uint8_t Dio4Mapping : 2; // 6,7 |

| dudmuck | 0:06cc2cd9f340 | 329 | } bits; |

| dudmuck | 0:06cc2cd9f340 | 330 | uint8_t octet; |

| dudmuck | 0:06cc2cd9f340 | 331 | } RegDioMapping2_t; |

| dudmuck | 0:06cc2cd9f340 | 332 | |

| dudmuck | 0:06cc2cd9f340 | 333 | /***************************************************/ |

| dudmuck | 0:06cc2cd9f340 | 334 | |

| dudmuck | 0:06cc2cd9f340 | 335 | typedef enum { |

| dudmuck | 0:06cc2cd9f340 | 336 | SERVICE_NONE = 0, |

| dudmuck | 0:06cc2cd9f340 | 337 | SERVICE_ERROR, //! |

| dudmuck | 0:06cc2cd9f340 | 338 | SERVICE_READ_FIFO //! request to call read_fifo() |

| dudmuck | 0:06cc2cd9f340 | 339 | } service_action_e; |

| dudmuck | 0:06cc2cd9f340 | 340 | |

| dudmuck | 0:06cc2cd9f340 | 341 | /** FSK radio transceiver for 800/900MHz. |

| dudmuck | 0:06cc2cd9f340 | 342 | * Compared with ADF7023 in Xbee PRO 900: |

| dudmuck | 0:06cc2cd9f340 | 343 | * Receiver bandwidth configurable to narrower operation, for performance at lower bitrates. |

| dudmuck | 0:06cc2cd9f340 | 344 | * Transmit power option to +20dBm. |

| dudmuck | 0:06cc2cd9f340 | 345 | * Superior blocking immunity in receiver. |

| dudmuck | 0:06cc2cd9f340 | 346 | * http://www.semtech.com/apps/product.php?pn=sx1232 |

| dudmuck | 0:06cc2cd9f340 | 347 | */ |

| dudmuck | 0:06cc2cd9f340 | 348 | class SX1232 { |

| dudmuck | 0:06cc2cd9f340 | 349 | public: |

| dudmuck | 0:06cc2cd9f340 | 350 | /** Create SX1232 instance |

| dudmuck | 0:06cc2cd9f340 | 351 | * @param mosi SPI master-out pin |

| dudmuck | 0:06cc2cd9f340 | 352 | * @param miso SPI master-in pin |

| dudmuck | 0:06cc2cd9f340 | 353 | * @param sclk SPI clock pin |

| dudmuck | 0:06cc2cd9f340 | 354 | * @param cs SPI chip-select pin |

| dudmuck | 0:06cc2cd9f340 | 355 | * @param rst radio hardware reset pin |

| dudmuck | 0:06cc2cd9f340 | 356 | * @param dio_0 interrupt pin from radio |

| dudmuck | 0:06cc2cd9f340 | 357 | */ |

| dudmuck | 0:06cc2cd9f340 | 358 | SX1232(PinName mosi, PinName miso, PinName sclk, PinName cs, PinName rst, PinName dio_0); |

| dudmuck | 0:06cc2cd9f340 | 359 | |

| dudmuck | 0:06cc2cd9f340 | 360 | ~SX1232(); |

| dudmuck | 0:06cc2cd9f340 | 361 | |

| dudmuck | 0:06cc2cd9f340 | 362 | /** set receiver bandwidth |

| dudmuck | 0:06cc2cd9f340 | 363 | * @note Value is selected to frequency deviation and bit-rate (occupied bandwidth) |

| dudmuck | 0:06cc2cd9f340 | 364 | * @note Narrower bandwidths may require AFC, depending on reference crystal accuracy |

| dudmuck | 0:06cc2cd9f340 | 365 | * @note RX start-up time is slower at narrower bandwidths |

| dudmuck | 0:06cc2cd9f340 | 366 | * @note you cannot change bandwith while in receive mode |

| dudmuck | 0:06cc2cd9f340 | 367 | * @note usable range is 2.6KHz to 250KHz |

| dudmuck | 0:06cc2cd9f340 | 368 | */ |

| dudmuck | 0:06cc2cd9f340 | 369 | void set_rx_dcc_bw_hz(uint32_t dccValue, uint32_t bw_hz ); |

| dudmuck | 0:06cc2cd9f340 | 370 | /** get receiver bandwidth |

| dudmuck | 0:06cc2cd9f340 | 371 | * @returns the receiver bandwidth in Hz |

| dudmuck | 0:06cc2cd9f340 | 372 | */ |

| dudmuck | 0:06cc2cd9f340 | 373 | uint32_t get_rx_bw_hz(uint8_t addr); |

| dudmuck | 0:06cc2cd9f340 | 374 | |

| dudmuck | 0:06cc2cd9f340 | 375 | /** set center operating frequency |

| dudmuck | 0:06cc2cd9f340 | 376 | * @param MHz operating frequency in MHz |

| dudmuck | 0:06cc2cd9f340 | 377 | */ |

| dudmuck | 0:06cc2cd9f340 | 378 | void set_frf_MHz( float MHz ); |

| dudmuck | 0:06cc2cd9f340 | 379 | |

| dudmuck | 0:06cc2cd9f340 | 380 | /** get center operating frequency |

| dudmuck | 0:06cc2cd9f340 | 381 | * @returns operating frequency in MHz |

| dudmuck | 0:06cc2cd9f340 | 382 | */ |

| dudmuck | 0:06cc2cd9f340 | 383 | float get_frf_MHz(void); |

| dudmuck | 0:06cc2cd9f340 | 384 | |

| dudmuck | 0:06cc2cd9f340 | 385 | /** set over-the-air bitrate |

| dudmuck | 0:06cc2cd9f340 | 386 | * @param bps bits per second |

| dudmuck | 0:06cc2cd9f340 | 387 | * @note TX frequency deviation must be set according to desired modulation index |

| dudmuck | 0:06cc2cd9f340 | 388 | * @note you cannot change bitrate while in receive mode |

| dudmuck | 0:06cc2cd9f340 | 389 | */ |

| dudmuck | 0:06cc2cd9f340 | 390 | void set_bitrate(uint32_t bps); |

| dudmuck | 0:06cc2cd9f340 | 391 | /** get over-the-air bitrte |

| dudmuck | 0:06cc2cd9f340 | 392 | * @returns bits per second |

| dudmuck | 0:06cc2cd9f340 | 393 | */ |

| dudmuck | 0:06cc2cd9f340 | 394 | uint32_t get_bitrate(void); |

| dudmuck | 0:06cc2cd9f340 | 395 | |

| dudmuck | 0:06cc2cd9f340 | 396 | /** set transmitted frequency deviation |

| dudmuck | 0:06cc2cd9f340 | 397 | * @param hz frequency deviation in Hz |

| dudmuck | 0:06cc2cd9f340 | 398 | * @note occupied bandwith is primarily determined by fdev; set receiver bandwidth appropriately |

| dudmuck | 0:06cc2cd9f340 | 399 | * @note usable range is 600Hz to 200KHz |

| dudmuck | 0:06cc2cd9f340 | 400 | */ |

| dudmuck | 0:06cc2cd9f340 | 401 | void set_tx_fdev_hz(uint32_t hz); |

| dudmuck | 0:06cc2cd9f340 | 402 | /** get transmitted frequency deviation |

| dudmuck | 0:06cc2cd9f340 | 403 | * @returns transmitter frequency deviation in Hz |

| dudmuck | 0:06cc2cd9f340 | 404 | */ |

| dudmuck | 0:06cc2cd9f340 | 405 | uint32_t get_tx_fdev_hz(void); |

| dudmuck | 0:06cc2cd9f340 | 406 | |

| dudmuck | 0:06cc2cd9f340 | 407 | /** enable AFC with preamble detector |

| dudmuck | 0:06cc2cd9f340 | 408 | * @note AFC generally used when crystal tolerance is worse than receiver bandwidth. Narrower bandwidths require better ppm on crystal, without AFC. |

| dudmuck | 0:06cc2cd9f340 | 409 | * @note this enables with RxTrigger on preamble detect without RSSI threshold. |

| dudmuck | 0:06cc2cd9f340 | 410 | * @note other option is to also use RSSI threshold, but requires calibration from ambient RSSI on vacant channel. |

| dudmuck | 0:06cc2cd9f340 | 411 | */ |

| dudmuck | 0:06cc2cd9f340 | 412 | void enable_afc(char enable); |

| dudmuck | 0:06cc2cd9f340 | 413 | |

| dudmuck | 0:06cc2cd9f340 | 414 | /** write payload length |

| dudmuck | 0:06cc2cd9f340 | 415 | * @note PayloadLength is maximum 255 in variable-length packet format, or fixed-length maximum of 2047 bytes. |

| dudmuck | 0:06cc2cd9f340 | 416 | * @note if PacketFormat is fixed-length, then PayloadLength of 0 enables unlimited length mode. |

| dudmuck | 0:06cc2cd9f340 | 417 | * @note In variable length mode, this sets maximum allowed received packet length. |

| dudmuck | 0:06cc2cd9f340 | 418 | * @param len PayloadLength |

| dudmuck | 0:06cc2cd9f340 | 419 | */ |

| dudmuck | 0:06cc2cd9f340 | 420 | void set_RegPayloadLength(uint16_t len); |

| dudmuck | 0:06cc2cd9f340 | 421 | /** read payload length |

| dudmuck | 0:06cc2cd9f340 | 422 | */ |

| dudmuck | 0:06cc2cd9f340 | 423 | uint16_t get_PayloadLength(void); |

| dudmuck | 0:06cc2cd9f340 | 424 | |

| dudmuck | 0:06cc2cd9f340 | 425 | /** transmit a packet |

| dudmuck | 0:06cc2cd9f340 | 426 | * @param len size of packet, variable-length format only. unused in fixed-length format. |

| dudmuck | 0:06cc2cd9f340 | 427 | * @note Limited to 64 bytes. Lengths greater than 64 require flow control (radio FIFO size) |

| dudmuck | 0:06cc2cd9f340 | 428 | */ |

| dudmuck | 0:06cc2cd9f340 | 429 | void start_tx(uint8_t len); |

| dudmuck | 0:06cc2cd9f340 | 430 | |

| dudmuck | 0:06cc2cd9f340 | 431 | /** start receive mode |

| dudmuck | 0:06cc2cd9f340 | 432 | * @note the variable service_action needs to be monitored to indicate read_fifo() needs to be called to pull packet from FIFO. |

| dudmuck | 0:06cc2cd9f340 | 433 | */ |

| dudmuck | 0:06cc2cd9f340 | 434 | void start_rx(void); |

| dudmuck | 0:06cc2cd9f340 | 435 | /** Called by main program when indicated by service_action variable, to pull recevied packet from radio FIFO. |

| dudmuck | 0:06cc2cd9f340 | 436 | * @returns count of bytes received |

| dudmuck | 0:06cc2cd9f340 | 437 | * @note received packet in rx_buf[] |

| dudmuck | 0:06cc2cd9f340 | 438 | */ |

| dudmuck | 0:06cc2cd9f340 | 439 | int read_fifo(void); |

| dudmuck | 0:06cc2cd9f340 | 440 | |

| dudmuck | 0:06cc2cd9f340 | 441 | void set_opmode(chip_mode_e mode); |

| dudmuck | 0:06cc2cd9f340 | 442 | |

| dudmuck | 0:06cc2cd9f340 | 443 | /** reset radio using pin |

| dudmuck | 0:06cc2cd9f340 | 444 | */ |

| dudmuck | 0:06cc2cd9f340 | 445 | void hw_reset(void); |

| dudmuck | 0:06cc2cd9f340 | 446 | /** initialise SX1232 class to radio |

| dudmuck | 0:06cc2cd9f340 | 447 | * @note this is called from class instantiation, but must also be manually called after hardware reset |

| dudmuck | 0:06cc2cd9f340 | 448 | */ |

| dudmuck | 0:06cc2cd9f340 | 449 | void init(void); |

| dudmuck | 0:06cc2cd9f340 | 450 | |

| dudmuck | 0:06cc2cd9f340 | 451 | /** read register from radio |

| dudmuck | 0:06cc2cd9f340 | 452 | * @param addr register address |

| dudmuck | 0:06cc2cd9f340 | 453 | * @returns the value read from the register |

| dudmuck | 0:06cc2cd9f340 | 454 | */ |

| dudmuck | 0:06cc2cd9f340 | 455 | uint8_t read_reg(uint8_t addr); |

| dudmuck | 0:06cc2cd9f340 | 456 | int16_t read_reg_s16(uint8_t addr); // for signed 16bit values, such as AFC/FEI |

| dudmuck | 0:06cc2cd9f340 | 457 | |

| dudmuck | 0:06cc2cd9f340 | 458 | /** write register to radio |

| dudmuck | 0:06cc2cd9f340 | 459 | * @param addr register address |

| dudmuck | 0:06cc2cd9f340 | 460 | * @param data byte to write |

| dudmuck | 0:06cc2cd9f340 | 461 | */ |

| dudmuck | 0:06cc2cd9f340 | 462 | void write_reg(uint8_t addr, uint8_t data); |

| dudmuck | 0:06cc2cd9f340 | 463 | |

| dudmuck | 0:06cc2cd9f340 | 464 | //! set from ISR to indicate an action to be performed from main loop |

| dudmuck | 0:06cc2cd9f340 | 465 | volatile service_action_e service_action; |

| dudmuck | 0:06cc2cd9f340 | 466 | |

| dudmuck | 0:06cc2cd9f340 | 467 | //! RF transmit packet buffer |

| dudmuck | 0:06cc2cd9f340 | 468 | uint8_t tx_buf[64]; |

| dudmuck | 0:06cc2cd9f340 | 469 | |

| dudmuck | 0:06cc2cd9f340 | 470 | //! RF receive packet buffer |

| dudmuck | 0:06cc2cd9f340 | 471 | uint8_t rx_buf[64]; |

| dudmuck | 0:06cc2cd9f340 | 472 | |

| dudmuck | 0:06cc2cd9f340 | 473 | //! operating mode |

| dudmuck | 0:06cc2cd9f340 | 474 | RegOpMode_t RegOpMode; |

| dudmuck | 0:06cc2cd9f340 | 475 | |

| dudmuck | 0:06cc2cd9f340 | 476 | //! pin assignments |

| dudmuck | 0:06cc2cd9f340 | 477 | RegDioMapping1_t RegDioMapping1; |

| dudmuck | 0:06cc2cd9f340 | 478 | |

| dudmuck | 0:06cc2cd9f340 | 479 | //! pin assignments |

| dudmuck | 0:06cc2cd9f340 | 480 | RegDioMapping2_t RegDioMapping2; |

| dudmuck | 0:06cc2cd9f340 | 481 | |

| dudmuck | 0:06cc2cd9f340 | 482 | //! packet format configuration |

| dudmuck | 0:06cc2cd9f340 | 483 | RegPktConfig1_t RegPktConfig1; |

| dudmuck | 0:06cc2cd9f340 | 484 | |

| dudmuck | 0:06cc2cd9f340 | 485 | //! packet mode control and payload length MSB |

| dudmuck | 0:06cc2cd9f340 | 486 | RegPktConfig2_t RegPktConfig2; |

| dudmuck | 0:06cc2cd9f340 | 487 | |

| dudmuck | 0:06cc2cd9f340 | 488 | //! payload length LSByte |

| dudmuck | 0:06cc2cd9f340 | 489 | uint8_t RegPayloadLength; |

| dudmuck | 0:06cc2cd9f340 | 490 | |

| dudmuck | 0:06cc2cd9f340 | 491 | //! TxStartCondition |

| dudmuck | 0:06cc2cd9f340 | 492 | RegFifoThreshold_t RegFifoThreshold; |

| dudmuck | 0:06cc2cd9f340 | 493 | |

| dudmuck | 0:06cc2cd9f340 | 494 | //! AutoRestartRx configuration and start-of-frame control |

| dudmuck | 0:06cc2cd9f340 | 495 | RegSyncConfig_t RegSyncConfig; |

| dudmuck | 0:06cc2cd9f340 | 496 | |

| dudmuck | 0:06cc2cd9f340 | 497 | //! receiver preamble detector control |

| dudmuck | 0:06cc2cd9f340 | 498 | RegPreambleDetect_t RegPreambleDetect; |

| dudmuck | 0:06cc2cd9f340 | 499 | |

| dudmuck | 0:06cc2cd9f340 | 500 | //! TX preamble length |

| dudmuck | 0:06cc2cd9f340 | 501 | uint8_t RegPreambleMsb; |

| dudmuck | 0:06cc2cd9f340 | 502 | |

| dudmuck | 0:06cc2cd9f340 | 503 | //! TX preamble length |

| dudmuck | 0:06cc2cd9f340 | 504 | uint8_t RegPreambleLsb; |

| dudmuck | 0:06cc2cd9f340 | 505 | |

| dudmuck | 0:06cc2cd9f340 | 506 | //! transmitter power configuration |

| dudmuck | 0:06cc2cd9f340 | 507 | RegPaConfig_t RegPaConfig; |

| dudmuck | 0:06cc2cd9f340 | 508 | |

| dudmuck | 0:06cc2cd9f340 | 509 | //! AFC/AGC configuration |

| dudmuck | 0:06cc2cd9f340 | 510 | RegRxConfig_t RegRxConfig; |

| dudmuck | 0:06cc2cd9f340 | 511 | |

| dudmuck | 0:06cc2cd9f340 | 512 | // receiver front-end |

| dudmuck | 0:06cc2cd9f340 | 513 | RegLna_t RegLna; |

| dudmuck | 0:06cc2cd9f340 | 514 | |

| dudmuck | 0:06cc2cd9f340 | 515 | //! sequencer timing |

| dudmuck | 0:06cc2cd9f340 | 516 | RegTimerResol_t RegTimerResol; |

| dudmuck | 0:06cc2cd9f340 | 517 | |

| dudmuck | 0:06cc2cd9f340 | 518 | //! receiver: trigger level for RSSI interrupt |

| dudmuck | 0:06cc2cd9f340 | 519 | uint8_t RegRssiThresh; |

| dudmuck | 0:06cc2cd9f340 | 520 | |

| dudmuck | 0:06cc2cd9f340 | 521 | //! sequencer control |

| dudmuck | 0:06cc2cd9f340 | 522 | RegSeqConfig1_t RegSeqConfig1; |

| dudmuck | 0:06cc2cd9f340 | 523 | |

| dudmuck | 0:06cc2cd9f340 | 524 | //! sequencer control |

| dudmuck | 0:06cc2cd9f340 | 525 | RegSeqConfig2_t RegSeqConfig2; |

| dudmuck | 0:06cc2cd9f340 | 526 | |

| dudmuck | 0:06cc2cd9f340 | 527 | //! AFC clearing control and manual AFC trigger |

| dudmuck | 0:06cc2cd9f340 | 528 | RegAfcFei_t RegAfcFei; |

| dudmuck | 0:06cc2cd9f340 | 529 | |

| dudmuck | 0:06cc2cd9f340 | 530 | RegOokPeak_t RegOokPeak; |

| dudmuck | 0:06cc2cd9f340 | 531 | |

| dudmuck | 0:06cc2cd9f340 | 532 | private: |

| dudmuck | 0:06cc2cd9f340 | 533 | SPI m_spi; |

| dudmuck | 0:06cc2cd9f340 | 534 | DigitalOut m_cs; |

| dudmuck | 0:06cc2cd9f340 | 535 | DigitalInOut reset_pin; |

| dudmuck | 0:06cc2cd9f340 | 536 | void dio0_callback(void); |

| dudmuck | 0:06cc2cd9f340 | 537 | void ComputeRxBwMantExp( uint32_t rxBwValue, uint8_t* mantisse, uint8_t* exponent ); |

| dudmuck | 0:06cc2cd9f340 | 538 | uint32_t ComputeRxBw( uint8_t mantisse, uint8_t exponent ); |

| dudmuck | 0:06cc2cd9f340 | 539 | void write_fifo__varlen(uint8_t len); |

| dudmuck | 0:06cc2cd9f340 | 540 | void write_fifo__fixedlen(void); |

| dudmuck | 0:06cc2cd9f340 | 541 | |

| dudmuck | 0:06cc2cd9f340 | 542 | |

| dudmuck | 0:06cc2cd9f340 | 543 | protected: |

| dudmuck | 0:06cc2cd9f340 | 544 | InterruptIn dio0; |

| dudmuck | 0:06cc2cd9f340 | 545 | FunctionPointer _callback_rx; |

| dudmuck | 0:06cc2cd9f340 | 546 | }; |

| dudmuck | 0:06cc2cd9f340 | 547 | |

| dudmuck | 0:06cc2cd9f340 | 548 | |

| dudmuck | 0:06cc2cd9f340 | 549 | #endif /* SX1232_H */ |