Garage Door Monitor and Opener

Dependencies: X_NUCLEO_COMMON ST_INTERFACES

Introduction

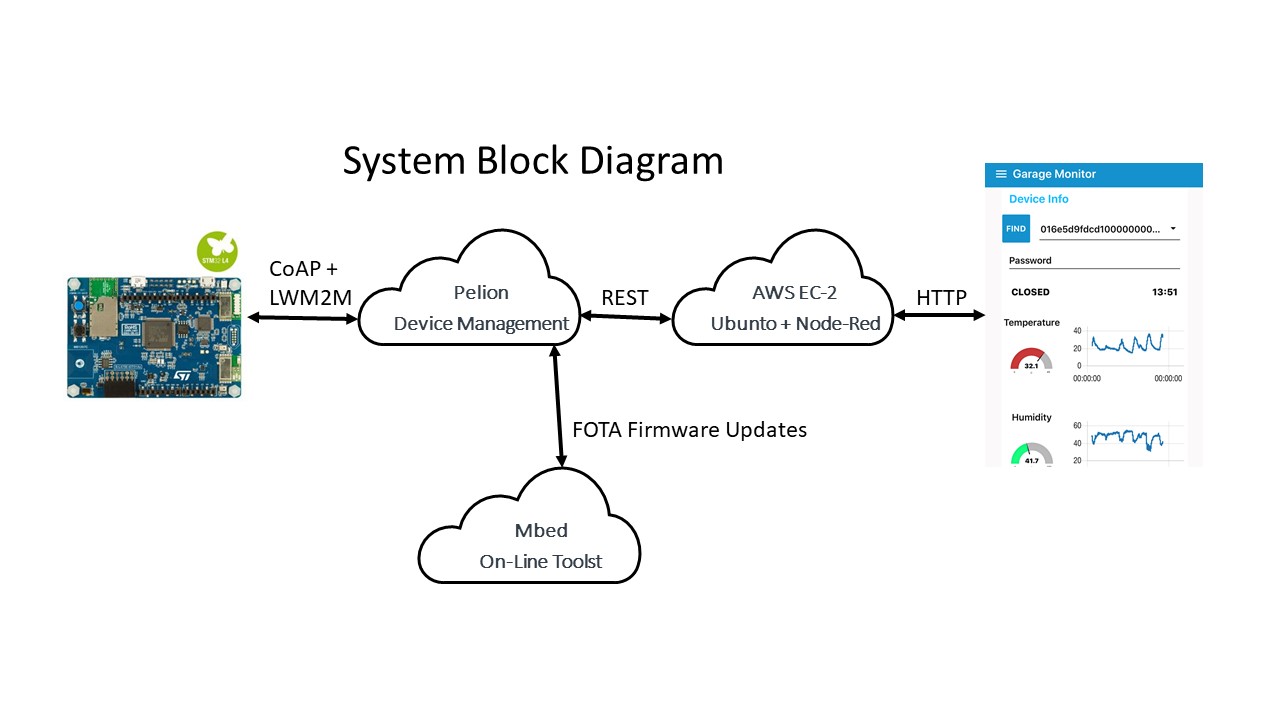

This system implements a simple garage door opener and environmental monitor. The hardware connects to the internet using Wi-Fi then on to the Pelion Device Management Platform which provides device monitoring and secure firmware updates over the air (FOTA). Pelion Device Management provides a flexible set of REST APIs which we will use to communicate to a web application running on an EC-2 instance in AWS. The web application will serve a web page where we can monitor and control our garage..

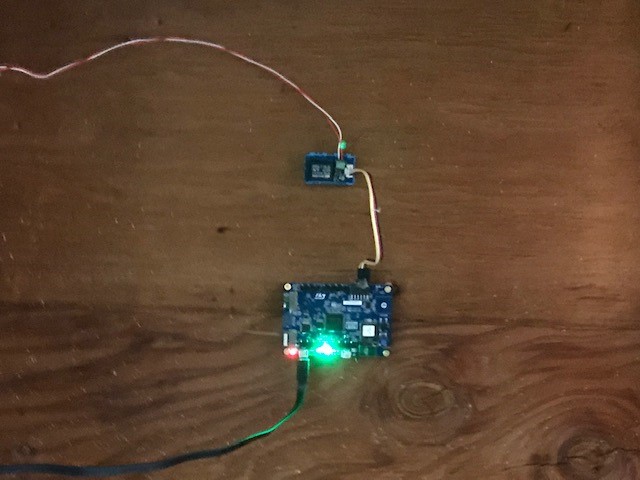

This project is intended to work on the DISCO-L475VG-IOT01A from ST Microelectronics It implements a simple actuator to drive a relay to simulate pushing the "open" button on older style garage doors which do not use a rolling code interface.

The system is designed to be mounted over the door so that the on board time of flight sensor can be used to detect if the door is open or closed.

The system also monitors temperature, humidity and barometric pressure.

Hardware Requirements:

DISCO-L475G-IOT01A https://os.mbed.com/platforms/ST-Discovery-L475E-IOT01A/

Seeed Studio Grove Relay module https://www.seeedstudio.com/Grove-Relay.html

Seeed Studio Grove cable, I used this one: https://www.seeedstudio.com/Grove-4-pin-Male-Jumper-to-Grove-4-pin-Conversion-Cable-5-PCs-per-Pack.html

Connect to the PMOD connector like this:

This shows how I installed so that the time of flight sensor can detect when the door is open

To use the project:

You will also need a Pelion developers account.

I suggest you first use the Pelion quick state to become familiar with Pelion Device Management. https://os.mbed.com/guides/connect-device-to-pelion/1/?board=ST-Discovery-L475E-IOT01A

Web Interface

For my web interface I am running node-red under Ubuntu in an EC2 instance on AWS. This can run for 12 month within the constraints of their free tier. Here is a tutorial: https://nodered.org/docs/getting-started/aws

You will also need to install several node-red add ons:

sudo npm install -g node-red-dashboard

sudo npm install -g node-red-contrib-mbed-cloud

sudo npm istall -g node-red-contrib-moment

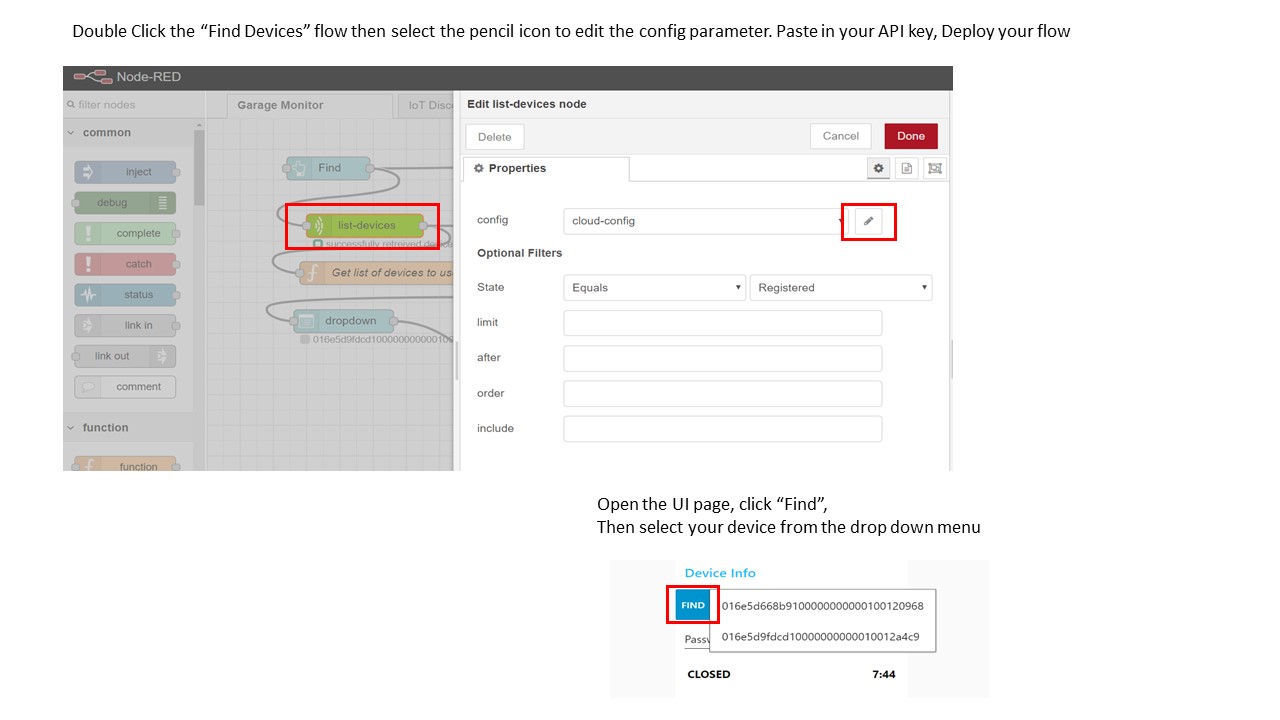

After starting node-red import the contents of GarageFlow.txt from the project, pin the flow into the page.

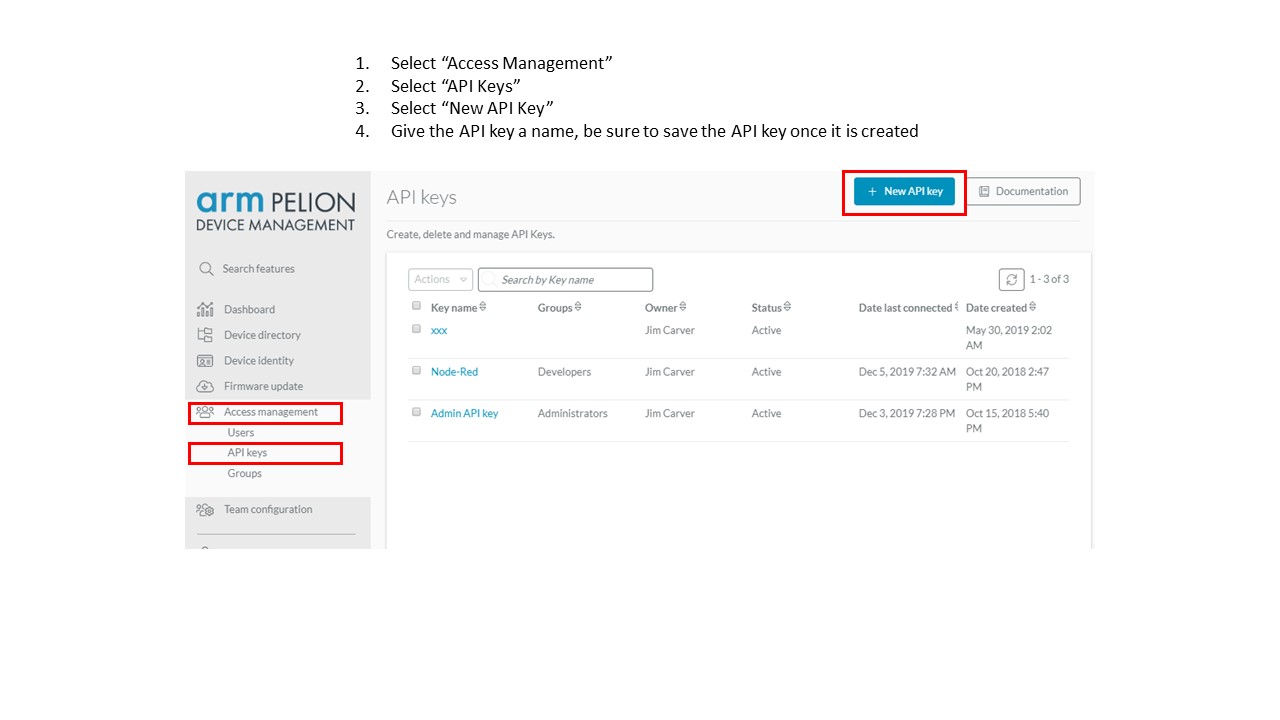

To enable your web app to access your Pelion account you need an API key.

First you will neet to use your Pelion account to create an API key.

Now we need to apply that API key to your Node-Red flow.

sensors/VL53L0X/VL53L0X.cpp@37:ec1124e5ec1f, 2019-12-05 (annotated)

- Committer:

- JimCarver

- Date:

- Thu Dec 05 19:03:48 2019 +0000

- Revision:

- 37:ec1124e5ec1f

- Parent:

- 18:a15bfe7aaebd

Bug fix

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| screamer | 18:a15bfe7aaebd | 1 | /** |

| screamer | 18:a15bfe7aaebd | 2 | ****************************************************************************** |

| screamer | 18:a15bfe7aaebd | 3 | * @file VL53L0X_class.cpp |

| screamer | 18:a15bfe7aaebd | 4 | * @author IMG |

| screamer | 18:a15bfe7aaebd | 5 | * @version V0.0.1 |

| screamer | 18:a15bfe7aaebd | 6 | * @date 28-June-2016 |

| screamer | 18:a15bfe7aaebd | 7 | * @brief Implementation file for the VL53L0X driver class |

| screamer | 18:a15bfe7aaebd | 8 | ****************************************************************************** |

| screamer | 18:a15bfe7aaebd | 9 | * @attention |

| screamer | 18:a15bfe7aaebd | 10 | * |

| screamer | 18:a15bfe7aaebd | 11 | * <h2><center>© COPYRIGHT(c) 2016 STMicroelectronics</center></h2> |

| screamer | 18:a15bfe7aaebd | 12 | * |

| screamer | 18:a15bfe7aaebd | 13 | * Redistribution and use in source and binary forms, with or without modification, |

| screamer | 18:a15bfe7aaebd | 14 | * are permitted provided that the following conditions are met: |

| screamer | 18:a15bfe7aaebd | 15 | * 1. Redistributions of source code must retain the above copyright notice, |

| screamer | 18:a15bfe7aaebd | 16 | * this list of conditions and the following disclaimer. |

| screamer | 18:a15bfe7aaebd | 17 | * 2. Redistributions in binary form must reproduce the above copyright notice, |

| screamer | 18:a15bfe7aaebd | 18 | * this list of conditions and the following disclaimer in the documentation |

| screamer | 18:a15bfe7aaebd | 19 | * and/or other materials provided with the distribution. |

| screamer | 18:a15bfe7aaebd | 20 | * 3. Neither the name of STMicroelectronics nor the names of its contributors |

| screamer | 18:a15bfe7aaebd | 21 | * may be used to endorse or promote products derived from this software |

| screamer | 18:a15bfe7aaebd | 22 | * without specific prior written permission. |

| screamer | 18:a15bfe7aaebd | 23 | * |

| screamer | 18:a15bfe7aaebd | 24 | * THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" |

| screamer | 18:a15bfe7aaebd | 25 | * AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE |

| screamer | 18:a15bfe7aaebd | 26 | * IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE |

| screamer | 18:a15bfe7aaebd | 27 | * DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE |

| screamer | 18:a15bfe7aaebd | 28 | * FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL |

| screamer | 18:a15bfe7aaebd | 29 | * DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR |

| screamer | 18:a15bfe7aaebd | 30 | * SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER |

| screamer | 18:a15bfe7aaebd | 31 | * CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, |

| screamer | 18:a15bfe7aaebd | 32 | * OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE |

| screamer | 18:a15bfe7aaebd | 33 | * OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE. |

| screamer | 18:a15bfe7aaebd | 34 | * |

| screamer | 18:a15bfe7aaebd | 35 | ****************************************************************************** |

| screamer | 18:a15bfe7aaebd | 36 | */ |

| screamer | 18:a15bfe7aaebd | 37 | |

| screamer | 18:a15bfe7aaebd | 38 | /* Includes */ |

| screamer | 18:a15bfe7aaebd | 39 | #include <stdlib.h> |

| screamer | 18:a15bfe7aaebd | 40 | |

| screamer | 18:a15bfe7aaebd | 41 | #include "VL53L0X.h" |

| screamer | 18:a15bfe7aaebd | 42 | |

| screamer | 18:a15bfe7aaebd | 43 | //#include "VL53L0X_api_core.h" |

| screamer | 18:a15bfe7aaebd | 44 | //#include "VL53L0X_api_calibration.h" |

| screamer | 18:a15bfe7aaebd | 45 | //#include "VL53L0X_api_strings.h" |

| screamer | 18:a15bfe7aaebd | 46 | #include "VL53L0X_interrupt_threshold_settings.h" |

| screamer | 18:a15bfe7aaebd | 47 | #include "VL53L0X_tuning.h" |

| screamer | 18:a15bfe7aaebd | 48 | #include "VL53L0X_types.h" |

| screamer | 18:a15bfe7aaebd | 49 | |

| screamer | 18:a15bfe7aaebd | 50 | |

| screamer | 18:a15bfe7aaebd | 51 | /****************** define for i2c configuration *******************************/ |

| screamer | 18:a15bfe7aaebd | 52 | |

| screamer | 18:a15bfe7aaebd | 53 | #define TEMP_BUF_SIZE 64 |

| screamer | 18:a15bfe7aaebd | 54 | |

| screamer | 18:a15bfe7aaebd | 55 | /** Maximum buffer size to be used in i2c */ |

| screamer | 18:a15bfe7aaebd | 56 | #define VL53L0X_MAX_I2C_XFER_SIZE 64 /* Maximum buffer size to be used in i2c */ |

| screamer | 18:a15bfe7aaebd | 57 | #define VL53L0X_I2C_USER_VAR /* none but could be for a flag var to get/pass to mutex interruptible return flags and try again */ |

| screamer | 18:a15bfe7aaebd | 58 | |

| screamer | 18:a15bfe7aaebd | 59 | |

| screamer | 18:a15bfe7aaebd | 60 | #define LOG_FUNCTION_START(fmt, ...) \ |

| screamer | 18:a15bfe7aaebd | 61 | _LOG_FUNCTION_START(TRACE_MODULE_API, fmt, ##__VA_ARGS__) |

| screamer | 18:a15bfe7aaebd | 62 | #define LOG_FUNCTION_END(status, ...) \ |

| screamer | 18:a15bfe7aaebd | 63 | _LOG_FUNCTION_END(TRACE_MODULE_API, status, ##__VA_ARGS__) |

| screamer | 18:a15bfe7aaebd | 64 | #define LOG_FUNCTION_END_FMT(status, fmt, ...) \ |

| screamer | 18:a15bfe7aaebd | 65 | _LOG_FUNCTION_END_FMT(TRACE_MODULE_API, status, fmt, ##__VA_ARGS__) |

| screamer | 18:a15bfe7aaebd | 66 | |

| screamer | 18:a15bfe7aaebd | 67 | #ifdef VL53L0X_LOG_ENABLE |

| screamer | 18:a15bfe7aaebd | 68 | #define trace_print(level, ...) trace_print_module_function(TRACE_MODULE_API, \ |

| screamer | 18:a15bfe7aaebd | 69 | level, TRACE_FUNCTION_NONE, ##__VA_ARGS__) |

| screamer | 18:a15bfe7aaebd | 70 | #endif |

| screamer | 18:a15bfe7aaebd | 71 | |

| screamer | 18:a15bfe7aaebd | 72 | #define REF_ARRAY_SPAD_0 0 |

| screamer | 18:a15bfe7aaebd | 73 | #define REF_ARRAY_SPAD_5 5 |

| screamer | 18:a15bfe7aaebd | 74 | #define REF_ARRAY_SPAD_10 10 |

| screamer | 18:a15bfe7aaebd | 75 | |

| screamer | 18:a15bfe7aaebd | 76 | uint32_t refArrayQuadrants[4] = {REF_ARRAY_SPAD_10, REF_ARRAY_SPAD_5, |

| screamer | 18:a15bfe7aaebd | 77 | REF_ARRAY_SPAD_0, REF_ARRAY_SPAD_5 |

| screamer | 18:a15bfe7aaebd | 78 | }; |

| screamer | 18:a15bfe7aaebd | 79 | |

| screamer | 18:a15bfe7aaebd | 80 | |

| screamer | 18:a15bfe7aaebd | 81 | |

| screamer | 18:a15bfe7aaebd | 82 | |

| screamer | 18:a15bfe7aaebd | 83 | VL53L0X_Error VL53L0X::VL53L0X_device_read_strobe(VL53L0X_DEV dev) |

| screamer | 18:a15bfe7aaebd | 84 | { |

| screamer | 18:a15bfe7aaebd | 85 | VL53L0X_Error status = VL53L0X_ERROR_NONE; |

| screamer | 18:a15bfe7aaebd | 86 | uint8_t strobe; |

| screamer | 18:a15bfe7aaebd | 87 | uint32_t loop_nb; |

| screamer | 18:a15bfe7aaebd | 88 | LOG_FUNCTION_START(""); |

| screamer | 18:a15bfe7aaebd | 89 | |

| screamer | 18:a15bfe7aaebd | 90 | status |= VL53L0X_write_byte(dev, 0x83, 0x00); |

| screamer | 18:a15bfe7aaebd | 91 | |

| screamer | 18:a15bfe7aaebd | 92 | /* polling |

| screamer | 18:a15bfe7aaebd | 93 | * use timeout to avoid deadlock*/ |

| screamer | 18:a15bfe7aaebd | 94 | if (status == VL53L0X_ERROR_NONE) { |

| screamer | 18:a15bfe7aaebd | 95 | loop_nb = 0; |

| screamer | 18:a15bfe7aaebd | 96 | do { |

| screamer | 18:a15bfe7aaebd | 97 | status = VL53L0X_read_byte(dev, 0x83, &strobe); |

| screamer | 18:a15bfe7aaebd | 98 | if ((strobe != 0x00) || status != VL53L0X_ERROR_NONE) { |

| screamer | 18:a15bfe7aaebd | 99 | break; |

| screamer | 18:a15bfe7aaebd | 100 | } |

| screamer | 18:a15bfe7aaebd | 101 | |

| screamer | 18:a15bfe7aaebd | 102 | loop_nb = loop_nb + 1; |

| screamer | 18:a15bfe7aaebd | 103 | } while (loop_nb < VL53L0X_DEFAULT_MAX_LOOP); |

| screamer | 18:a15bfe7aaebd | 104 | |

| screamer | 18:a15bfe7aaebd | 105 | if (loop_nb >= VL53L0X_DEFAULT_MAX_LOOP) { |

| screamer | 18:a15bfe7aaebd | 106 | status = VL53L0X_ERROR_TIME_OUT; |

| screamer | 18:a15bfe7aaebd | 107 | } |

| screamer | 18:a15bfe7aaebd | 108 | } |

| screamer | 18:a15bfe7aaebd | 109 | |

| screamer | 18:a15bfe7aaebd | 110 | status |= VL53L0X_write_byte(dev, 0x83, 0x01); |

| screamer | 18:a15bfe7aaebd | 111 | |

| screamer | 18:a15bfe7aaebd | 112 | LOG_FUNCTION_END(status); |

| screamer | 18:a15bfe7aaebd | 113 | return status; |

| screamer | 18:a15bfe7aaebd | 114 | } |

| screamer | 18:a15bfe7aaebd | 115 | |

| screamer | 18:a15bfe7aaebd | 116 | VL53L0X_Error VL53L0X::VL53L0X_get_info_from_device(VL53L0X_DEV dev, uint8_t option) |

| screamer | 18:a15bfe7aaebd | 117 | { |

| screamer | 18:a15bfe7aaebd | 118 | VL53L0X_Error status = VL53L0X_ERROR_NONE; |

| screamer | 18:a15bfe7aaebd | 119 | uint8_t byte; |

| screamer | 18:a15bfe7aaebd | 120 | uint32_t tmp_dword; |

| screamer | 18:a15bfe7aaebd | 121 | uint8_t module_id; |

| screamer | 18:a15bfe7aaebd | 122 | uint8_t revision; |

| screamer | 18:a15bfe7aaebd | 123 | uint8_t reference_spad_count = 0; |

| screamer | 18:a15bfe7aaebd | 124 | uint8_t reference_spad_type = 0; |

| screamer | 18:a15bfe7aaebd | 125 | uint32_t part_uid_upper = 0; |

| screamer | 18:a15bfe7aaebd | 126 | uint32_t part_uid_lower = 0; |

| screamer | 18:a15bfe7aaebd | 127 | uint32_t offset_fixed1104_mm = 0; |

| screamer | 18:a15bfe7aaebd | 128 | int16_t offset_micro_meters = 0; |

| screamer | 18:a15bfe7aaebd | 129 | uint32_t dist_meas_tgt_fixed1104_mm = 400 << 4; |

| screamer | 18:a15bfe7aaebd | 130 | uint32_t dist_meas_fixed1104_400_mm = 0; |

| screamer | 18:a15bfe7aaebd | 131 | uint32_t signal_rate_meas_fixed1104_400_mm = 0; |

| screamer | 18:a15bfe7aaebd | 132 | char product_id[19]; |

| screamer | 18:a15bfe7aaebd | 133 | char *product_id_tmp; |

| screamer | 18:a15bfe7aaebd | 134 | uint8_t read_data_from_device_done; |

| screamer | 18:a15bfe7aaebd | 135 | FixPoint1616_t signal_rate_meas_fixed400_mm_fix = 0; |

| screamer | 18:a15bfe7aaebd | 136 | uint8_t nvm_ref_good_spad_map[VL53L0X_REF_SPAD_BUFFER_SIZE]; |

| screamer | 18:a15bfe7aaebd | 137 | int i; |

| screamer | 18:a15bfe7aaebd | 138 | |

| screamer | 18:a15bfe7aaebd | 139 | |

| screamer | 18:a15bfe7aaebd | 140 | LOG_FUNCTION_START(""); |

| screamer | 18:a15bfe7aaebd | 141 | |

| screamer | 18:a15bfe7aaebd | 142 | read_data_from_device_done = VL53L0X_GETDEVICESPECIFICPARAMETER(dev, |

| screamer | 18:a15bfe7aaebd | 143 | ReadDataFromDeviceDone); |

| screamer | 18:a15bfe7aaebd | 144 | |

| screamer | 18:a15bfe7aaebd | 145 | /* This access is done only once after that a GetDeviceInfo or |

| screamer | 18:a15bfe7aaebd | 146 | * datainit is done*/ |

| screamer | 18:a15bfe7aaebd | 147 | if (read_data_from_device_done != 7) { |

| screamer | 18:a15bfe7aaebd | 148 | |

| screamer | 18:a15bfe7aaebd | 149 | status |= VL53L0X_write_byte(dev, 0x80, 0x01); |

| screamer | 18:a15bfe7aaebd | 150 | status |= VL53L0X_write_byte(dev, 0xFF, 0x01); |

| screamer | 18:a15bfe7aaebd | 151 | status |= VL53L0X_write_byte(dev, 0x00, 0x00); |

| screamer | 18:a15bfe7aaebd | 152 | |

| screamer | 18:a15bfe7aaebd | 153 | status |= VL53L0X_write_byte(dev, 0xFF, 0x06); |

| screamer | 18:a15bfe7aaebd | 154 | status |= VL53L0X_read_byte(dev, 0x83, &byte); |

| screamer | 18:a15bfe7aaebd | 155 | status |= VL53L0X_write_byte(dev, 0x83, byte | 4); |

| screamer | 18:a15bfe7aaebd | 156 | status |= VL53L0X_write_byte(dev, 0xFF, 0x07); |

| screamer | 18:a15bfe7aaebd | 157 | status |= VL53L0X_write_byte(dev, 0x81, 0x01); |

| screamer | 18:a15bfe7aaebd | 158 | |

| screamer | 18:a15bfe7aaebd | 159 | status |= VL53L0X_polling_delay(dev); |

| screamer | 18:a15bfe7aaebd | 160 | |

| screamer | 18:a15bfe7aaebd | 161 | status |= VL53L0X_write_byte(dev, 0x80, 0x01); |

| screamer | 18:a15bfe7aaebd | 162 | |

| screamer | 18:a15bfe7aaebd | 163 | if (((option & 1) == 1) && |

| screamer | 18:a15bfe7aaebd | 164 | ((read_data_from_device_done & 1) == 0)) { |

| screamer | 18:a15bfe7aaebd | 165 | status |= VL53L0X_write_byte(dev, 0x94, 0x6b); |

| screamer | 18:a15bfe7aaebd | 166 | status |= VL53L0X_device_read_strobe(dev); |

| screamer | 18:a15bfe7aaebd | 167 | status |= VL53L0X_read_dword(dev, 0x90, &tmp_dword); |

| screamer | 18:a15bfe7aaebd | 168 | |

| screamer | 18:a15bfe7aaebd | 169 | reference_spad_count = (uint8_t)((tmp_dword >> 8) & 0x07f); |

| screamer | 18:a15bfe7aaebd | 170 | reference_spad_type = (uint8_t)((tmp_dword >> 15) & 0x01); |

| screamer | 18:a15bfe7aaebd | 171 | |

| screamer | 18:a15bfe7aaebd | 172 | status |= VL53L0X_write_byte(dev, 0x94, 0x24); |

| screamer | 18:a15bfe7aaebd | 173 | status |= VL53L0X_device_read_strobe(dev); |

| screamer | 18:a15bfe7aaebd | 174 | status |= VL53L0X_read_dword(dev, 0x90, &tmp_dword); |

| screamer | 18:a15bfe7aaebd | 175 | |

| screamer | 18:a15bfe7aaebd | 176 | |

| screamer | 18:a15bfe7aaebd | 177 | nvm_ref_good_spad_map[0] = (uint8_t)((tmp_dword >> 24) |

| screamer | 18:a15bfe7aaebd | 178 | & 0xff); |

| screamer | 18:a15bfe7aaebd | 179 | nvm_ref_good_spad_map[1] = (uint8_t)((tmp_dword >> 16) |

| screamer | 18:a15bfe7aaebd | 180 | & 0xff); |

| screamer | 18:a15bfe7aaebd | 181 | nvm_ref_good_spad_map[2] = (uint8_t)((tmp_dword >> 8) |

| screamer | 18:a15bfe7aaebd | 182 | & 0xff); |

| screamer | 18:a15bfe7aaebd | 183 | nvm_ref_good_spad_map[3] = (uint8_t)(tmp_dword & 0xff); |

| screamer | 18:a15bfe7aaebd | 184 | |

| screamer | 18:a15bfe7aaebd | 185 | status |= VL53L0X_write_byte(dev, 0x94, 0x25); |

| screamer | 18:a15bfe7aaebd | 186 | status |= VL53L0X_device_read_strobe(dev); |

| screamer | 18:a15bfe7aaebd | 187 | status |= VL53L0X_read_dword(dev, 0x90, &tmp_dword); |

| screamer | 18:a15bfe7aaebd | 188 | |

| screamer | 18:a15bfe7aaebd | 189 | nvm_ref_good_spad_map[4] = (uint8_t)((tmp_dword >> 24) |

| screamer | 18:a15bfe7aaebd | 190 | & 0xff); |

| screamer | 18:a15bfe7aaebd | 191 | nvm_ref_good_spad_map[5] = (uint8_t)((tmp_dword >> 16) |

| screamer | 18:a15bfe7aaebd | 192 | & 0xff); |

| screamer | 18:a15bfe7aaebd | 193 | } |

| screamer | 18:a15bfe7aaebd | 194 | |

| screamer | 18:a15bfe7aaebd | 195 | if (((option & 2) == 2) && |

| screamer | 18:a15bfe7aaebd | 196 | ((read_data_from_device_done & 2) == 0)) { |

| screamer | 18:a15bfe7aaebd | 197 | |

| screamer | 18:a15bfe7aaebd | 198 | status |= VL53L0X_write_byte(dev, 0x94, 0x02); |

| screamer | 18:a15bfe7aaebd | 199 | status |= VL53L0X_device_read_strobe(dev); |

| screamer | 18:a15bfe7aaebd | 200 | status |= VL53L0X_read_byte(dev, 0x90, &module_id); |

| screamer | 18:a15bfe7aaebd | 201 | |

| screamer | 18:a15bfe7aaebd | 202 | status |= VL53L0X_write_byte(dev, 0x94, 0x7B); |

| screamer | 18:a15bfe7aaebd | 203 | status |= VL53L0X_device_read_strobe(dev); |

| screamer | 18:a15bfe7aaebd | 204 | status |= VL53L0X_read_byte(dev, 0x90, &revision); |

| screamer | 18:a15bfe7aaebd | 205 | |

| screamer | 18:a15bfe7aaebd | 206 | status |= VL53L0X_write_byte(dev, 0x94, 0x77); |

| screamer | 18:a15bfe7aaebd | 207 | status |= VL53L0X_device_read_strobe(dev); |

| screamer | 18:a15bfe7aaebd | 208 | status |= VL53L0X_read_dword(dev, 0x90, &tmp_dword); |

| screamer | 18:a15bfe7aaebd | 209 | |

| screamer | 18:a15bfe7aaebd | 210 | product_id[0] = (char)((tmp_dword >> 25) & 0x07f); |

| screamer | 18:a15bfe7aaebd | 211 | product_id[1] = (char)((tmp_dword >> 18) & 0x07f); |

| screamer | 18:a15bfe7aaebd | 212 | product_id[2] = (char)((tmp_dword >> 11) & 0x07f); |

| screamer | 18:a15bfe7aaebd | 213 | product_id[3] = (char)((tmp_dword >> 4) & 0x07f); |

| screamer | 18:a15bfe7aaebd | 214 | |

| screamer | 18:a15bfe7aaebd | 215 | byte = (uint8_t)((tmp_dword & 0x00f) << 3); |

| screamer | 18:a15bfe7aaebd | 216 | |

| screamer | 18:a15bfe7aaebd | 217 | status |= VL53L0X_write_byte(dev, 0x94, 0x78); |

| screamer | 18:a15bfe7aaebd | 218 | status |= VL53L0X_device_read_strobe(dev); |

| screamer | 18:a15bfe7aaebd | 219 | status |= VL53L0X_read_dword(dev, 0x90, &tmp_dword); |

| screamer | 18:a15bfe7aaebd | 220 | |

| screamer | 18:a15bfe7aaebd | 221 | product_id[4] = (char)(byte + |

| screamer | 18:a15bfe7aaebd | 222 | ((tmp_dword >> 29) & 0x07f)); |

| screamer | 18:a15bfe7aaebd | 223 | product_id[5] = (char)((tmp_dword >> 22) & 0x07f); |

| screamer | 18:a15bfe7aaebd | 224 | product_id[6] = (char)((tmp_dword >> 15) & 0x07f); |

| screamer | 18:a15bfe7aaebd | 225 | product_id[7] = (char)((tmp_dword >> 8) & 0x07f); |

| screamer | 18:a15bfe7aaebd | 226 | product_id[8] = (char)((tmp_dword >> 1) & 0x07f); |

| screamer | 18:a15bfe7aaebd | 227 | |

| screamer | 18:a15bfe7aaebd | 228 | byte = (uint8_t)((tmp_dword & 0x001) << 6); |

| screamer | 18:a15bfe7aaebd | 229 | |

| screamer | 18:a15bfe7aaebd | 230 | status |= VL53L0X_write_byte(dev, 0x94, 0x79); |

| screamer | 18:a15bfe7aaebd | 231 | |

| screamer | 18:a15bfe7aaebd | 232 | status |= VL53L0X_device_read_strobe(dev); |

| screamer | 18:a15bfe7aaebd | 233 | |

| screamer | 18:a15bfe7aaebd | 234 | status |= VL53L0X_read_dword(dev, 0x90, &tmp_dword); |

| screamer | 18:a15bfe7aaebd | 235 | |

| screamer | 18:a15bfe7aaebd | 236 | product_id[9] = (char)(byte + |

| screamer | 18:a15bfe7aaebd | 237 | ((tmp_dword >> 26) & 0x07f)); |

| screamer | 18:a15bfe7aaebd | 238 | product_id[10] = (char)((tmp_dword >> 19) & 0x07f); |

| screamer | 18:a15bfe7aaebd | 239 | product_id[11] = (char)((tmp_dword >> 12) & 0x07f); |

| screamer | 18:a15bfe7aaebd | 240 | product_id[12] = (char)((tmp_dword >> 5) & 0x07f); |

| screamer | 18:a15bfe7aaebd | 241 | |

| screamer | 18:a15bfe7aaebd | 242 | byte = (uint8_t)((tmp_dword & 0x01f) << 2); |

| screamer | 18:a15bfe7aaebd | 243 | |

| screamer | 18:a15bfe7aaebd | 244 | status |= VL53L0X_write_byte(dev, 0x94, 0x7A); |

| screamer | 18:a15bfe7aaebd | 245 | |

| screamer | 18:a15bfe7aaebd | 246 | status |= VL53L0X_device_read_strobe(dev); |

| screamer | 18:a15bfe7aaebd | 247 | |

| screamer | 18:a15bfe7aaebd | 248 | status |= VL53L0X_read_dword(dev, 0x90, &tmp_dword); |

| screamer | 18:a15bfe7aaebd | 249 | |

| screamer | 18:a15bfe7aaebd | 250 | product_id[13] = (char)(byte + |

| screamer | 18:a15bfe7aaebd | 251 | ((tmp_dword >> 30) & 0x07f)); |

| screamer | 18:a15bfe7aaebd | 252 | product_id[14] = (char)((tmp_dword >> 23) & 0x07f); |

| screamer | 18:a15bfe7aaebd | 253 | product_id[15] = (char)((tmp_dword >> 16) & 0x07f); |

| screamer | 18:a15bfe7aaebd | 254 | product_id[16] = (char)((tmp_dword >> 9) & 0x07f); |

| screamer | 18:a15bfe7aaebd | 255 | product_id[17] = (char)((tmp_dword >> 2) & 0x07f); |

| screamer | 18:a15bfe7aaebd | 256 | product_id[18] = '\0'; |

| screamer | 18:a15bfe7aaebd | 257 | |

| screamer | 18:a15bfe7aaebd | 258 | } |

| screamer | 18:a15bfe7aaebd | 259 | |

| screamer | 18:a15bfe7aaebd | 260 | if (((option & 4) == 4) && |

| screamer | 18:a15bfe7aaebd | 261 | ((read_data_from_device_done & 4) == 0)) { |

| screamer | 18:a15bfe7aaebd | 262 | |

| screamer | 18:a15bfe7aaebd | 263 | status |= VL53L0X_write_byte(dev, 0x94, 0x7B); |

| screamer | 18:a15bfe7aaebd | 264 | status |= VL53L0X_device_read_strobe(dev); |

| screamer | 18:a15bfe7aaebd | 265 | status |= VL53L0X_read_dword(dev, 0x90, &part_uid_upper); |

| screamer | 18:a15bfe7aaebd | 266 | |

| screamer | 18:a15bfe7aaebd | 267 | status |= VL53L0X_write_byte(dev, 0x94, 0x7C); |

| screamer | 18:a15bfe7aaebd | 268 | status |= VL53L0X_device_read_strobe(dev); |

| screamer | 18:a15bfe7aaebd | 269 | status |= VL53L0X_read_dword(dev, 0x90, &part_uid_lower); |

| screamer | 18:a15bfe7aaebd | 270 | |

| screamer | 18:a15bfe7aaebd | 271 | status |= VL53L0X_write_byte(dev, 0x94, 0x73); |

| screamer | 18:a15bfe7aaebd | 272 | status |= VL53L0X_device_read_strobe(dev); |

| screamer | 18:a15bfe7aaebd | 273 | status |= VL53L0X_read_dword(dev, 0x90, &tmp_dword); |

| screamer | 18:a15bfe7aaebd | 274 | |

| screamer | 18:a15bfe7aaebd | 275 | signal_rate_meas_fixed1104_400_mm = (tmp_dword & |

| screamer | 18:a15bfe7aaebd | 276 | 0x0000000ff) << 8; |

| screamer | 18:a15bfe7aaebd | 277 | |

| screamer | 18:a15bfe7aaebd | 278 | status |= VL53L0X_write_byte(dev, 0x94, 0x74); |

| screamer | 18:a15bfe7aaebd | 279 | status |= VL53L0X_device_read_strobe(dev); |

| screamer | 18:a15bfe7aaebd | 280 | status |= VL53L0X_read_dword(dev, 0x90, &tmp_dword); |

| screamer | 18:a15bfe7aaebd | 281 | |

| screamer | 18:a15bfe7aaebd | 282 | signal_rate_meas_fixed1104_400_mm |= ((tmp_dword & |

| screamer | 18:a15bfe7aaebd | 283 | 0xff000000) >> 24); |

| screamer | 18:a15bfe7aaebd | 284 | |

| screamer | 18:a15bfe7aaebd | 285 | status |= VL53L0X_write_byte(dev, 0x94, 0x75); |

| screamer | 18:a15bfe7aaebd | 286 | status |= VL53L0X_device_read_strobe(dev); |

| screamer | 18:a15bfe7aaebd | 287 | status |= VL53L0X_read_dword(dev, 0x90, &tmp_dword); |

| screamer | 18:a15bfe7aaebd | 288 | |

| screamer | 18:a15bfe7aaebd | 289 | dist_meas_fixed1104_400_mm = (tmp_dword & 0x0000000ff) |

| screamer | 18:a15bfe7aaebd | 290 | << 8; |

| screamer | 18:a15bfe7aaebd | 291 | |

| screamer | 18:a15bfe7aaebd | 292 | status |= VL53L0X_write_byte(dev, 0x94, 0x76); |

| screamer | 18:a15bfe7aaebd | 293 | status |= VL53L0X_device_read_strobe(dev); |

| screamer | 18:a15bfe7aaebd | 294 | status |= VL53L0X_read_dword(dev, 0x90, &tmp_dword); |

| screamer | 18:a15bfe7aaebd | 295 | |

| screamer | 18:a15bfe7aaebd | 296 | dist_meas_fixed1104_400_mm |= ((tmp_dword & 0xff000000) |

| screamer | 18:a15bfe7aaebd | 297 | >> 24); |

| screamer | 18:a15bfe7aaebd | 298 | } |

| screamer | 18:a15bfe7aaebd | 299 | |

| screamer | 18:a15bfe7aaebd | 300 | status |= VL53L0X_write_byte(dev, 0x81, 0x00); |

| screamer | 18:a15bfe7aaebd | 301 | status |= VL53L0X_write_byte(dev, 0xFF, 0x06); |

| screamer | 18:a15bfe7aaebd | 302 | status |= VL53L0X_read_byte(dev, 0x83, &byte); |

| screamer | 18:a15bfe7aaebd | 303 | status |= VL53L0X_write_byte(dev, 0x83, byte & 0xfb); |

| screamer | 18:a15bfe7aaebd | 304 | status |= VL53L0X_write_byte(dev, 0xFF, 0x01); |

| screamer | 18:a15bfe7aaebd | 305 | status |= VL53L0X_write_byte(dev, 0x00, 0x01); |

| screamer | 18:a15bfe7aaebd | 306 | |

| screamer | 18:a15bfe7aaebd | 307 | status |= VL53L0X_write_byte(dev, 0xFF, 0x00); |

| screamer | 18:a15bfe7aaebd | 308 | status |= VL53L0X_write_byte(dev, 0x80, 0x00); |

| screamer | 18:a15bfe7aaebd | 309 | } |

| screamer | 18:a15bfe7aaebd | 310 | |

| screamer | 18:a15bfe7aaebd | 311 | if ((status == VL53L0X_ERROR_NONE) && |

| screamer | 18:a15bfe7aaebd | 312 | (read_data_from_device_done != 7)) { |

| screamer | 18:a15bfe7aaebd | 313 | /* Assign to variable if status is ok */ |

| screamer | 18:a15bfe7aaebd | 314 | if (((option & 1) == 1) && |

| screamer | 18:a15bfe7aaebd | 315 | ((read_data_from_device_done & 1) == 0)) { |

| screamer | 18:a15bfe7aaebd | 316 | VL53L0X_SETDEVICESPECIFICPARAMETER(dev, |

| screamer | 18:a15bfe7aaebd | 317 | ReferenceSpadCount, reference_spad_count); |

| screamer | 18:a15bfe7aaebd | 318 | |

| screamer | 18:a15bfe7aaebd | 319 | VL53L0X_SETDEVICESPECIFICPARAMETER(dev, |

| screamer | 18:a15bfe7aaebd | 320 | ReferenceSpadType, reference_spad_type); |

| screamer | 18:a15bfe7aaebd | 321 | |

| screamer | 18:a15bfe7aaebd | 322 | for (i = 0; i < VL53L0X_REF_SPAD_BUFFER_SIZE; i++) { |

| screamer | 18:a15bfe7aaebd | 323 | dev->Data.SpadData.RefGoodSpadMap[i] = |

| screamer | 18:a15bfe7aaebd | 324 | nvm_ref_good_spad_map[i]; |

| screamer | 18:a15bfe7aaebd | 325 | } |

| screamer | 18:a15bfe7aaebd | 326 | } |

| screamer | 18:a15bfe7aaebd | 327 | |

| screamer | 18:a15bfe7aaebd | 328 | if (((option & 2) == 2) && |

| screamer | 18:a15bfe7aaebd | 329 | ((read_data_from_device_done & 2) == 0)) { |

| screamer | 18:a15bfe7aaebd | 330 | VL53L0X_SETDEVICESPECIFICPARAMETER(dev, |

| screamer | 18:a15bfe7aaebd | 331 | ModuleId, module_id); |

| screamer | 18:a15bfe7aaebd | 332 | |

| screamer | 18:a15bfe7aaebd | 333 | VL53L0X_SETDEVICESPECIFICPARAMETER(dev, |

| screamer | 18:a15bfe7aaebd | 334 | Revision, revision); |

| screamer | 18:a15bfe7aaebd | 335 | |

| screamer | 18:a15bfe7aaebd | 336 | product_id_tmp = VL53L0X_GETDEVICESPECIFICPARAMETER(dev, |

| screamer | 18:a15bfe7aaebd | 337 | ProductId); |

| screamer | 18:a15bfe7aaebd | 338 | VL53L0X_COPYSTRING(product_id_tmp, product_id); |

| screamer | 18:a15bfe7aaebd | 339 | |

| screamer | 18:a15bfe7aaebd | 340 | } |

| screamer | 18:a15bfe7aaebd | 341 | |

| screamer | 18:a15bfe7aaebd | 342 | if (((option & 4) == 4) && |

| screamer | 18:a15bfe7aaebd | 343 | ((read_data_from_device_done & 4) == 0)) { |

| screamer | 18:a15bfe7aaebd | 344 | VL53L0X_SETDEVICESPECIFICPARAMETER(dev, |

| screamer | 18:a15bfe7aaebd | 345 | PartUIDUpper, part_uid_upper); |

| screamer | 18:a15bfe7aaebd | 346 | |

| screamer | 18:a15bfe7aaebd | 347 | VL53L0X_SETDEVICESPECIFICPARAMETER(dev, |

| screamer | 18:a15bfe7aaebd | 348 | PartUIDLower, part_uid_lower); |

| screamer | 18:a15bfe7aaebd | 349 | |

| screamer | 18:a15bfe7aaebd | 350 | signal_rate_meas_fixed400_mm_fix = |

| screamer | 18:a15bfe7aaebd | 351 | VL53L0X_FIXPOINT97TOFIXPOINT1616( |

| screamer | 18:a15bfe7aaebd | 352 | signal_rate_meas_fixed1104_400_mm); |

| screamer | 18:a15bfe7aaebd | 353 | |

| screamer | 18:a15bfe7aaebd | 354 | VL53L0X_SETDEVICESPECIFICPARAMETER(dev, |

| screamer | 18:a15bfe7aaebd | 355 | SignalRateMeasFixed400mm, |

| screamer | 18:a15bfe7aaebd | 356 | signal_rate_meas_fixed400_mm_fix); |

| screamer | 18:a15bfe7aaebd | 357 | |

| screamer | 18:a15bfe7aaebd | 358 | offset_micro_meters = 0; |

| screamer | 18:a15bfe7aaebd | 359 | if (dist_meas_fixed1104_400_mm != 0) { |

| screamer | 18:a15bfe7aaebd | 360 | offset_fixed1104_mm = |

| screamer | 18:a15bfe7aaebd | 361 | dist_meas_fixed1104_400_mm - |

| screamer | 18:a15bfe7aaebd | 362 | dist_meas_tgt_fixed1104_mm; |

| screamer | 18:a15bfe7aaebd | 363 | offset_micro_meters = (offset_fixed1104_mm |

| screamer | 18:a15bfe7aaebd | 364 | * 1000) >> 4; |

| screamer | 18:a15bfe7aaebd | 365 | offset_micro_meters *= -1; |

| screamer | 18:a15bfe7aaebd | 366 | } |

| screamer | 18:a15bfe7aaebd | 367 | |

| screamer | 18:a15bfe7aaebd | 368 | PALDevDataSet(dev, |

| screamer | 18:a15bfe7aaebd | 369 | Part2PartOffsetAdjustmentNVMMicroMeter, |

| screamer | 18:a15bfe7aaebd | 370 | offset_micro_meters); |

| screamer | 18:a15bfe7aaebd | 371 | } |

| screamer | 18:a15bfe7aaebd | 372 | byte = (uint8_t)(read_data_from_device_done | option); |

| screamer | 18:a15bfe7aaebd | 373 | VL53L0X_SETDEVICESPECIFICPARAMETER(dev, ReadDataFromDeviceDone, |

| screamer | 18:a15bfe7aaebd | 374 | byte); |

| screamer | 18:a15bfe7aaebd | 375 | } |

| screamer | 18:a15bfe7aaebd | 376 | |

| screamer | 18:a15bfe7aaebd | 377 | LOG_FUNCTION_END(status); |

| screamer | 18:a15bfe7aaebd | 378 | return status; |

| screamer | 18:a15bfe7aaebd | 379 | } |

| screamer | 18:a15bfe7aaebd | 380 | |

| screamer | 18:a15bfe7aaebd | 381 | VL53L0X_Error VL53L0X::wrapped_VL53L0X_get_offset_calibration_data_micro_meter(VL53L0X_DEV dev, |

| screamer | 18:a15bfe7aaebd | 382 | int32_t *p_offset_calibration_data_micro_meter) |

| screamer | 18:a15bfe7aaebd | 383 | { |

| screamer | 18:a15bfe7aaebd | 384 | VL53L0X_Error status = VL53L0X_ERROR_NONE; |

| screamer | 18:a15bfe7aaebd | 385 | uint16_t range_offset_register; |

| screamer | 18:a15bfe7aaebd | 386 | int16_t c_max_offset = 2047; |

| screamer | 18:a15bfe7aaebd | 387 | int16_t c_offset_range = 4096; |

| screamer | 18:a15bfe7aaebd | 388 | |

| screamer | 18:a15bfe7aaebd | 389 | /* Note that offset has 10.2 format */ |

| screamer | 18:a15bfe7aaebd | 390 | |

| screamer | 18:a15bfe7aaebd | 391 | status = VL53L0X_read_word(dev, |

| screamer | 18:a15bfe7aaebd | 392 | VL53L0X_REG_ALGO_PART_TO_PART_RANGE_OFFSET_MM, |

| screamer | 18:a15bfe7aaebd | 393 | &range_offset_register); |

| screamer | 18:a15bfe7aaebd | 394 | |

| screamer | 18:a15bfe7aaebd | 395 | if (status == VL53L0X_ERROR_NONE) { |

| screamer | 18:a15bfe7aaebd | 396 | range_offset_register = (range_offset_register & 0x0fff); |

| screamer | 18:a15bfe7aaebd | 397 | |

| screamer | 18:a15bfe7aaebd | 398 | /* Apply 12 bit 2's compliment conversion */ |

| screamer | 18:a15bfe7aaebd | 399 | if (range_offset_register > c_max_offset) { |

| screamer | 18:a15bfe7aaebd | 400 | *p_offset_calibration_data_micro_meter = |

| screamer | 18:a15bfe7aaebd | 401 | (int16_t)(range_offset_register - c_offset_range) |

| screamer | 18:a15bfe7aaebd | 402 | * 250; |

| screamer | 18:a15bfe7aaebd | 403 | } else { |

| screamer | 18:a15bfe7aaebd | 404 | *p_offset_calibration_data_micro_meter = |

| screamer | 18:a15bfe7aaebd | 405 | (int16_t)range_offset_register * 250; |

| screamer | 18:a15bfe7aaebd | 406 | } |

| screamer | 18:a15bfe7aaebd | 407 | |

| screamer | 18:a15bfe7aaebd | 408 | } |

| screamer | 18:a15bfe7aaebd | 409 | |

| screamer | 18:a15bfe7aaebd | 410 | return status; |

| screamer | 18:a15bfe7aaebd | 411 | } |

| screamer | 18:a15bfe7aaebd | 412 | |

| screamer | 18:a15bfe7aaebd | 413 | VL53L0X_Error VL53L0X::VL53L0X_get_offset_calibration_data_micro_meter(VL53L0X_DEV dev, |

| screamer | 18:a15bfe7aaebd | 414 | int32_t *p_offset_calibration_data_micro_meter) |

| screamer | 18:a15bfe7aaebd | 415 | { |

| screamer | 18:a15bfe7aaebd | 416 | VL53L0X_Error status = VL53L0X_ERROR_NONE; |

| screamer | 18:a15bfe7aaebd | 417 | LOG_FUNCTION_START(""); |

| screamer | 18:a15bfe7aaebd | 418 | |

| screamer | 18:a15bfe7aaebd | 419 | status = wrapped_VL53L0X_get_offset_calibration_data_micro_meter(dev, |

| screamer | 18:a15bfe7aaebd | 420 | p_offset_calibration_data_micro_meter); |

| screamer | 18:a15bfe7aaebd | 421 | |

| screamer | 18:a15bfe7aaebd | 422 | LOG_FUNCTION_END(status); |

| screamer | 18:a15bfe7aaebd | 423 | return status; |

| screamer | 18:a15bfe7aaebd | 424 | } |

| screamer | 18:a15bfe7aaebd | 425 | |

| screamer | 18:a15bfe7aaebd | 426 | VL53L0X_Error VL53L0X::wrapped_VL53L0X_set_offset_calibration_data_micro_meter(VL53L0X_DEV dev, |

| screamer | 18:a15bfe7aaebd | 427 | int32_t offset_calibration_data_micro_meter) |

| screamer | 18:a15bfe7aaebd | 428 | { |

| screamer | 18:a15bfe7aaebd | 429 | VL53L0X_Error status = VL53L0X_ERROR_NONE; |

| screamer | 18:a15bfe7aaebd | 430 | int32_t c_max_offset_micro_meter = 511000; |

| screamer | 18:a15bfe7aaebd | 431 | int32_t c_min_offset_micro_meter = -512000; |

| screamer | 18:a15bfe7aaebd | 432 | int16_t c_offset_range = 4096; |

| screamer | 18:a15bfe7aaebd | 433 | uint32_t encoded_offset_val; |

| screamer | 18:a15bfe7aaebd | 434 | |

| screamer | 18:a15bfe7aaebd | 435 | LOG_FUNCTION_START(""); |

| screamer | 18:a15bfe7aaebd | 436 | |

| screamer | 18:a15bfe7aaebd | 437 | if (offset_calibration_data_micro_meter > c_max_offset_micro_meter) { |

| screamer | 18:a15bfe7aaebd | 438 | offset_calibration_data_micro_meter = c_max_offset_micro_meter; |

| screamer | 18:a15bfe7aaebd | 439 | } else { |

| screamer | 18:a15bfe7aaebd | 440 | if (offset_calibration_data_micro_meter < c_min_offset_micro_meter) { |

| screamer | 18:a15bfe7aaebd | 441 | offset_calibration_data_micro_meter = c_min_offset_micro_meter; |

| screamer | 18:a15bfe7aaebd | 442 | } |

| screamer | 18:a15bfe7aaebd | 443 | } |

| screamer | 18:a15bfe7aaebd | 444 | |

| screamer | 18:a15bfe7aaebd | 445 | /* The offset register is 10.2 format and units are mm |

| screamer | 18:a15bfe7aaebd | 446 | * therefore conversion is applied by a division of |

| screamer | 18:a15bfe7aaebd | 447 | * 250. |

| screamer | 18:a15bfe7aaebd | 448 | */ |

| screamer | 18:a15bfe7aaebd | 449 | if (offset_calibration_data_micro_meter >= 0) { |

| screamer | 18:a15bfe7aaebd | 450 | encoded_offset_val = |

| screamer | 18:a15bfe7aaebd | 451 | offset_calibration_data_micro_meter / 250; |

| screamer | 18:a15bfe7aaebd | 452 | } else { |

| screamer | 18:a15bfe7aaebd | 453 | encoded_offset_val = |

| screamer | 18:a15bfe7aaebd | 454 | c_offset_range + |

| screamer | 18:a15bfe7aaebd | 455 | offset_calibration_data_micro_meter / 250; |

| screamer | 18:a15bfe7aaebd | 456 | } |

| screamer | 18:a15bfe7aaebd | 457 | |

| screamer | 18:a15bfe7aaebd | 458 | status = VL53L0X_write_word(dev, |

| screamer | 18:a15bfe7aaebd | 459 | VL53L0X_REG_ALGO_PART_TO_PART_RANGE_OFFSET_MM, |

| screamer | 18:a15bfe7aaebd | 460 | encoded_offset_val); |

| screamer | 18:a15bfe7aaebd | 461 | |

| screamer | 18:a15bfe7aaebd | 462 | LOG_FUNCTION_END(status); |

| screamer | 18:a15bfe7aaebd | 463 | return status; |

| screamer | 18:a15bfe7aaebd | 464 | } |

| screamer | 18:a15bfe7aaebd | 465 | |

| screamer | 18:a15bfe7aaebd | 466 | VL53L0X_Error VL53L0X::VL53L0X_set_offset_calibration_data_micro_meter(VL53L0X_DEV dev, |

| screamer | 18:a15bfe7aaebd | 467 | int32_t offset_calibration_data_micro_meter) |

| screamer | 18:a15bfe7aaebd | 468 | { |

| screamer | 18:a15bfe7aaebd | 469 | VL53L0X_Error status = VL53L0X_ERROR_NONE; |

| screamer | 18:a15bfe7aaebd | 470 | LOG_FUNCTION_START(""); |

| screamer | 18:a15bfe7aaebd | 471 | |

| screamer | 18:a15bfe7aaebd | 472 | status = wrapped_VL53L0X_set_offset_calibration_data_micro_meter(dev, |

| screamer | 18:a15bfe7aaebd | 473 | offset_calibration_data_micro_meter); |

| screamer | 18:a15bfe7aaebd | 474 | |

| screamer | 18:a15bfe7aaebd | 475 | LOG_FUNCTION_END(status); |

| screamer | 18:a15bfe7aaebd | 476 | return status; |

| screamer | 18:a15bfe7aaebd | 477 | } |

| screamer | 18:a15bfe7aaebd | 478 | |

| screamer | 18:a15bfe7aaebd | 479 | VL53L0X_Error VL53L0X::VL53L0X_apply_offset_adjustment(VL53L0X_DEV dev) |

| screamer | 18:a15bfe7aaebd | 480 | { |

| screamer | 18:a15bfe7aaebd | 481 | VL53L0X_Error status = VL53L0X_ERROR_NONE; |

| screamer | 18:a15bfe7aaebd | 482 | int32_t corrected_offset_micro_meters; |

| screamer | 18:a15bfe7aaebd | 483 | int32_t current_offset_micro_meters; |

| screamer | 18:a15bfe7aaebd | 484 | |

| screamer | 18:a15bfe7aaebd | 485 | /* if we run on this function we can read all the NVM info |

| screamer | 18:a15bfe7aaebd | 486 | * used by the API */ |

| screamer | 18:a15bfe7aaebd | 487 | status = VL53L0X_get_info_from_device(dev, 7); |

| screamer | 18:a15bfe7aaebd | 488 | |

| screamer | 18:a15bfe7aaebd | 489 | /* Read back current device offset */ |

| screamer | 18:a15bfe7aaebd | 490 | if (status == VL53L0X_ERROR_NONE) { |

| screamer | 18:a15bfe7aaebd | 491 | status = VL53L0X_get_offset_calibration_data_micro_meter(dev, |

| screamer | 18:a15bfe7aaebd | 492 | ¤t_offset_micro_meters); |

| screamer | 18:a15bfe7aaebd | 493 | } |

| screamer | 18:a15bfe7aaebd | 494 | |

| screamer | 18:a15bfe7aaebd | 495 | /* Apply Offset Adjustment derived from 400mm measurements */ |

| screamer | 18:a15bfe7aaebd | 496 | if (status == VL53L0X_ERROR_NONE) { |

| screamer | 18:a15bfe7aaebd | 497 | |

| screamer | 18:a15bfe7aaebd | 498 | /* Store initial device offset */ |

| screamer | 18:a15bfe7aaebd | 499 | PALDevDataSet(dev, Part2PartOffsetNVMMicroMeter, |

| screamer | 18:a15bfe7aaebd | 500 | current_offset_micro_meters); |

| screamer | 18:a15bfe7aaebd | 501 | |

| screamer | 18:a15bfe7aaebd | 502 | corrected_offset_micro_meters = current_offset_micro_meters + |

| screamer | 18:a15bfe7aaebd | 503 | (int32_t)PALDevDataGet(dev, |

| screamer | 18:a15bfe7aaebd | 504 | Part2PartOffsetAdjustmentNVMMicroMeter); |

| screamer | 18:a15bfe7aaebd | 505 | |

| screamer | 18:a15bfe7aaebd | 506 | status = VL53L0X_set_offset_calibration_data_micro_meter(dev, |

| screamer | 18:a15bfe7aaebd | 507 | corrected_offset_micro_meters); |

| screamer | 18:a15bfe7aaebd | 508 | |

| screamer | 18:a15bfe7aaebd | 509 | /* store current, adjusted offset */ |

| screamer | 18:a15bfe7aaebd | 510 | if (status == VL53L0X_ERROR_NONE) { |

| screamer | 18:a15bfe7aaebd | 511 | VL53L0X_SETPARAMETERFIELD(dev, RangeOffsetMicroMeters, |

| screamer | 18:a15bfe7aaebd | 512 | corrected_offset_micro_meters); |

| screamer | 18:a15bfe7aaebd | 513 | } |

| screamer | 18:a15bfe7aaebd | 514 | } |

| screamer | 18:a15bfe7aaebd | 515 | |

| screamer | 18:a15bfe7aaebd | 516 | return status; |

| screamer | 18:a15bfe7aaebd | 517 | } |

| screamer | 18:a15bfe7aaebd | 518 | |

| screamer | 18:a15bfe7aaebd | 519 | VL53L0X_Error VL53L0X::VL53L0X_get_device_mode(VL53L0X_DEV dev, |

| screamer | 18:a15bfe7aaebd | 520 | VL53L0X_DeviceModes *p_device_mode) |

| screamer | 18:a15bfe7aaebd | 521 | { |

| screamer | 18:a15bfe7aaebd | 522 | VL53L0X_Error status = VL53L0X_ERROR_NONE; |

| screamer | 18:a15bfe7aaebd | 523 | LOG_FUNCTION_START(""); |

| screamer | 18:a15bfe7aaebd | 524 | |

| screamer | 18:a15bfe7aaebd | 525 | VL53L0X_GETPARAMETERFIELD(dev, DeviceMode, *p_device_mode); |

| screamer | 18:a15bfe7aaebd | 526 | |

| screamer | 18:a15bfe7aaebd | 527 | LOG_FUNCTION_END(status); |

| screamer | 18:a15bfe7aaebd | 528 | return status; |

| screamer | 18:a15bfe7aaebd | 529 | } |

| screamer | 18:a15bfe7aaebd | 530 | |

| screamer | 18:a15bfe7aaebd | 531 | VL53L0X_Error VL53L0X::VL53L0X_get_inter_measurement_period_milli_seconds(VL53L0X_DEV dev, |

| screamer | 18:a15bfe7aaebd | 532 | uint32_t *p_inter_measurement_period_milli_seconds) |

| screamer | 18:a15bfe7aaebd | 533 | { |

| screamer | 18:a15bfe7aaebd | 534 | VL53L0X_Error status = VL53L0X_ERROR_NONE; |

| screamer | 18:a15bfe7aaebd | 535 | uint16_t osc_calibrate_val; |

| screamer | 18:a15bfe7aaebd | 536 | uint32_t im_period_milli_seconds; |

| screamer | 18:a15bfe7aaebd | 537 | |

| screamer | 18:a15bfe7aaebd | 538 | LOG_FUNCTION_START(""); |

| screamer | 18:a15bfe7aaebd | 539 | |

| screamer | 18:a15bfe7aaebd | 540 | status = VL53L0X_read_word(dev, VL53L0X_REG_OSC_CALIBRATE_VAL, |

| screamer | 18:a15bfe7aaebd | 541 | &osc_calibrate_val); |

| screamer | 18:a15bfe7aaebd | 542 | |

| screamer | 18:a15bfe7aaebd | 543 | if (status == VL53L0X_ERROR_NONE) { |

| screamer | 18:a15bfe7aaebd | 544 | status = VL53L0X_read_dword(dev, |

| screamer | 18:a15bfe7aaebd | 545 | VL53L0X_REG_SYSTEM_INTERMEASUREMENT_PERIOD, |

| screamer | 18:a15bfe7aaebd | 546 | &im_period_milli_seconds); |

| screamer | 18:a15bfe7aaebd | 547 | } |

| screamer | 18:a15bfe7aaebd | 548 | |

| screamer | 18:a15bfe7aaebd | 549 | if (status == VL53L0X_ERROR_NONE) { |

| screamer | 18:a15bfe7aaebd | 550 | if (osc_calibrate_val != 0) { |

| screamer | 18:a15bfe7aaebd | 551 | *p_inter_measurement_period_milli_seconds = |

| screamer | 18:a15bfe7aaebd | 552 | im_period_milli_seconds / osc_calibrate_val; |

| screamer | 18:a15bfe7aaebd | 553 | } |

| screamer | 18:a15bfe7aaebd | 554 | VL53L0X_SETPARAMETERFIELD(dev, |

| screamer | 18:a15bfe7aaebd | 555 | InterMeasurementPeriodMilliSeconds, |

| screamer | 18:a15bfe7aaebd | 556 | *p_inter_measurement_period_milli_seconds); |

| screamer | 18:a15bfe7aaebd | 557 | } |

| screamer | 18:a15bfe7aaebd | 558 | |

| screamer | 18:a15bfe7aaebd | 559 | LOG_FUNCTION_END(status); |

| screamer | 18:a15bfe7aaebd | 560 | return status; |

| screamer | 18:a15bfe7aaebd | 561 | } |

| screamer | 18:a15bfe7aaebd | 562 | |

| screamer | 18:a15bfe7aaebd | 563 | VL53L0X_Error VL53L0X::VL53L0X_get_x_talk_compensation_rate_mega_cps(VL53L0X_DEV dev, |

| screamer | 18:a15bfe7aaebd | 564 | FixPoint1616_t *p_xtalk_compensation_rate_mega_cps) |

| screamer | 18:a15bfe7aaebd | 565 | { |

| screamer | 18:a15bfe7aaebd | 566 | VL53L0X_Error status = VL53L0X_ERROR_NONE; |

| screamer | 18:a15bfe7aaebd | 567 | uint16_t value; |

| screamer | 18:a15bfe7aaebd | 568 | FixPoint1616_t temp_fix1616; |

| screamer | 18:a15bfe7aaebd | 569 | |

| screamer | 18:a15bfe7aaebd | 570 | LOG_FUNCTION_START(""); |

| screamer | 18:a15bfe7aaebd | 571 | |

| screamer | 18:a15bfe7aaebd | 572 | status = VL53L0X_read_word(dev, |

| screamer | 18:a15bfe7aaebd | 573 | VL53L0X_REG_CROSSTALK_COMPENSATION_PEAK_RATE_MCPS, (uint16_t *)&value); |

| screamer | 18:a15bfe7aaebd | 574 | if (status == VL53L0X_ERROR_NONE) { |

| screamer | 18:a15bfe7aaebd | 575 | if (value == 0) { |

| screamer | 18:a15bfe7aaebd | 576 | /* the Xtalk is disabled return value from memory */ |

| screamer | 18:a15bfe7aaebd | 577 | VL53L0X_GETPARAMETERFIELD(dev, |

| screamer | 18:a15bfe7aaebd | 578 | XTalkCompensationRateMegaCps, temp_fix1616); |

| screamer | 18:a15bfe7aaebd | 579 | *p_xtalk_compensation_rate_mega_cps = temp_fix1616; |

| screamer | 18:a15bfe7aaebd | 580 | VL53L0X_SETPARAMETERFIELD(dev, XTalkCompensationEnable, |

| screamer | 18:a15bfe7aaebd | 581 | 0); |

| screamer | 18:a15bfe7aaebd | 582 | } else { |

| screamer | 18:a15bfe7aaebd | 583 | temp_fix1616 = VL53L0X_FIXPOINT313TOFIXPOINT1616(value); |

| screamer | 18:a15bfe7aaebd | 584 | *p_xtalk_compensation_rate_mega_cps = temp_fix1616; |

| screamer | 18:a15bfe7aaebd | 585 | VL53L0X_SETPARAMETERFIELD(dev, |

| screamer | 18:a15bfe7aaebd | 586 | XTalkCompensationRateMegaCps, temp_fix1616); |

| screamer | 18:a15bfe7aaebd | 587 | VL53L0X_SETPARAMETERFIELD(dev, XTalkCompensationEnable, |

| screamer | 18:a15bfe7aaebd | 588 | 1); |

| screamer | 18:a15bfe7aaebd | 589 | } |

| screamer | 18:a15bfe7aaebd | 590 | } |

| screamer | 18:a15bfe7aaebd | 591 | |

| screamer | 18:a15bfe7aaebd | 592 | LOG_FUNCTION_END(status); |

| screamer | 18:a15bfe7aaebd | 593 | return status; |

| screamer | 18:a15bfe7aaebd | 594 | } |

| screamer | 18:a15bfe7aaebd | 595 | |

| screamer | 18:a15bfe7aaebd | 596 | VL53L0X_Error VL53L0X::VL53L0X_get_limit_check_value(VL53L0X_DEV dev, uint16_t limit_check_id, |

| screamer | 18:a15bfe7aaebd | 597 | FixPoint1616_t *p_limit_check_value) |

| screamer | 18:a15bfe7aaebd | 598 | { |

| screamer | 18:a15bfe7aaebd | 599 | VL53L0X_Error status = VL53L0X_ERROR_NONE; |

| screamer | 18:a15bfe7aaebd | 600 | uint8_t enable_zero_value = 0; |

| screamer | 18:a15bfe7aaebd | 601 | uint16_t temp16; |

| screamer | 18:a15bfe7aaebd | 602 | FixPoint1616_t temp_fix1616; |

| screamer | 18:a15bfe7aaebd | 603 | |

| screamer | 18:a15bfe7aaebd | 604 | LOG_FUNCTION_START(""); |

| screamer | 18:a15bfe7aaebd | 605 | |

| screamer | 18:a15bfe7aaebd | 606 | switch (limit_check_id) { |

| screamer | 18:a15bfe7aaebd | 607 | |

| screamer | 18:a15bfe7aaebd | 608 | case VL53L0X_CHECKENABLE_SIGMA_FINAL_RANGE: |

| screamer | 18:a15bfe7aaebd | 609 | /* internal computation: */ |

| screamer | 18:a15bfe7aaebd | 610 | VL53L0X_GETARRAYPARAMETERFIELD(dev, LimitChecksValue, |

| screamer | 18:a15bfe7aaebd | 611 | VL53L0X_CHECKENABLE_SIGMA_FINAL_RANGE, temp_fix1616); |

| screamer | 18:a15bfe7aaebd | 612 | enable_zero_value = 0; |

| screamer | 18:a15bfe7aaebd | 613 | break; |

| screamer | 18:a15bfe7aaebd | 614 | |

| screamer | 18:a15bfe7aaebd | 615 | case VL53L0X_CHECKENABLE_SIGNAL_RATE_FINAL_RANGE: |

| screamer | 18:a15bfe7aaebd | 616 | status = VL53L0X_read_word(dev, |

| screamer | 18:a15bfe7aaebd | 617 | VL53L0X_REG_FINAL_RANGE_CONFIG_MIN_COUNT_RATE_RTN_LIMIT, |

| screamer | 18:a15bfe7aaebd | 618 | &temp16); |

| screamer | 18:a15bfe7aaebd | 619 | if (status == VL53L0X_ERROR_NONE) { |

| screamer | 18:a15bfe7aaebd | 620 | temp_fix1616 = VL53L0X_FIXPOINT97TOFIXPOINT1616(temp16); |

| screamer | 18:a15bfe7aaebd | 621 | } |

| screamer | 18:a15bfe7aaebd | 622 | |

| screamer | 18:a15bfe7aaebd | 623 | |

| screamer | 18:a15bfe7aaebd | 624 | enable_zero_value = 1; |

| screamer | 18:a15bfe7aaebd | 625 | break; |

| screamer | 18:a15bfe7aaebd | 626 | |

| screamer | 18:a15bfe7aaebd | 627 | case VL53L0X_CHECKENABLE_SIGNAL_REF_CLIP: |

| screamer | 18:a15bfe7aaebd | 628 | /* internal computation: */ |

| screamer | 18:a15bfe7aaebd | 629 | VL53L0X_GETARRAYPARAMETERFIELD(dev, LimitChecksValue, |

| screamer | 18:a15bfe7aaebd | 630 | VL53L0X_CHECKENABLE_SIGNAL_REF_CLIP, temp_fix1616); |

| screamer | 18:a15bfe7aaebd | 631 | enable_zero_value = 0; |

| screamer | 18:a15bfe7aaebd | 632 | break; |

| screamer | 18:a15bfe7aaebd | 633 | |

| screamer | 18:a15bfe7aaebd | 634 | case VL53L0X_CHECKENABLE_RANGE_IGNORE_THRESHOLD: |

| screamer | 18:a15bfe7aaebd | 635 | /* internal computation: */ |

| screamer | 18:a15bfe7aaebd | 636 | VL53L0X_GETARRAYPARAMETERFIELD(dev, LimitChecksValue, |

| screamer | 18:a15bfe7aaebd | 637 | VL53L0X_CHECKENABLE_RANGE_IGNORE_THRESHOLD, temp_fix1616); |

| screamer | 18:a15bfe7aaebd | 638 | enable_zero_value = 0; |

| screamer | 18:a15bfe7aaebd | 639 | break; |

| screamer | 18:a15bfe7aaebd | 640 | |

| screamer | 18:a15bfe7aaebd | 641 | case VL53L0X_CHECKENABLE_SIGNAL_RATE_MSRC: |

| screamer | 18:a15bfe7aaebd | 642 | case VL53L0X_CHECKENABLE_SIGNAL_RATE_PRE_RANGE: |

| screamer | 18:a15bfe7aaebd | 643 | status = VL53L0X_read_word(dev, |

| screamer | 18:a15bfe7aaebd | 644 | VL53L0X_REG_PRE_RANGE_MIN_COUNT_RATE_RTN_LIMIT, |

| screamer | 18:a15bfe7aaebd | 645 | &temp16); |

| screamer | 18:a15bfe7aaebd | 646 | if (status == VL53L0X_ERROR_NONE) { |

| screamer | 18:a15bfe7aaebd | 647 | temp_fix1616 = VL53L0X_FIXPOINT97TOFIXPOINT1616(temp16); |

| screamer | 18:a15bfe7aaebd | 648 | } |

| screamer | 18:a15bfe7aaebd | 649 | |

| screamer | 18:a15bfe7aaebd | 650 | |

| screamer | 18:a15bfe7aaebd | 651 | enable_zero_value = 0; |

| screamer | 18:a15bfe7aaebd | 652 | break; |

| screamer | 18:a15bfe7aaebd | 653 | |

| screamer | 18:a15bfe7aaebd | 654 | default: |

| screamer | 18:a15bfe7aaebd | 655 | status = VL53L0X_ERROR_INVALID_PARAMS; |

| screamer | 18:a15bfe7aaebd | 656 | |

| screamer | 18:a15bfe7aaebd | 657 | } |

| screamer | 18:a15bfe7aaebd | 658 | |

| screamer | 18:a15bfe7aaebd | 659 | if (status == VL53L0X_ERROR_NONE) { |

| screamer | 18:a15bfe7aaebd | 660 | |

| screamer | 18:a15bfe7aaebd | 661 | if (enable_zero_value == 1) { |

| screamer | 18:a15bfe7aaebd | 662 | |

| screamer | 18:a15bfe7aaebd | 663 | if (temp_fix1616 == 0) { |

| screamer | 18:a15bfe7aaebd | 664 | /* disabled: return value from memory */ |

| screamer | 18:a15bfe7aaebd | 665 | VL53L0X_GETARRAYPARAMETERFIELD(dev, |

| screamer | 18:a15bfe7aaebd | 666 | LimitChecksValue, limit_check_id, |

| screamer | 18:a15bfe7aaebd | 667 | temp_fix1616); |

| screamer | 18:a15bfe7aaebd | 668 | *p_limit_check_value = temp_fix1616; |

| screamer | 18:a15bfe7aaebd | 669 | VL53L0X_SETARRAYPARAMETERFIELD(dev, |

| screamer | 18:a15bfe7aaebd | 670 | LimitChecksEnable, limit_check_id, 0); |

| screamer | 18:a15bfe7aaebd | 671 | } else { |

| screamer | 18:a15bfe7aaebd | 672 | *p_limit_check_value = temp_fix1616; |

| screamer | 18:a15bfe7aaebd | 673 | VL53L0X_SETARRAYPARAMETERFIELD(dev, |

| screamer | 18:a15bfe7aaebd | 674 | LimitChecksValue, limit_check_id, |

| screamer | 18:a15bfe7aaebd | 675 | temp_fix1616); |

| screamer | 18:a15bfe7aaebd | 676 | VL53L0X_SETARRAYPARAMETERFIELD(dev, |

| screamer | 18:a15bfe7aaebd | 677 | LimitChecksEnable, limit_check_id, 1); |

| screamer | 18:a15bfe7aaebd | 678 | } |

| screamer | 18:a15bfe7aaebd | 679 | } else { |

| screamer | 18:a15bfe7aaebd | 680 | *p_limit_check_value = temp_fix1616; |

| screamer | 18:a15bfe7aaebd | 681 | } |

| screamer | 18:a15bfe7aaebd | 682 | } |

| screamer | 18:a15bfe7aaebd | 683 | |

| screamer | 18:a15bfe7aaebd | 684 | LOG_FUNCTION_END(status); |

| screamer | 18:a15bfe7aaebd | 685 | return status; |

| screamer | 18:a15bfe7aaebd | 686 | |

| screamer | 18:a15bfe7aaebd | 687 | } |

| screamer | 18:a15bfe7aaebd | 688 | |

| screamer | 18:a15bfe7aaebd | 689 | VL53L0X_Error VL53L0X::VL53L0X_get_limit_check_enable(VL53L0X_DEV dev, uint16_t limit_check_id, |

| screamer | 18:a15bfe7aaebd | 690 | uint8_t *p_limit_check_enable) |

| screamer | 18:a15bfe7aaebd | 691 | { |

| screamer | 18:a15bfe7aaebd | 692 | VL53L0X_Error status = VL53L0X_ERROR_NONE; |

| screamer | 18:a15bfe7aaebd | 693 | uint8_t temp8; |

| screamer | 18:a15bfe7aaebd | 694 | |

| screamer | 18:a15bfe7aaebd | 695 | LOG_FUNCTION_START(""); |

| screamer | 18:a15bfe7aaebd | 696 | |

| screamer | 18:a15bfe7aaebd | 697 | if (limit_check_id >= VL53L0X_CHECKENABLE_NUMBER_OF_CHECKS) { |

| screamer | 18:a15bfe7aaebd | 698 | status = VL53L0X_ERROR_INVALID_PARAMS; |

| screamer | 18:a15bfe7aaebd | 699 | *p_limit_check_enable = 0; |

| screamer | 18:a15bfe7aaebd | 700 | } else { |

| screamer | 18:a15bfe7aaebd | 701 | VL53L0X_GETARRAYPARAMETERFIELD(dev, LimitChecksEnable, |

| screamer | 18:a15bfe7aaebd | 702 | limit_check_id, temp8); |

| screamer | 18:a15bfe7aaebd | 703 | *p_limit_check_enable = temp8; |

| screamer | 18:a15bfe7aaebd | 704 | } |

| screamer | 18:a15bfe7aaebd | 705 | |

| screamer | 18:a15bfe7aaebd | 706 | LOG_FUNCTION_END(status); |

| screamer | 18:a15bfe7aaebd | 707 | return status; |

| screamer | 18:a15bfe7aaebd | 708 | } |

| screamer | 18:a15bfe7aaebd | 709 | |

| screamer | 18:a15bfe7aaebd | 710 | VL53L0X_Error VL53L0X::VL53L0X_get_wrap_around_check_enable(VL53L0X_DEV dev, |

| screamer | 18:a15bfe7aaebd | 711 | uint8_t *p_wrap_around_check_enable) |

| screamer | 18:a15bfe7aaebd | 712 | { |

| screamer | 18:a15bfe7aaebd | 713 | VL53L0X_Error status = VL53L0X_ERROR_NONE; |

| screamer | 18:a15bfe7aaebd | 714 | uint8_t data; |

| screamer | 18:a15bfe7aaebd | 715 | |

| screamer | 18:a15bfe7aaebd | 716 | LOG_FUNCTION_START(""); |

| screamer | 18:a15bfe7aaebd | 717 | |

| screamer | 18:a15bfe7aaebd | 718 | status = VL53L0X_read_byte(dev, VL53L0X_REG_SYSTEM_SEQUENCE_CONFIG, &data); |

| screamer | 18:a15bfe7aaebd | 719 | if (status == VL53L0X_ERROR_NONE) { |

| screamer | 18:a15bfe7aaebd | 720 | PALDevDataSet(dev, SequenceConfig, data); |

| screamer | 18:a15bfe7aaebd | 721 | if (data & (0x01 << 7)) { |

| screamer | 18:a15bfe7aaebd | 722 | *p_wrap_around_check_enable = 0x01; |

| screamer | 18:a15bfe7aaebd | 723 | } else { |

| screamer | 18:a15bfe7aaebd | 724 | *p_wrap_around_check_enable = 0x00; |

| screamer | 18:a15bfe7aaebd | 725 | } |

| screamer | 18:a15bfe7aaebd | 726 | } |

| screamer | 18:a15bfe7aaebd | 727 | if (status == VL53L0X_ERROR_NONE) { |

| screamer | 18:a15bfe7aaebd | 728 | VL53L0X_SETPARAMETERFIELD(dev, WrapAroundCheckEnable, |

| screamer | 18:a15bfe7aaebd | 729 | *p_wrap_around_check_enable); |

| screamer | 18:a15bfe7aaebd | 730 | } |

| screamer | 18:a15bfe7aaebd | 731 | |

| screamer | 18:a15bfe7aaebd | 732 | LOG_FUNCTION_END(status); |

| screamer | 18:a15bfe7aaebd | 733 | return status; |

| screamer | 18:a15bfe7aaebd | 734 | } |

| screamer | 18:a15bfe7aaebd | 735 | |

| screamer | 18:a15bfe7aaebd | 736 | VL53L0X_Error VL53L0X::sequence_step_enabled(VL53L0X_DEV dev, |

| screamer | 18:a15bfe7aaebd | 737 | VL53L0X_SequenceStepId sequence_step_id, uint8_t sequence_config, |

| screamer | 18:a15bfe7aaebd | 738 | uint8_t *p_sequence_step_enabled) |

| screamer | 18:a15bfe7aaebd | 739 | { |

| screamer | 18:a15bfe7aaebd | 740 | VL53L0X_Error Status = VL53L0X_ERROR_NONE; |

| screamer | 18:a15bfe7aaebd | 741 | *p_sequence_step_enabled = 0; |

| screamer | 18:a15bfe7aaebd | 742 | LOG_FUNCTION_START(""); |

| screamer | 18:a15bfe7aaebd | 743 | |

| screamer | 18:a15bfe7aaebd | 744 | switch (sequence_step_id) { |

| screamer | 18:a15bfe7aaebd | 745 | case VL53L0X_SEQUENCESTEP_TCC: |

| screamer | 18:a15bfe7aaebd | 746 | *p_sequence_step_enabled = (sequence_config & 0x10) >> 4; |

| screamer | 18:a15bfe7aaebd | 747 | break; |

| screamer | 18:a15bfe7aaebd | 748 | case VL53L0X_SEQUENCESTEP_DSS: |

| screamer | 18:a15bfe7aaebd | 749 | *p_sequence_step_enabled = (sequence_config & 0x08) >> 3; |

| screamer | 18:a15bfe7aaebd | 750 | break; |

| screamer | 18:a15bfe7aaebd | 751 | case VL53L0X_SEQUENCESTEP_MSRC: |

| screamer | 18:a15bfe7aaebd | 752 | *p_sequence_step_enabled = (sequence_config & 0x04) >> 2; |

| screamer | 18:a15bfe7aaebd | 753 | break; |

| screamer | 18:a15bfe7aaebd | 754 | case VL53L0X_SEQUENCESTEP_PRE_RANGE: |

| screamer | 18:a15bfe7aaebd | 755 | *p_sequence_step_enabled = (sequence_config & 0x40) >> 6; |

| screamer | 18:a15bfe7aaebd | 756 | break; |

| screamer | 18:a15bfe7aaebd | 757 | case VL53L0X_SEQUENCESTEP_FINAL_RANGE: |

| screamer | 18:a15bfe7aaebd | 758 | *p_sequence_step_enabled = (sequence_config & 0x80) >> 7; |

| screamer | 18:a15bfe7aaebd | 759 | break; |

| screamer | 18:a15bfe7aaebd | 760 | default: |

| screamer | 18:a15bfe7aaebd | 761 | Status = VL53L0X_ERROR_INVALID_PARAMS; |

| screamer | 18:a15bfe7aaebd | 762 | } |

| screamer | 18:a15bfe7aaebd | 763 | |

| screamer | 18:a15bfe7aaebd | 764 | LOG_FUNCTION_END(status); |

| screamer | 18:a15bfe7aaebd | 765 | return Status; |

| screamer | 18:a15bfe7aaebd | 766 | } |

| screamer | 18:a15bfe7aaebd | 767 | |

| screamer | 18:a15bfe7aaebd | 768 | VL53L0X_Error VL53L0X::VL53L0X_get_sequence_step_enables(VL53L0X_DEV dev, |

| screamer | 18:a15bfe7aaebd | 769 | VL53L0X_SchedulerSequenceSteps_t *p_scheduler_sequence_steps) |

| screamer | 18:a15bfe7aaebd | 770 | { |

| screamer | 18:a15bfe7aaebd | 771 | VL53L0X_Error status = VL53L0X_ERROR_NONE; |

| screamer | 18:a15bfe7aaebd | 772 | uint8_t sequence_config = 0; |

| screamer | 18:a15bfe7aaebd | 773 | LOG_FUNCTION_START(""); |

| screamer | 18:a15bfe7aaebd | 774 | |

| screamer | 18:a15bfe7aaebd | 775 | status = VL53L0X_read_byte(dev, VL53L0X_REG_SYSTEM_SEQUENCE_CONFIG, |

| screamer | 18:a15bfe7aaebd | 776 | &sequence_config); |

| screamer | 18:a15bfe7aaebd | 777 | |

| screamer | 18:a15bfe7aaebd | 778 | if (status == VL53L0X_ERROR_NONE) { |

| screamer | 18:a15bfe7aaebd | 779 | status = sequence_step_enabled(dev, |

| screamer | 18:a15bfe7aaebd | 780 | VL53L0X_SEQUENCESTEP_TCC, sequence_config, |

| screamer | 18:a15bfe7aaebd | 781 | &p_scheduler_sequence_steps->TccOn); |

| screamer | 18:a15bfe7aaebd | 782 | } |

| screamer | 18:a15bfe7aaebd | 783 | if (status == VL53L0X_ERROR_NONE) { |

| screamer | 18:a15bfe7aaebd | 784 | status = sequence_step_enabled(dev, |

| screamer | 18:a15bfe7aaebd | 785 | VL53L0X_SEQUENCESTEP_DSS, sequence_config, |

| screamer | 18:a15bfe7aaebd | 786 | &p_scheduler_sequence_steps->DssOn); |

| screamer | 18:a15bfe7aaebd | 787 | } |

| screamer | 18:a15bfe7aaebd | 788 | if (status == VL53L0X_ERROR_NONE) { |

| screamer | 18:a15bfe7aaebd | 789 | status = sequence_step_enabled(dev, |

| screamer | 18:a15bfe7aaebd | 790 | VL53L0X_SEQUENCESTEP_MSRC, sequence_config, |

| screamer | 18:a15bfe7aaebd | 791 | &p_scheduler_sequence_steps->MsrcOn); |

| screamer | 18:a15bfe7aaebd | 792 | } |

| screamer | 18:a15bfe7aaebd | 793 | if (status == VL53L0X_ERROR_NONE) { |

| screamer | 18:a15bfe7aaebd | 794 | status = sequence_step_enabled(dev, |

| screamer | 18:a15bfe7aaebd | 795 | VL53L0X_SEQUENCESTEP_PRE_RANGE, sequence_config, |

| screamer | 18:a15bfe7aaebd | 796 | &p_scheduler_sequence_steps->PreRangeOn); |

| screamer | 18:a15bfe7aaebd | 797 | } |

| screamer | 18:a15bfe7aaebd | 798 | if (status == VL53L0X_ERROR_NONE) { |

| screamer | 18:a15bfe7aaebd | 799 | status = sequence_step_enabled(dev, |

| screamer | 18:a15bfe7aaebd | 800 | VL53L0X_SEQUENCESTEP_FINAL_RANGE, sequence_config, |

| screamer | 18:a15bfe7aaebd | 801 | &p_scheduler_sequence_steps->FinalRangeOn); |

| screamer | 18:a15bfe7aaebd | 802 | } |

| screamer | 18:a15bfe7aaebd | 803 | |

| screamer | 18:a15bfe7aaebd | 804 | LOG_FUNCTION_END(status); |

| screamer | 18:a15bfe7aaebd | 805 | return status; |

| screamer | 18:a15bfe7aaebd | 806 | } |

| screamer | 18:a15bfe7aaebd | 807 | |

| screamer | 18:a15bfe7aaebd | 808 | uint8_t VL53L0X::VL53L0X_decode_vcsel_period(uint8_t vcsel_period_reg) |

| screamer | 18:a15bfe7aaebd | 809 | { |

| screamer | 18:a15bfe7aaebd | 810 | /*! |

| screamer | 18:a15bfe7aaebd | 811 | * Converts the encoded VCSEL period register value into the real |

| screamer | 18:a15bfe7aaebd | 812 | * period in PLL clocks |

| screamer | 18:a15bfe7aaebd | 813 | */ |

| screamer | 18:a15bfe7aaebd | 814 | |

| screamer | 18:a15bfe7aaebd | 815 | uint8_t vcsel_period_pclks = 0; |

| screamer | 18:a15bfe7aaebd | 816 | |

| screamer | 18:a15bfe7aaebd | 817 | vcsel_period_pclks = (vcsel_period_reg + 1) << 1; |

| screamer | 18:a15bfe7aaebd | 818 | |

| screamer | 18:a15bfe7aaebd | 819 | return vcsel_period_pclks; |

| screamer | 18:a15bfe7aaebd | 820 | } |

| screamer | 18:a15bfe7aaebd | 821 | |

| screamer | 18:a15bfe7aaebd | 822 | uint8_t VL53L0X::lv53l0x_encode_vcsel_period(uint8_t vcsel_period_pclks) |

| screamer | 18:a15bfe7aaebd | 823 | { |

| screamer | 18:a15bfe7aaebd | 824 | /*! |

| screamer | 18:a15bfe7aaebd | 825 | * Converts the encoded VCSEL period register value into the real period |

| screamer | 18:a15bfe7aaebd | 826 | * in PLL clocks |

| screamer | 18:a15bfe7aaebd | 827 | */ |

| screamer | 18:a15bfe7aaebd | 828 | |

| screamer | 18:a15bfe7aaebd | 829 | uint8_t vcsel_period_reg = 0; |

| screamer | 18:a15bfe7aaebd | 830 | |

| screamer | 18:a15bfe7aaebd | 831 | vcsel_period_reg = (vcsel_period_pclks >> 1) - 1; |

| screamer | 18:a15bfe7aaebd | 832 | |

| screamer | 18:a15bfe7aaebd | 833 | return vcsel_period_reg; |

| screamer | 18:a15bfe7aaebd | 834 | } |

| screamer | 18:a15bfe7aaebd | 835 | |

| screamer | 18:a15bfe7aaebd | 836 | |

| screamer | 18:a15bfe7aaebd | 837 | VL53L0X_Error VL53L0X::wrapped_VL53L0X_set_vcsel_pulse_period(VL53L0X_DEV dev, |

| screamer | 18:a15bfe7aaebd | 838 | VL53L0X_VcselPeriod vcsel_period_type, uint8_t vcsel_pulse_period_pclk) |

| screamer | 18:a15bfe7aaebd | 839 | { |

| screamer | 18:a15bfe7aaebd | 840 | VL53L0X_Error status = VL53L0X_ERROR_NONE; |

| screamer | 18:a15bfe7aaebd | 841 | uint8_t vcsel_period_reg; |

| screamer | 18:a15bfe7aaebd | 842 | uint8_t min_pre_vcsel_period_pclk = 12; |

| screamer | 18:a15bfe7aaebd | 843 | uint8_t max_pre_vcsel_period_pclk = 18; |

| screamer | 18:a15bfe7aaebd | 844 | uint8_t min_final_vcsel_period_pclk = 8; |

| screamer | 18:a15bfe7aaebd | 845 | uint8_t max_final_vcsel_period_pclk = 14; |

| screamer | 18:a15bfe7aaebd | 846 | uint32_t measurement_timing_budget_micro_seconds; |

| screamer | 18:a15bfe7aaebd | 847 | uint32_t final_range_timeout_micro_seconds; |

| screamer | 18:a15bfe7aaebd | 848 | uint32_t pre_range_timeout_micro_seconds; |

| screamer | 18:a15bfe7aaebd | 849 | uint32_t msrc_timeout_micro_seconds; |

| screamer | 18:a15bfe7aaebd | 850 | uint8_t phase_cal_int = 0; |

| screamer | 18:a15bfe7aaebd | 851 | |

| screamer | 18:a15bfe7aaebd | 852 | /* Check if valid clock period requested */ |

| screamer | 18:a15bfe7aaebd | 853 | |

| screamer | 18:a15bfe7aaebd | 854 | if ((vcsel_pulse_period_pclk % 2) != 0) { |

| screamer | 18:a15bfe7aaebd | 855 | /* Value must be an even number */ |

| screamer | 18:a15bfe7aaebd | 856 | status = VL53L0X_ERROR_INVALID_PARAMS; |

| screamer | 18:a15bfe7aaebd | 857 | } else if (vcsel_period_type == VL53L0X_VCSEL_PERIOD_PRE_RANGE && |

| screamer | 18:a15bfe7aaebd | 858 | (vcsel_pulse_period_pclk < min_pre_vcsel_period_pclk || |

| screamer | 18:a15bfe7aaebd | 859 | vcsel_pulse_period_pclk > max_pre_vcsel_period_pclk)) { |

| screamer | 18:a15bfe7aaebd | 860 | status = VL53L0X_ERROR_INVALID_PARAMS; |

| screamer | 18:a15bfe7aaebd | 861 | } else if (vcsel_period_type == VL53L0X_VCSEL_PERIOD_FINAL_RANGE && |

| screamer | 18:a15bfe7aaebd | 862 | (vcsel_pulse_period_pclk < min_final_vcsel_period_pclk || |

| screamer | 18:a15bfe7aaebd | 863 | vcsel_pulse_period_pclk > max_final_vcsel_period_pclk)) { |

| screamer | 18:a15bfe7aaebd | 864 | |

| screamer | 18:a15bfe7aaebd | 865 | status = VL53L0X_ERROR_INVALID_PARAMS; |

| screamer | 18:a15bfe7aaebd | 866 | } |

| screamer | 18:a15bfe7aaebd | 867 | |

| screamer | 18:a15bfe7aaebd | 868 | /* Apply specific settings for the requested clock period */ |

| screamer | 18:a15bfe7aaebd | 869 | |

| screamer | 18:a15bfe7aaebd | 870 | if (status != VL53L0X_ERROR_NONE) { |

| screamer | 18:a15bfe7aaebd | 871 | return status; |

| screamer | 18:a15bfe7aaebd | 872 | } |

| screamer | 18:a15bfe7aaebd | 873 | |

| screamer | 18:a15bfe7aaebd | 874 | |

| screamer | 18:a15bfe7aaebd | 875 | if (vcsel_period_type == VL53L0X_VCSEL_PERIOD_PRE_RANGE) { |

| screamer | 18:a15bfe7aaebd | 876 | |

| screamer | 18:a15bfe7aaebd | 877 | /* Set phase check limits */ |

| screamer | 18:a15bfe7aaebd | 878 | if (vcsel_pulse_period_pclk == 12) { |

| screamer | 18:a15bfe7aaebd | 879 | |

| screamer | 18:a15bfe7aaebd | 880 | status = VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 881 | VL53L0X_REG_PRE_RANGE_CONFIG_VALID_PHASE_HIGH, |

| screamer | 18:a15bfe7aaebd | 882 | 0x18); |

| screamer | 18:a15bfe7aaebd | 883 | status = VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 884 | VL53L0X_REG_PRE_RANGE_CONFIG_VALID_PHASE_LOW, |

| screamer | 18:a15bfe7aaebd | 885 | 0x08); |

| screamer | 18:a15bfe7aaebd | 886 | } else if (vcsel_pulse_period_pclk == 14) { |

| screamer | 18:a15bfe7aaebd | 887 | |

| screamer | 18:a15bfe7aaebd | 888 | status = VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 889 | VL53L0X_REG_PRE_RANGE_CONFIG_VALID_PHASE_HIGH, |

| screamer | 18:a15bfe7aaebd | 890 | 0x30); |

| screamer | 18:a15bfe7aaebd | 891 | status = VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 892 | VL53L0X_REG_PRE_RANGE_CONFIG_VALID_PHASE_LOW, |

| screamer | 18:a15bfe7aaebd | 893 | 0x08); |

| screamer | 18:a15bfe7aaebd | 894 | } else if (vcsel_pulse_period_pclk == 16) { |

| screamer | 18:a15bfe7aaebd | 895 | |

| screamer | 18:a15bfe7aaebd | 896 | status = VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 897 | VL53L0X_REG_PRE_RANGE_CONFIG_VALID_PHASE_HIGH, |

| screamer | 18:a15bfe7aaebd | 898 | 0x40); |

| screamer | 18:a15bfe7aaebd | 899 | status = VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 900 | VL53L0X_REG_PRE_RANGE_CONFIG_VALID_PHASE_LOW, |

| screamer | 18:a15bfe7aaebd | 901 | 0x08); |

| screamer | 18:a15bfe7aaebd | 902 | } else if (vcsel_pulse_period_pclk == 18) { |

| screamer | 18:a15bfe7aaebd | 903 | |

| screamer | 18:a15bfe7aaebd | 904 | status = VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 905 | VL53L0X_REG_PRE_RANGE_CONFIG_VALID_PHASE_HIGH, |

| screamer | 18:a15bfe7aaebd | 906 | 0x50); |

| screamer | 18:a15bfe7aaebd | 907 | status = VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 908 | VL53L0X_REG_PRE_RANGE_CONFIG_VALID_PHASE_LOW, |

| screamer | 18:a15bfe7aaebd | 909 | 0x08); |

| screamer | 18:a15bfe7aaebd | 910 | } |

| screamer | 18:a15bfe7aaebd | 911 | } else if (vcsel_period_type == VL53L0X_VCSEL_PERIOD_FINAL_RANGE) { |

| screamer | 18:a15bfe7aaebd | 912 | |

| screamer | 18:a15bfe7aaebd | 913 | if (vcsel_pulse_period_pclk == 8) { |

| screamer | 18:a15bfe7aaebd | 914 | |

| screamer | 18:a15bfe7aaebd | 915 | status = VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 916 | VL53L0X_REG_FINAL_RANGE_CONFIG_VALID_PHASE_HIGH, |

| screamer | 18:a15bfe7aaebd | 917 | 0x10); |

| screamer | 18:a15bfe7aaebd | 918 | status = VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 919 | VL53L0X_REG_FINAL_RANGE_CONFIG_VALID_PHASE_LOW, |

| screamer | 18:a15bfe7aaebd | 920 | 0x08); |

| screamer | 18:a15bfe7aaebd | 921 | |

| screamer | 18:a15bfe7aaebd | 922 | status |= VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 923 | VL53L0X_REG_GLOBAL_CONFIG_VCSEL_WIDTH, 0x02); |

| screamer | 18:a15bfe7aaebd | 924 | status |= VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 925 | VL53L0X_REG_ALGO_PHASECAL_CONFIG_TIMEOUT, 0x0C); |

| screamer | 18:a15bfe7aaebd | 926 | |

| screamer | 18:a15bfe7aaebd | 927 | status |= VL53L0X_write_byte(dev, 0xff, 0x01); |

| screamer | 18:a15bfe7aaebd | 928 | status |= VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 929 | VL53L0X_REG_ALGO_PHASECAL_LIM, |

| screamer | 18:a15bfe7aaebd | 930 | 0x30); |

| screamer | 18:a15bfe7aaebd | 931 | status |= VL53L0X_write_byte(dev, 0xff, 0x00); |

| screamer | 18:a15bfe7aaebd | 932 | } else if (vcsel_pulse_period_pclk == 10) { |

| screamer | 18:a15bfe7aaebd | 933 | |

| screamer | 18:a15bfe7aaebd | 934 | status = VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 935 | VL53L0X_REG_FINAL_RANGE_CONFIG_VALID_PHASE_HIGH, |

| screamer | 18:a15bfe7aaebd | 936 | 0x28); |

| screamer | 18:a15bfe7aaebd | 937 | status = VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 938 | VL53L0X_REG_FINAL_RANGE_CONFIG_VALID_PHASE_LOW, |

| screamer | 18:a15bfe7aaebd | 939 | 0x08); |

| screamer | 18:a15bfe7aaebd | 940 | |

| screamer | 18:a15bfe7aaebd | 941 | status |= VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 942 | VL53L0X_REG_GLOBAL_CONFIG_VCSEL_WIDTH, 0x03); |

| screamer | 18:a15bfe7aaebd | 943 | status |= VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 944 | VL53L0X_REG_ALGO_PHASECAL_CONFIG_TIMEOUT, 0x09); |

| screamer | 18:a15bfe7aaebd | 945 | |

| screamer | 18:a15bfe7aaebd | 946 | status |= VL53L0X_write_byte(dev, 0xff, 0x01); |

| screamer | 18:a15bfe7aaebd | 947 | status |= VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 948 | VL53L0X_REG_ALGO_PHASECAL_LIM, |

| screamer | 18:a15bfe7aaebd | 949 | 0x20); |

| screamer | 18:a15bfe7aaebd | 950 | status |= VL53L0X_write_byte(dev, 0xff, 0x00); |

| screamer | 18:a15bfe7aaebd | 951 | } else if (vcsel_pulse_period_pclk == 12) { |

| screamer | 18:a15bfe7aaebd | 952 | |

| screamer | 18:a15bfe7aaebd | 953 | status = VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 954 | VL53L0X_REG_FINAL_RANGE_CONFIG_VALID_PHASE_HIGH, |

| screamer | 18:a15bfe7aaebd | 955 | 0x38); |

| screamer | 18:a15bfe7aaebd | 956 | status = VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 957 | VL53L0X_REG_FINAL_RANGE_CONFIG_VALID_PHASE_LOW, |

| screamer | 18:a15bfe7aaebd | 958 | 0x08); |

| screamer | 18:a15bfe7aaebd | 959 | |

| screamer | 18:a15bfe7aaebd | 960 | status |= VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 961 | VL53L0X_REG_GLOBAL_CONFIG_VCSEL_WIDTH, 0x03); |

| screamer | 18:a15bfe7aaebd | 962 | status |= VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 963 | VL53L0X_REG_ALGO_PHASECAL_CONFIG_TIMEOUT, 0x08); |

| screamer | 18:a15bfe7aaebd | 964 | |

| screamer | 18:a15bfe7aaebd | 965 | status |= VL53L0X_write_byte(dev, 0xff, 0x01); |

| screamer | 18:a15bfe7aaebd | 966 | status |= VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 967 | VL53L0X_REG_ALGO_PHASECAL_LIM, |

| screamer | 18:a15bfe7aaebd | 968 | 0x20); |

| screamer | 18:a15bfe7aaebd | 969 | status |= VL53L0X_write_byte(dev, 0xff, 0x00); |

| screamer | 18:a15bfe7aaebd | 970 | } else if (vcsel_pulse_period_pclk == 14) { |

| screamer | 18:a15bfe7aaebd | 971 | |

| screamer | 18:a15bfe7aaebd | 972 | status = VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 973 | VL53L0X_REG_FINAL_RANGE_CONFIG_VALID_PHASE_HIGH, |

| screamer | 18:a15bfe7aaebd | 974 | 0x048); |

| screamer | 18:a15bfe7aaebd | 975 | status = VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 976 | VL53L0X_REG_FINAL_RANGE_CONFIG_VALID_PHASE_LOW, |

| screamer | 18:a15bfe7aaebd | 977 | 0x08); |

| screamer | 18:a15bfe7aaebd | 978 | |

| screamer | 18:a15bfe7aaebd | 979 | status |= VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 980 | VL53L0X_REG_GLOBAL_CONFIG_VCSEL_WIDTH, 0x03); |

| screamer | 18:a15bfe7aaebd | 981 | status |= VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 982 | VL53L0X_REG_ALGO_PHASECAL_CONFIG_TIMEOUT, 0x07); |

| screamer | 18:a15bfe7aaebd | 983 | |

| screamer | 18:a15bfe7aaebd | 984 | status |= VL53L0X_write_byte(dev, 0xff, 0x01); |

| screamer | 18:a15bfe7aaebd | 985 | status |= VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 986 | VL53L0X_REG_ALGO_PHASECAL_LIM, |

| screamer | 18:a15bfe7aaebd | 987 | 0x20); |

| screamer | 18:a15bfe7aaebd | 988 | status |= VL53L0X_write_byte(dev, 0xff, 0x00); |

| screamer | 18:a15bfe7aaebd | 989 | } |

| screamer | 18:a15bfe7aaebd | 990 | } |

| screamer | 18:a15bfe7aaebd | 991 | |

| screamer | 18:a15bfe7aaebd | 992 | |

| screamer | 18:a15bfe7aaebd | 993 | /* Re-calculate and apply timeouts, in macro periods */ |

| screamer | 18:a15bfe7aaebd | 994 | |

| screamer | 18:a15bfe7aaebd | 995 | if (status == VL53L0X_ERROR_NONE) { |

| screamer | 18:a15bfe7aaebd | 996 | vcsel_period_reg = lv53l0x_encode_vcsel_period((uint8_t) |

| screamer | 18:a15bfe7aaebd | 997 | vcsel_pulse_period_pclk); |

| screamer | 18:a15bfe7aaebd | 998 | |

| screamer | 18:a15bfe7aaebd | 999 | /* When the VCSEL period for the pre or final range is changed, |

| screamer | 18:a15bfe7aaebd | 1000 | * the corresponding timeout must be read from the device using |

| screamer | 18:a15bfe7aaebd | 1001 | * the current VCSEL period, then the new VCSEL period can be |

| screamer | 18:a15bfe7aaebd | 1002 | * applied. The timeout then must be written back to the device |

| screamer | 18:a15bfe7aaebd | 1003 | * using the new VCSEL period. |

| screamer | 18:a15bfe7aaebd | 1004 | * |

| screamer | 18:a15bfe7aaebd | 1005 | * For the MSRC timeout, the same applies - this timeout being |

| screamer | 18:a15bfe7aaebd | 1006 | * dependant on the pre-range vcsel period. |

| screamer | 18:a15bfe7aaebd | 1007 | */ |

| screamer | 18:a15bfe7aaebd | 1008 | switch (vcsel_period_type) { |

| screamer | 18:a15bfe7aaebd | 1009 | case VL53L0X_VCSEL_PERIOD_PRE_RANGE: |

| screamer | 18:a15bfe7aaebd | 1010 | status = get_sequence_step_timeout(dev, |

| screamer | 18:a15bfe7aaebd | 1011 | VL53L0X_SEQUENCESTEP_PRE_RANGE, |

| screamer | 18:a15bfe7aaebd | 1012 | &pre_range_timeout_micro_seconds); |

| screamer | 18:a15bfe7aaebd | 1013 | |

| screamer | 18:a15bfe7aaebd | 1014 | if (status == VL53L0X_ERROR_NONE) |

| screamer | 18:a15bfe7aaebd | 1015 | status = get_sequence_step_timeout(dev, |

| screamer | 18:a15bfe7aaebd | 1016 | VL53L0X_SEQUENCESTEP_MSRC, |

| screamer | 18:a15bfe7aaebd | 1017 | &msrc_timeout_micro_seconds); |

| screamer | 18:a15bfe7aaebd | 1018 | |

| screamer | 18:a15bfe7aaebd | 1019 | if (status == VL53L0X_ERROR_NONE) |

| screamer | 18:a15bfe7aaebd | 1020 | status = VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 1021 | VL53L0X_REG_PRE_RANGE_CONFIG_VCSEL_PERIOD, |

| screamer | 18:a15bfe7aaebd | 1022 | vcsel_period_reg); |

| screamer | 18:a15bfe7aaebd | 1023 | |

| screamer | 18:a15bfe7aaebd | 1024 | |

| screamer | 18:a15bfe7aaebd | 1025 | if (status == VL53L0X_ERROR_NONE) |

| screamer | 18:a15bfe7aaebd | 1026 | status = set_sequence_step_timeout(dev, |

| screamer | 18:a15bfe7aaebd | 1027 | VL53L0X_SEQUENCESTEP_PRE_RANGE, |

| screamer | 18:a15bfe7aaebd | 1028 | pre_range_timeout_micro_seconds); |

| screamer | 18:a15bfe7aaebd | 1029 | |

| screamer | 18:a15bfe7aaebd | 1030 | |

| screamer | 18:a15bfe7aaebd | 1031 | if (status == VL53L0X_ERROR_NONE) |

| screamer | 18:a15bfe7aaebd | 1032 | status = set_sequence_step_timeout(dev, |

| screamer | 18:a15bfe7aaebd | 1033 | VL53L0X_SEQUENCESTEP_MSRC, |

| screamer | 18:a15bfe7aaebd | 1034 | msrc_timeout_micro_seconds); |

| screamer | 18:a15bfe7aaebd | 1035 | |

| screamer | 18:a15bfe7aaebd | 1036 | VL53L0X_SETDEVICESPECIFICPARAMETER( |

| screamer | 18:a15bfe7aaebd | 1037 | dev, |

| screamer | 18:a15bfe7aaebd | 1038 | PreRangeVcselPulsePeriod, |

| screamer | 18:a15bfe7aaebd | 1039 | vcsel_pulse_period_pclk); |

| screamer | 18:a15bfe7aaebd | 1040 | break; |

| screamer | 18:a15bfe7aaebd | 1041 | case VL53L0X_VCSEL_PERIOD_FINAL_RANGE: |

| screamer | 18:a15bfe7aaebd | 1042 | status = get_sequence_step_timeout(dev, |

| screamer | 18:a15bfe7aaebd | 1043 | VL53L0X_SEQUENCESTEP_FINAL_RANGE, |

| screamer | 18:a15bfe7aaebd | 1044 | &final_range_timeout_micro_seconds); |

| screamer | 18:a15bfe7aaebd | 1045 | |

| screamer | 18:a15bfe7aaebd | 1046 | if (status == VL53L0X_ERROR_NONE) |

| screamer | 18:a15bfe7aaebd | 1047 | status = VL53L0X_write_byte(dev, |

| screamer | 18:a15bfe7aaebd | 1048 | VL53L0X_REG_FINAL_RANGE_CONFIG_VCSEL_PERIOD, |

| screamer | 18:a15bfe7aaebd | 1049 | vcsel_period_reg); |

| screamer | 18:a15bfe7aaebd | 1050 | |

| screamer | 18:a15bfe7aaebd | 1051 | |

| screamer | 18:a15bfe7aaebd | 1052 | if (status == VL53L0X_ERROR_NONE) |

| screamer | 18:a15bfe7aaebd | 1053 | status = set_sequence_step_timeout(dev, |

| screamer | 18:a15bfe7aaebd | 1054 | VL53L0X_SEQUENCESTEP_FINAL_RANGE, |