This Automatic mode is the most simple lib for MCU Gear. You don't need to think about Bank.

This is a MCU Gear Automatic mode library.

(日本語は英語の次に書いてあります。)

MCU Gear is a digital wiring extension board.(A kind of dynamic circuit changer.)

It can change its wiring dynamically, without the need of rewiring your device.

Your MCU can be connected to a theoretical maximum of 120 devices.

detail : http://mcugear.com/en/

You can save 8 schematics (bank 0-7) on Baseboard. But this Automatic mode is you don't think about Bank but little bit slow. Manual Mode is here -> http://mbed.org/users/Info/code/MCUGearM/

How to use it?

1,include library

1,include library

#include "mbed.h" #include "MCUGearBaseA.h" #include "MCUGearA.h" #include "commonA.h"

2,Declare Module

2,Declare Module

MCUGear myModule1(p28, p27, N_***_***_***); MCUGear myModule2(p28, p27, N_***_***_***);

myModule: Optional name for Module.

p28, p27, : I2C pins (KL25Z is "PTE0, PTE1")

N_*_*_* : Address. You can set it on the reverse side of the Module board.

3,Initialize baseboard

3,Initialize baseboard

initBase();

4,Make wiring data

4,Call wiring register

myModule1.setWire(IO_MBED_P9, IO_REG_IN_DIR, 5);

myModule1.setWire(IO_MBED_P15, IO_REG_OUT_DIR, 2);

myModule1.setWire(IO_MBED_P12, IO_REG_OUT_DIR, 0);

myModule2.setWire(IO_MBED_P13, IO_REG_OUT_DIR, 1);

myModule2.setWire(IO_MBED_P14, IO_REG_IN_DIR, 3);

myModule2.setWire(IO_MBED_P16, IO_REG_IN_DIR, 4);

see the reference on MCUGearBaseboardA.h file.

4,Call wiring register

// CPU I/O

typedef enum {

#if defined TARGET_LPC1768

IO_MBED_P15 = 0x80,

IO_MBED_P13,

IO_MBED_P16,

IO_MBED_P12,

IO_MBED_P5,

IO_MBED_P11,

IO_MBED_P23,

IO_MBED_P22,

IO_MBED_P26,

IO_MBED_P10,

IO_MBED_P21,

IO_MBED_P9,

IO_MBED_P6,

IO_MBED_P7,

IO_MBED_P8,

IO_MBED_P14,

IO_MBED_P24,

IO_MBED_P25,

IO_MBED_P28,

IO_MBED_P27

#endif

#if defined TARGET_KL25Z

IO_MBED_PTA5 = 0x80,

IO_MBED_PTC8,

IO_MBED_PTC9,

IO_MBED_PTD5,

IO_MBED_PTA13,

IO_MBED_PTD2,

IO_MBED_PTB1,

IO_MBED_PTB2,

IO_MBED_PTA2,

IO_MBED_PTD4,

IO_MBED_PTB3,

IO_MBED_PTA12,

IO_MBED_PTD0,

IO_MBED_PTD3,

IO_MBED_PTD1,

IO_MBED_PTA4,

IO_MBED_PTB0,

IO_MBED_PTA1,

IO_MBED_PTE0, //SDA

IO_MBED_PTE1 //SCL

#endif

} en_cpu_io;

setWire function

uint8_t setWire(uint8_t mcuIO, uint8_t direction, uint8_t moduleIO);

Set MCU's IO, Directionfrom MCU and module's IO number.

setWire() is wiring data to connect pin of MCU to pin of Module.

uint8_t mcuIO : You can choose 18 IOs.

uint8_t direction: choose signal direction IO_REG_OUT_DIR : output from MCU IO_REG_IN_DIR : input to MCU

uint8_t moduleIO: You can select module pin.

5,Open or close the module gate

5,Open or close the module gate

myModule1.connectModule(); ... (same as normal mbed code) ... myModule1.disconnectModule(); myModule2.connectModule(); ... (same as normal mbed code) ... myModule2.disconnectModule();

If you want to use many modules simultaneously as one circuit, you should use manual mode.

Sample code 1

Universal Module and LCD module test program.

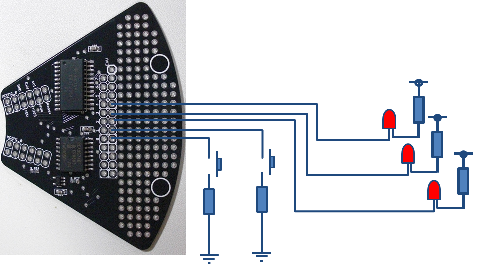

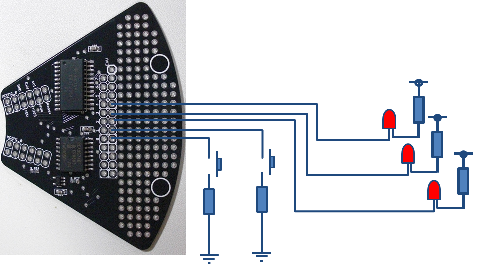

I set test function board like the below picture.(Universal module)

Sample code 1

#include "mbed.h"

#include "TextLCD.h"

#include "MCUGearBaseA.h"

#include "MCUGearA.h"

#include "commonA.h"

Serial pc(USBTX, USBRX); // tx, rx Set BaudRate = 115200 in main()

void setIOUni(MCUGear *mcugear);

void setIOLCD(MCUGear *mcugear);

DigitalOut myled(LED1);

MCUGear UniM(p28, p27, N_VDD_VDD_VDD); //2 Connector Universal Module

MCUGear LCDM(p28, p27, N_VDD_VSS_VSS); //LCD Module

DigitalOut Dout1(p11);

DigitalOut Dout2(p12);

DigitalOut Dout3(p13);

DigitalOut Dout4(p14);

DigitalOut Dout5(p15);

DigitalIn Din1(p9);

DigitalIn Din2(p10);

int main() {

int sw1 = 0;

int sw2 = 0;

initBase(); //initialize Baseboard

//set schematic select 0-7

UniM.detectModule(); //save location data in MCUGear class.

LCDM.detectModule(); //save location data in MCUGear class.

setIOUni(&UniM);//make schematic Bank0

setIOLCD(&LCDM);//make schematic Bank0

LCDM.connectModuleA();

TextLCD lcd(p21, p22, p23, p24, p25, p26, TextLCD::LCD16x2); // rs, e, d4-d7

lcd.cls();

lcd.printf("Hello World!\n");

wait(1);

LCDM.disconnectModule();

while(1) {

UniM.connectModuleA();

sw1 = Din1.read();

sw2 = Din2.read();

printf("sw1 = %d sw2 = %d\r\n",sw1,sw2);

UniM.disconnectModule();

LCDM.connectModuleA();

lcd.printf(" "); //set IO as a neutral position

lcd.cls(); //clear LCD

lcd.printf("sw1 = %d\nsw2 = %d",sw1,sw2); //write LCD data

wait_ms(10); //delay for view the LCD

LCDM.disconnectModule();

UniM.connectModuleA();

Dout1 = 0;

Dout2 = 1;

Dout3 = 1;

wait(0.3);

Dout1 = 1;

Dout2 = 0;

Dout3 = 1;

wait(0.3);

Dout1 = 1;

Dout2 = 1;

Dout3 = 0;

wait(0.3);

UniM.disconnectModule();

}

}

void setIOUni(MCUGear *mcugear){

mcugear->setWireA(IO_MBED_P9, IO_REG_IN_DIR, 0);

mcugear->setWireA(IO_MBED_P10, IO_REG_IN_DIR, 1);

mcugear->setWireA(IO_MBED_P11, IO_REG_OUT_DIR,2);

mcugear->setWireA(IO_MBED_P12, IO_REG_OUT_DIR,3);

mcugear->setWireA(IO_MBED_P13, IO_REG_OUT_DIR,4);

}

void setIOLCD(MCUGear *mcugear){

mcugear->setWireA(IO_MBED_P21, IO_REG_OUT_DIR,0);

mcugear->setWireA(IO_MBED_P22, IO_REG_OUT_DIR,1);

mcugear->setWireA(IO_MBED_P23, IO_REG_OUT_DIR,2);

mcugear->setWireA(IO_MBED_P24, IO_REG_OUT_DIR,3);

mcugear->setWireA(IO_MBED_P25, IO_REG_OUT_DIR,4);

mcugear->setWireA(IO_MBED_P26, IO_REG_OUT_DIR,5);

}

日本語説明

MCU Gearの自動モードライブラリです。

detail : http://mcugear.com/en/

自動モードは8つのBank設定は考えずに実行できます。同時に複数のモジュールをつなげたい場合はマニュアルモードをご利用ください -> http://mbed.org/users/Info/code/MCUGearM/

使い方

1,ライブラリーをインクルード

1,include library

#include "mbed.h" #include "MCUGearBaseA.h" #include "MCUGearA.h" #include "commonA.h"

2,モジュールを定義します

2,Declare Module

MCUGear myModule1(p28, p27, N_***_***_***); MCUGear myModule2(p28, p27, N_***_***_***);

myModule: モジュールの好きな名前を付けられます。

p28, p27, : I2C pins (KL25Z is "PTE0, PTE1")

N_*_*_* : Address. モジュールの裏面に設定したアドレスを入れます。

3,ベースボード初期化

3,Initialize baseboard

initBase();

4,配線データの登録

4,Call wiring register

myModule1.setWire(IO_MBED_P9, IO_REG_IN_DIR, 5);

myModule1.setWire(IO_MBED_P15, IO_REG_OUT_DIR, 2);

myModule1.setWire(IO_MBED_P12, IO_REG_OUT_DIR, 0);

myModule2.setWire(IO_MBED_P13, IO_REG_OUT_DIR, 1);

myModule2.setWire(IO_MBED_P14, IO_REG_IN_DIR, 3);

myModule2.setWire(IO_MBED_P16, IO_REG_IN_DIR, 4);

MCUGearBaseboardA.h ファイルも参考にしてください。

4,Call wiring register

// CPU I/O

typedef enum {

#if defined TARGET_LPC1768

IO_MBED_P15 = 0x80,

IO_MBED_P13,

IO_MBED_P16,

IO_MBED_P12,

IO_MBED_P5,

IO_MBED_P11,

IO_MBED_P23,

IO_MBED_P22,

IO_MBED_P26,

IO_MBED_P10,

IO_MBED_P21,

IO_MBED_P9,

IO_MBED_P6,

IO_MBED_P7,

IO_MBED_P8,

IO_MBED_P14,

IO_MBED_P24,

IO_MBED_P25,

IO_MBED_P28,

IO_MBED_P27

#endif

#if defined TARGET_KL25Z

IO_MBED_PTA5 = 0x80,

IO_MBED_PTC8,

IO_MBED_PTC9,

IO_MBED_PTD5,

IO_MBED_PTA13,

IO_MBED_PTD2,

IO_MBED_PTB1,

IO_MBED_PTB2,

IO_MBED_PTA2,

IO_MBED_PTD4,

IO_MBED_PTB3,

IO_MBED_PTA12,

IO_MBED_PTD0,

IO_MBED_PTD3,

IO_MBED_PTD1,

IO_MBED_PTA4,

IO_MBED_PTB0,

IO_MBED_PTA1,

IO_MBED_PTE0, //SDA

IO_MBED_PTE1 //SCL

#endif

} en_cpu_io;

setWire function

uint8_t setWire(uint8_t mcuIO, uint8_t direction, uint8_t moduleIO);

引数はマイコンのIO、マイコンからの入出力方向とモジュールの端子番号 setWire()関数はmbedの端子とモジュールの端子の割り振り方を決める関数です。

uint8_t mcuIO : mbedの18端子がアダプターボード(MCUボード)を介してベースボードに接続されています。(残りの端子はアダプターボード(MCUボード)から端子が出ています。)

uint8_t direction: mbedから見て入力か出力かを設定します。 IO_REG_OUT_DIR : output from MCU IO_REG_IN_DIR : input to MCU

uint8_t moduleIO: モジュールの出口の端子をどれにするかを決めます。

5,モジュールのゲート開閉

5,Open or close the module gate

myModule1.connectModule(); ... (same as normal mbed code) ... myModule1.disconnectModule(); myModule2.connectModule(); ... (same as normal mbed code) ... myModule2.disconnectModule();

If you want to use many modules simultaneously as one circuit, you should use manual mode. 同時に複数のモジュールに接続して動かすには

Sample code 1

ユニバーサルモジュールとLCDモジュールを接続した例です。

ユニバーサルモジュールは以下の図のように接続します。

Sample code 1

#include "mbed.h"

#include "TextLCD.h"

#include "MCUGearBaseA.h"

#include "MCUGearA.h"

#include "commonA.h"

Serial pc(USBTX, USBRX); // tx, rx Set BaudRate = 115200 in main()

void setIOUni(MCUGear *mcugear);

void setIOLCD(MCUGear *mcugear);

DigitalOut myled(LED1);

MCUGear UniM(p28, p27, N_VDD_VDD_VDD); //2 Connector Universal Module

MCUGear LCDM(p28, p27, N_VDD_VSS_VSS); //LCD Module

DigitalOut Dout1(p11);

DigitalOut Dout2(p12);

DigitalOut Dout3(p13);

DigitalOut Dout4(p14);

DigitalOut Dout5(p15);

DigitalIn Din1(p9);

DigitalIn Din2(p10);

int main() {

int sw1 = 0;

int sw2 = 0;

initBase(); //initialize Baseboard

//set schematic select 0-7

UniM.detectModule(); //save location data in MCUGear class.

LCDM.detectModule(); //save location data in MCUGear class.

setIOUni(&UniM);//make schematic Bank0

setIOLCD(&LCDM);//make schematic Bank0

LCDM.connectModuleA();

TextLCD lcd(p21, p22, p23, p24, p25, p26, TextLCD::LCD16x2); // rs, e, d4-d7

lcd.cls();

lcd.printf("Hello World!\n");

wait(1);

LCDM.disconnectModule();

while(1) {

UniM.connectModuleA();

sw1 = Din1.read();

sw2 = Din2.read();

printf("sw1 = %d sw2 = %d\r\n",sw1,sw2);

UniM.disconnectModule();

LCDM.connectModuleA();

lcd.printf(" "); //set IO as a neutral position

lcd.cls(); //clear LCD

lcd.printf("sw1 = %d\nsw2 = %d",sw1,sw2); //write LCD data

wait_ms(10); //delay for view the LCD

LCDM.disconnectModule();

UniM.connectModuleA();

Dout1 = 0;

Dout2 = 1;

Dout3 = 1;

wait(0.3);

Dout1 = 1;

Dout2 = 0;

Dout3 = 1;

wait(0.3);

Dout1 = 1;

Dout2 = 1;

Dout3 = 0;

wait(0.3);

UniM.disconnectModule();

}

}

void setIOUni(MCUGear *mcugear){

mcugear->setWireA(IO_MBED_P9, IO_REG_IN_DIR, 0);

mcugear->setWireA(IO_MBED_P10, IO_REG_IN_DIR, 1);

mcugear->setWireA(IO_MBED_P11, IO_REG_OUT_DIR,2);

mcugear->setWireA(IO_MBED_P12, IO_REG_OUT_DIR,3);

mcugear->setWireA(IO_MBED_P13, IO_REG_OUT_DIR,4);

}

void setIOLCD(MCUGear *mcugear){

mcugear->setWireA(IO_MBED_P21, IO_REG_OUT_DIR,0);

mcugear->setWireA(IO_MBED_P22, IO_REG_OUT_DIR,1);

mcugear->setWireA(IO_MBED_P23, IO_REG_OUT_DIR,2);

mcugear->setWireA(IO_MBED_P24, IO_REG_OUT_DIR,3);

mcugear->setWireA(IO_MBED_P25, IO_REG_OUT_DIR,4);

mcugear->setWireA(IO_MBED_P26, IO_REG_OUT_DIR,5);

}

MCUGearBaseA.h@0:12d93184b350, 2014-03-09 (annotated)

- Committer:

- Info

- Date:

- Sun Mar 09 09:33:14 2014 +0000

- Revision:

- 0:12d93184b350

Automatic module changer for MCU Gear. It make circuit each time. You don't need to think about the Bank.

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| Info | 0:12d93184b350 | 1 | /* MCU Gear Library, only for testing MCUGear without any circuit you connected. |

| Info | 0:12d93184b350 | 2 | * Copyright (c) 2013, NestEgg Inc., http://www.mcugear.com/ |

| Info | 0:12d93184b350 | 3 | * |

| Info | 0:12d93184b350 | 4 | * Permission is hereby granted, free of charge, to any person obtaining a copy |

| Info | 0:12d93184b350 | 5 | * of this software and associated documentation files (the "Software"), to deal |

| Info | 0:12d93184b350 | 6 | * in the Software without restriction, including without limitation the rights |

| Info | 0:12d93184b350 | 7 | * to use, copy, modify, merge, publish, distribute, sublicense, and/or sell |

| Info | 0:12d93184b350 | 8 | * copies of the Software, and to permit persons to whom the Software is |

| Info | 0:12d93184b350 | 9 | * furnished to do so, subject to the following conditions: |

| Info | 0:12d93184b350 | 10 | * |

| Info | 0:12d93184b350 | 11 | * The above copyright notice and this permission notice shall be included in |

| Info | 0:12d93184b350 | 12 | * all copies or substantial portions of the Software. |

| Info | 0:12d93184b350 | 13 | * |

| Info | 0:12d93184b350 | 14 | * THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR |

| Info | 0:12d93184b350 | 15 | * IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, |

| Info | 0:12d93184b350 | 16 | * FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE |

| Info | 0:12d93184b350 | 17 | * AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER |

| Info | 0:12d93184b350 | 18 | * LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, |

| Info | 0:12d93184b350 | 19 | * OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN |

| Info | 0:12d93184b350 | 20 | * THE SOFTWARE. |

| Info | 0:12d93184b350 | 21 | */ |

| Info | 0:12d93184b350 | 22 | |

| Info | 0:12d93184b350 | 23 | #include "commonA.h" |

| Info | 0:12d93184b350 | 24 | |

| Info | 0:12d93184b350 | 25 | |

| Info | 0:12d93184b350 | 26 | #define FPGA_SYSINFO_0 0x00 |

| Info | 0:12d93184b350 | 27 | #define FPGA_SYSINFO_1 0x04 |

| Info | 0:12d93184b350 | 28 | #define FPGA_ENABLE 0x08 |

| Info | 0:12d93184b350 | 29 | #define FPGA_DETECT 0x14 |

| Info | 0:12d93184b350 | 30 | |

| Info | 0:12d93184b350 | 31 | void fpga_write(int dev_adr,unsigned char adr, unsigned char data); |

| Info | 0:12d93184b350 | 32 | unsigned char fpga_read(int dev_adr,unsigned char adr); |

| Info | 0:12d93184b350 | 33 | void initBase(void); |

| Info | 0:12d93184b350 | 34 | //void startReg(uint8_t bank); |

| Info | 0:12d93184b350 | 35 | //void endReg(uint8_t bank); |

| Info | 0:12d93184b350 | 36 | void deleteBank(uint8_t bank); |

| Info | 0:12d93184b350 | 37 | void changeBank(uint8_t bank); |

| Info | 0:12d93184b350 | 38 | |

| Info | 0:12d93184b350 | 39 | |

| Info | 0:12d93184b350 | 40 | // FGPGA CPU I/O |

| Info | 0:12d93184b350 | 41 | typedef enum { |

| Info | 0:12d93184b350 | 42 | |

| Info | 0:12d93184b350 | 43 | #if defined TARGET_LPC1768 |

| Info | 0:12d93184b350 | 44 | IO_MBED_P15 = 0x80, |

| Info | 0:12d93184b350 | 45 | IO_MBED_P13, |

| Info | 0:12d93184b350 | 46 | IO_MBED_P16, |

| Info | 0:12d93184b350 | 47 | IO_MBED_P12, |

| Info | 0:12d93184b350 | 48 | IO_MBED_P5, |

| Info | 0:12d93184b350 | 49 | IO_MBED_P11, |

| Info | 0:12d93184b350 | 50 | IO_MBED_P23, |

| Info | 0:12d93184b350 | 51 | IO_MBED_P22, |

| Info | 0:12d93184b350 | 52 | IO_MBED_P26, |

| Info | 0:12d93184b350 | 53 | IO_MBED_P10, |

| Info | 0:12d93184b350 | 54 | IO_MBED_P21, |

| Info | 0:12d93184b350 | 55 | IO_MBED_P9, |

| Info | 0:12d93184b350 | 56 | IO_MBED_P6, |

| Info | 0:12d93184b350 | 57 | IO_MBED_P7, |

| Info | 0:12d93184b350 | 58 | IO_MBED_P8, |

| Info | 0:12d93184b350 | 59 | IO_MBED_P14, |

| Info | 0:12d93184b350 | 60 | IO_MBED_P24, |

| Info | 0:12d93184b350 | 61 | IO_MBED_P25, |

| Info | 0:12d93184b350 | 62 | IO_MBED_P28, |

| Info | 0:12d93184b350 | 63 | IO_MBED_P27 |

| Info | 0:12d93184b350 | 64 | #endif |

| Info | 0:12d93184b350 | 65 | |

| Info | 0:12d93184b350 | 66 | #if defined TARGET_KL25Z |

| Info | 0:12d93184b350 | 67 | |

| Info | 0:12d93184b350 | 68 | IO_MBED_PTA5 = 0x80, |

| Info | 0:12d93184b350 | 69 | IO_MBED_PTC8, |

| Info | 0:12d93184b350 | 70 | IO_MBED_PTC9, |

| Info | 0:12d93184b350 | 71 | IO_MBED_PTD5, |

| Info | 0:12d93184b350 | 72 | IO_MBED_PTA13, |

| Info | 0:12d93184b350 | 73 | IO_MBED_PTD2, |

| Info | 0:12d93184b350 | 74 | IO_MBED_PTB1, |

| Info | 0:12d93184b350 | 75 | IO_MBED_PTB2, |

| Info | 0:12d93184b350 | 76 | IO_MBED_PTA2, |

| Info | 0:12d93184b350 | 77 | IO_MBED_PTD4, |

| Info | 0:12d93184b350 | 78 | IO_MBED_PTB3, |

| Info | 0:12d93184b350 | 79 | IO_MBED_PTA12, |

| Info | 0:12d93184b350 | 80 | IO_MBED_PTD0, |

| Info | 0:12d93184b350 | 81 | IO_MBED_PTD3, |

| Info | 0:12d93184b350 | 82 | IO_MBED_PTD1, |

| Info | 0:12d93184b350 | 83 | IO_MBED_PTA4, |

| Info | 0:12d93184b350 | 84 | IO_MBED_PTB0, |

| Info | 0:12d93184b350 | 85 | IO_MBED_PTA1, |

| Info | 0:12d93184b350 | 86 | IO_MBED_PTE0, //SDA |

| Info | 0:12d93184b350 | 87 | IO_MBED_PTE1 //SCL |

| Info | 0:12d93184b350 | 88 | #endif |

| Info | 0:12d93184b350 | 89 | |

| Info | 0:12d93184b350 | 90 | } en_cpu_io; |

| Info | 0:12d93184b350 | 91 | |

| Info | 0:12d93184b350 | 92 | // FPGA EXT I/O |

| Info | 0:12d93184b350 | 93 | typedef enum { |

| Info | 0:12d93184b350 | 94 | IO_CON1_1 = 0, |

| Info | 0:12d93184b350 | 95 | IO_CON1_2, |

| Info | 0:12d93184b350 | 96 | IO_CON1_3, |

| Info | 0:12d93184b350 | 97 | IO_CON1_4, |

| Info | 0:12d93184b350 | 98 | IO_CON2_1, |

| Info | 0:12d93184b350 | 99 | IO_CON2_2, |

| Info | 0:12d93184b350 | 100 | IO_CON2_3, |

| Info | 0:12d93184b350 | 101 | IO_CON2_4, |

| Info | 0:12d93184b350 | 102 | IO_CON3_1, |

| Info | 0:12d93184b350 | 103 | IO_CON3_2, |

| Info | 0:12d93184b350 | 104 | IO_CON3_3, |

| Info | 0:12d93184b350 | 105 | IO_CON3_4, |

| Info | 0:12d93184b350 | 106 | IO_CON4_1, |

| Info | 0:12d93184b350 | 107 | IO_CON4_2, |

| Info | 0:12d93184b350 | 108 | IO_CON4_3, |

| Info | 0:12d93184b350 | 109 | IO_CON4_4, |

| Info | 0:12d93184b350 | 110 | IO_CON5_1, |

| Info | 0:12d93184b350 | 111 | IO_CON5_2, |

| Info | 0:12d93184b350 | 112 | IO_CON5_3, |

| Info | 0:12d93184b350 | 113 | IO_CON5_4, |

| Info | 0:12d93184b350 | 114 | IO_CON6_1, |

| Info | 0:12d93184b350 | 115 | IO_CON6_2, |

| Info | 0:12d93184b350 | 116 | IO_CON6_3, |

| Info | 0:12d93184b350 | 117 | IO_CON6_4, |

| Info | 0:12d93184b350 | 118 | IO_CON7_1, |

| Info | 0:12d93184b350 | 119 | IO_CON7_2, |

| Info | 0:12d93184b350 | 120 | IO_CON7_3, |

| Info | 0:12d93184b350 | 121 | IO_CON7_4, |

| Info | 0:12d93184b350 | 122 | IO_CON8_1, |

| Info | 0:12d93184b350 | 123 | IO_CON8_2, |

| Info | 0:12d93184b350 | 124 | IO_CON8_3, |

| Info | 0:12d93184b350 | 125 | IO_CON8_4, |

| Info | 0:12d93184b350 | 126 | IO_CON9_1, |

| Info | 0:12d93184b350 | 127 | IO_CON9_2, |

| Info | 0:12d93184b350 | 128 | IO_CON9_3, |

| Info | 0:12d93184b350 | 129 | IO_CON9_4, |

| Info | 0:12d93184b350 | 130 | IO_CON10_1, |

| Info | 0:12d93184b350 | 131 | IO_CON10_2, |

| Info | 0:12d93184b350 | 132 | IO_CON10_3, |

| Info | 0:12d93184b350 | 133 | IO_CON10_4, |

| Info | 0:12d93184b350 | 134 | IO_CON11_1, |

| Info | 0:12d93184b350 | 135 | IO_CON11_2, |

| Info | 0:12d93184b350 | 136 | IO_CON11_3, |

| Info | 0:12d93184b350 | 137 | IO_CON11_4, |

| Info | 0:12d93184b350 | 138 | IO_CON12_1, |

| Info | 0:12d93184b350 | 139 | IO_CON12_2, |

| Info | 0:12d93184b350 | 140 | IO_CON12_3, |

| Info | 0:12d93184b350 | 141 | IO_CON12_4 |

| Info | 0:12d93184b350 | 142 | } en_fpga_io; |

| Info | 0:12d93184b350 | 143 | |

| Info | 0:12d93184b350 | 144 | typedef enum { |

| Info | 0:12d93184b350 | 145 | IO_REG_EN = 0x80, |

| Info | 0:12d93184b350 | 146 | IO_REG_OUT_DIR = 0x40, |

| Info | 0:12d93184b350 | 147 | IO_REG_IN_DIR = 0x00, |

| Info | 0:12d93184b350 | 148 | IO_REG_DISABLE = 0x3f |

| Info | 0:12d93184b350 | 149 | } en_fpga_io_reg; |

| Info | 0:12d93184b350 | 150 | |

| Info | 0:12d93184b350 | 151 |

mille feuille

mille feuille