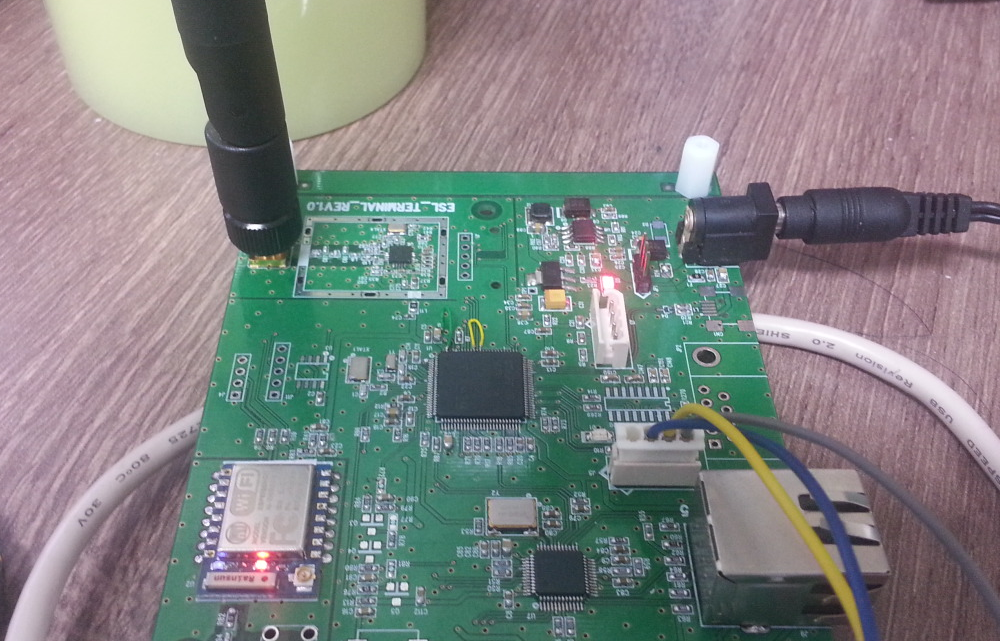

This is modified program from original CC1101_Transceiver. CC1101 Test succeeded STM32-F407 platform. Feature are improved little bit.

Dependencies: mbed

TI CC1101 chip is embedded along with STM32-F407 MCU.

CC1101.h@1:e96096a7b90b, 2015-03-31 (annotated)

- Committer:

- hillkim7

- Date:

- Tue Mar 31 07:48:52 2015 +0000

- Revision:

- 1:e96096a7b90b

- Parent:

- 0:9df942ea84f4

- Child:

- 2:54c832c68208

CC1101 Test with STM32-F407 platform

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| tmav123 | 0:9df942ea84f4 | 1 | /** |

| tmav123 | 0:9df942ea84f4 | 2 | * @author Athanassios Mavrogeorgiadis |

| tmav123 | 0:9df942ea84f4 | 3 | * @author TI CC1101 library developed by Athanassios Mavrogeorgiadis (tmav Electronics) as template based on TI C8051 SOURCE CODE swrc021f |

| tmav123 | 0:9df942ea84f4 | 4 | * @section LICENSE |

| tmav123 | 0:9df942ea84f4 | 5 | * |

| tmav123 | 0:9df942ea84f4 | 6 | * Copyright (c) 2010 ARM Limited |

| tmav123 | 0:9df942ea84f4 | 7 | * |

| tmav123 | 0:9df942ea84f4 | 8 | * Permission is hereby granted, free of charge, to any person obtaining a copy |

| tmav123 | 0:9df942ea84f4 | 9 | * of this software and associated documentation files (the "Software"), to deal |

| tmav123 | 0:9df942ea84f4 | 10 | * in the Software without restriction, including without limitation the rights |

| tmav123 | 0:9df942ea84f4 | 11 | * to use, copy, modify, merge, publish, distribute, sublicense, and/or sell |

| tmav123 | 0:9df942ea84f4 | 12 | * copies of the Software, and to permit persons to whom the Software is |

| tmav123 | 0:9df942ea84f4 | 13 | * furnished to do so, subject to the following conditions: |

| tmav123 | 0:9df942ea84f4 | 14 | * |

| tmav123 | 0:9df942ea84f4 | 15 | * The above copyright notice and this permission notice shall be included in |

| tmav123 | 0:9df942ea84f4 | 16 | * all copies or substantial portions of the Software. |

| tmav123 | 0:9df942ea84f4 | 17 | * |

| tmav123 | 0:9df942ea84f4 | 18 | * THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR |

| tmav123 | 0:9df942ea84f4 | 19 | * IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, |

| tmav123 | 0:9df942ea84f4 | 20 | * FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE |

| tmav123 | 0:9df942ea84f4 | 21 | * AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER |

| tmav123 | 0:9df942ea84f4 | 22 | * LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, |

| tmav123 | 0:9df942ea84f4 | 23 | * OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN |

| tmav123 | 0:9df942ea84f4 | 24 | * THE SOFTWARE. |

| tmav123 | 0:9df942ea84f4 | 25 | * |

| tmav123 | 0:9df942ea84f4 | 26 | * @section DESCRIPTION |

| tmav123 | 0:9df942ea84f4 | 27 | * |

| tmav123 | 0:9df942ea84f4 | 28 | * CC1101 Low-Power Sub-1 GHz RF Transceiver CC1101. |

| tmav123 | 0:9df942ea84f4 | 29 | * |

| tmav123 | 0:9df942ea84f4 | 30 | * Datasheet: |

| tmav123 | 0:9df942ea84f4 | 31 | * |

| tmav123 | 0:9df942ea84f4 | 32 | * http://focus.ti.com/lit/ds/swrs061f/swrs061f.pdf |

| tmav123 | 0:9df942ea84f4 | 33 | */ |

| tmav123 | 0:9df942ea84f4 | 34 | |

| tmav123 | 0:9df942ea84f4 | 35 | #ifndef MBED_CC1101_H |

| tmav123 | 0:9df942ea84f4 | 36 | #define MBED_CC1101_H |

| tmav123 | 0:9df942ea84f4 | 37 | |

| tmav123 | 0:9df942ea84f4 | 38 | /** |

| tmav123 | 0:9df942ea84f4 | 39 | * Includes |

| tmav123 | 0:9df942ea84f4 | 40 | */ |

| tmav123 | 0:9df942ea84f4 | 41 | #include "mbed.h" |

| tmav123 | 0:9df942ea84f4 | 42 | |

| tmav123 | 0:9df942ea84f4 | 43 | /** |

| tmav123 | 0:9df942ea84f4 | 44 | * Defines |

| tmav123 | 0:9df942ea84f4 | 45 | */ |

| tmav123 | 0:9df942ea84f4 | 46 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 47 | //------------------------------------------------------------------------------------------------------ |

| tmav123 | 0:9df942ea84f4 | 48 | // CC2500/CC1100 STROBE, CONTROL AND STATUS REGSITER |

| tmav123 | 0:9df942ea84f4 | 49 | #define CCxxx0_IOCFG2 0x00 // GDO2 output pin configuration |

| tmav123 | 0:9df942ea84f4 | 50 | #define CCxxx0_IOCFG1 0x01 // GDO1 output pin configuration |

| tmav123 | 0:9df942ea84f4 | 51 | #define CCxxx0_FIFOTHR 0x03 // RX FIFO and TX FIFO thresholds |

| tmav123 | 0:9df942ea84f4 | 52 | #define CCxxx0_SYNC1 0x04 // Sync word, high byte |

| tmav123 | 0:9df942ea84f4 | 53 | #define CCxxx0_SYNC0 0x05 // Sync word, low byte |

| tmav123 | 0:9df942ea84f4 | 54 | #define CCxxx0_IOCFG0 0x02 // GDO0 output pin configuration |

| tmav123 | 0:9df942ea84f4 | 55 | #define CCxxx0_FIFOTHR 0x03 // RX FIFO and TX FIFO thresholds |

| tmav123 | 0:9df942ea84f4 | 56 | #define CCxxx0_SYNC1 0x04 // Sync word, high byte |

| tmav123 | 0:9df942ea84f4 | 57 | #define CCxxx0_SYNC0 0x05 // Sync word, low byte |

| tmav123 | 0:9df942ea84f4 | 58 | #define CCxxx0_PKTLEN 0x06 // Packet length |

| tmav123 | 0:9df942ea84f4 | 59 | #define CCxxx0_PKTCTRL1 0x07 // Packet automation control |

| tmav123 | 0:9df942ea84f4 | 60 | #define CCxxx0_PKTCTRL0 0x08 // Packet automation control |

| tmav123 | 0:9df942ea84f4 | 61 | #define CCxxx0_ADDR 0x09 // Device address |

| tmav123 | 0:9df942ea84f4 | 62 | #define CCxxx0_CHANNR 0x0A // Channel number |

| tmav123 | 0:9df942ea84f4 | 63 | #define CCxxx0_FSCTRL1 0x0B // Frequency synthesizer control |

| tmav123 | 0:9df942ea84f4 | 64 | #define CCxxx0_FSCTRL0 0x0C // Frequency synthesizer control |

| tmav123 | 0:9df942ea84f4 | 65 | #define CCxxx0_FREQ2 0x0D // Frequency control word, high byte |

| tmav123 | 0:9df942ea84f4 | 66 | #define CCxxx0_FREQ1 0x0E // Frequency control word, middle byte |

| tmav123 | 0:9df942ea84f4 | 67 | #define CCxxx0_FREQ0 0x0F // Frequency control word, low byte |

| tmav123 | 0:9df942ea84f4 | 68 | #define CCxxx0_MDMCFG4 0x10 // Modem configuration |

| tmav123 | 0:9df942ea84f4 | 69 | #define CCxxx0_MDMCFG3 0x11 // Modem configuration |

| tmav123 | 0:9df942ea84f4 | 70 | #define CCxxx0_MDMCFG2 0x12 // Modem configuration |

| tmav123 | 0:9df942ea84f4 | 71 | #define CCxxx0_MDMCFG1 0x13 // Modem configuration |

| tmav123 | 0:9df942ea84f4 | 72 | #define CCxxx0_MDMCFG0 0x14 // Modem configuration |

| tmav123 | 0:9df942ea84f4 | 73 | #define CCxxx0_DEVIATN 0x15 // Modem deviation setting |

| tmav123 | 0:9df942ea84f4 | 74 | #define CCxxx0_MCSM2 0x16 // Main Radio Control State Machine configuration |

| tmav123 | 0:9df942ea84f4 | 75 | #define CCxxx0_MCSM1 0x17 // Main Radio Control State Machine configuration |

| tmav123 | 0:9df942ea84f4 | 76 | #define CCxxx0_MCSM0 0x18 // Main Radio Control State Machine configuration |

| tmav123 | 0:9df942ea84f4 | 77 | #define CCxxx0_FOCCFG 0x19 // Frequency Offset Compensation configuration |

| tmav123 | 0:9df942ea84f4 | 78 | #define CCxxx0_BSCFG 0x1A // Bit Synchronization configuration |

| tmav123 | 0:9df942ea84f4 | 79 | #define CCxxx0_AGCCTRL2 0x1B // AGC control |

| tmav123 | 0:9df942ea84f4 | 80 | #define CCxxx0_AGCCTRL1 0x1C // AGC control |

| tmav123 | 0:9df942ea84f4 | 81 | #define CCxxx0_AGCCTRL0 0x1D // AGC control |

| tmav123 | 0:9df942ea84f4 | 82 | #define CCxxx0_WOREVT1 0x1E // High byte Event 0 timeout |

| tmav123 | 0:9df942ea84f4 | 83 | #define CCxxx0_WOREVT0 0x1F // Low byte Event 0 timeout |

| tmav123 | 0:9df942ea84f4 | 84 | #define CCxxx0_WORCTRL 0x20 // Wake On Radio control |

| tmav123 | 0:9df942ea84f4 | 85 | #define CCxxx0_FREND1 0x21 // Front end RX configuration |

| tmav123 | 0:9df942ea84f4 | 86 | #define CCxxx0_FREND0 0x22 // Front end TX configuration |

| tmav123 | 0:9df942ea84f4 | 87 | #define CCxxx0_FSCAL3 0x23 // Frequency synthesizer calibration |

| tmav123 | 0:9df942ea84f4 | 88 | #define CCxxx0_FSCAL2 0x24 // Frequency synthesizer calibration |

| tmav123 | 0:9df942ea84f4 | 89 | #define CCxxx0_FSCAL1 0x25 // Frequency synthesizer calibration |

| tmav123 | 0:9df942ea84f4 | 90 | #define CCxxx0_FSCAL0 0x26 // Frequency synthesizer calibration |

| tmav123 | 0:9df942ea84f4 | 91 | #define CCxxx0_RCCTRL1 0x27 // RC oscillator configuration |

| tmav123 | 0:9df942ea84f4 | 92 | #define CCxxx0_RCCTRL0 0x28 // RC oscillator configuration |

| tmav123 | 0:9df942ea84f4 | 93 | #define CCxxx0_FSTEST 0x29 // Frequency synthesizer calibration control |

| tmav123 | 0:9df942ea84f4 | 94 | #define CCxxx0_PTEST 0x2A // Production test |

| tmav123 | 0:9df942ea84f4 | 95 | #define CCxxx0_AGCTEST 0x2B // AGC test |

| tmav123 | 0:9df942ea84f4 | 96 | #define CCxxx0_TEST2 0x2C // Various test settings |

| tmav123 | 0:9df942ea84f4 | 97 | #define CCxxx0_TEST1 0x2D // Various test settings |

| tmav123 | 0:9df942ea84f4 | 98 | #define CCxxx0_TEST0 0x2E // Various test settings |

| tmav123 | 0:9df942ea84f4 | 99 | |

| tmav123 | 0:9df942ea84f4 | 100 | // Strobe commands |

| tmav123 | 0:9df942ea84f4 | 101 | #define CCxxx0_SRES 0x30 // Reset chip. |

| tmav123 | 0:9df942ea84f4 | 102 | #define CCxxx0_SFSTXON 0x31 // Enable and calibrate frequency synthesizer (if MCSM0.FS_AUTOCAL=1). |

| hillkim7 | 1:e96096a7b90b | 103 | // If in RX/TX: Go to a wait state where only the synthesizer is |

| hillkim7 | 1:e96096a7b90b | 104 | // running (for quick RX / TX turnaround). |

| tmav123 | 0:9df942ea84f4 | 105 | #define CCxxx0_SXOFF 0x32 // Turn off crystal oscillator. |

| tmav123 | 0:9df942ea84f4 | 106 | #define CCxxx0_SCAL 0x33 // Calibrate frequency synthesizer and turn it off |

| hillkim7 | 1:e96096a7b90b | 107 | // (enables quick start). |

| tmav123 | 0:9df942ea84f4 | 108 | #define CCxxx0_SRX 0x34 // Enable RX. Perform calibration first if coming from IDLE and |

| hillkim7 | 1:e96096a7b90b | 109 | // MCSM0.FS_AUTOCAL=1. |

| tmav123 | 0:9df942ea84f4 | 110 | #define CCxxx0_STX 0x35 // In IDLE state: Enable TX. Perform calibration first if |

| hillkim7 | 1:e96096a7b90b | 111 | // MCSM0.FS_AUTOCAL=1. If in RX state and CCA is enabled: |

| hillkim7 | 1:e96096a7b90b | 112 | // Only go to TX if channel is clear. |

| tmav123 | 0:9df942ea84f4 | 113 | #define CCxxx0_SIDLE 0x36 // Exit RX / TX, turn off frequency synthesizer and exit |

| hillkim7 | 1:e96096a7b90b | 114 | // Wake-On-Radio mode if applicable. |

| tmav123 | 0:9df942ea84f4 | 115 | #define CCxxx0_SAFC 0x37 // Perform AFC adjustment of the frequency synthesizer |

| tmav123 | 0:9df942ea84f4 | 116 | #define CCxxx0_SWOR 0x38 // Start automatic RX polling sequence (Wake-on-Radio) |

| tmav123 | 0:9df942ea84f4 | 117 | #define CCxxx0_SPWD 0x39 // Enter power down mode when CSn goes high. |

| tmav123 | 0:9df942ea84f4 | 118 | #define CCxxx0_SFRX 0x3A // Flush the RX FIFO buffer. |

| tmav123 | 0:9df942ea84f4 | 119 | #define CCxxx0_SFTX 0x3B // Flush the TX FIFO buffer. |

| tmav123 | 0:9df942ea84f4 | 120 | #define CCxxx0_SWORRST 0x3C // Reset real time clock. |

| tmav123 | 0:9df942ea84f4 | 121 | #define CCxxx0_SNOP 0x3D // No operation. May be used to pad strobe commands to two |

| hillkim7 | 1:e96096a7b90b | 122 | // bytes for simpler software. |

| tmav123 | 0:9df942ea84f4 | 123 | |

| tmav123 | 0:9df942ea84f4 | 124 | #define CCxxx0_PARTNUM 0x30 |

| tmav123 | 0:9df942ea84f4 | 125 | #define CCxxx0_VERSION 0x31 |

| tmav123 | 0:9df942ea84f4 | 126 | #define CCxxx0_FREQEST 0x32 |

| tmav123 | 0:9df942ea84f4 | 127 | #define CCxxx0_LQI 0x33 |

| tmav123 | 0:9df942ea84f4 | 128 | #define CCxxx0_RSSI 0x34 |

| tmav123 | 0:9df942ea84f4 | 129 | #define CCxxx0_MARCSTATE 0x35 |

| tmav123 | 0:9df942ea84f4 | 130 | #define CCxxx0_WORTIME1 0x36 |

| tmav123 | 0:9df942ea84f4 | 131 | #define CCxxx0_WORTIME0 0x37 |

| tmav123 | 0:9df942ea84f4 | 132 | #define CCxxx0_PKTSTATUS 0x38 |

| tmav123 | 0:9df942ea84f4 | 133 | #define CCxxx0_VCO_VC_DAC 0x39 |

| tmav123 | 0:9df942ea84f4 | 134 | #define CCxxx0_TXBYTES 0x3A |

| tmav123 | 0:9df942ea84f4 | 135 | #define CCxxx0_RXBYTES 0x3B |

| tmav123 | 0:9df942ea84f4 | 136 | #define CCxxx0_RCCTRL1_STATUS 0x3C |

| tmav123 | 0:9df942ea84f4 | 137 | #define CCxxx0_RCCTRL0_STATUS 0x3D |

| tmav123 | 0:9df942ea84f4 | 138 | |

| tmav123 | 0:9df942ea84f4 | 139 | #define CCxxx0_PATABLE 0x3E |

| tmav123 | 0:9df942ea84f4 | 140 | #define CCxxx0_TXFIFO 0x3F |

| tmav123 | 0:9df942ea84f4 | 141 | #define CCxxx0_RXFIFO 0x3F |

| tmav123 | 0:9df942ea84f4 | 142 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 143 | // RF_SETTINGS is a data structure which contains all relevant CCxxx0 registers |

| hillkim7 | 1:e96096a7b90b | 144 | typedef struct S_RF_SETTINGS { |

| tmav123 | 0:9df942ea84f4 | 145 | unsigned char FSCTRL1; // Frequency synthesizer control. |

| tmav123 | 0:9df942ea84f4 | 146 | unsigned char IOCFG0; // GDO0 output pin configuration |

| tmav123 | 0:9df942ea84f4 | 147 | unsigned char FSCTRL0; // Frequency synthesizer control. |

| tmav123 | 0:9df942ea84f4 | 148 | unsigned char FREQ2; // Frequency control word, high byte. |

| tmav123 | 0:9df942ea84f4 | 149 | unsigned char FREQ1; // Frequency control word, middle byte. |

| tmav123 | 0:9df942ea84f4 | 150 | unsigned char FREQ0; // Frequency control word, low byte. |

| tmav123 | 0:9df942ea84f4 | 151 | unsigned char MDMCFG4; // Modem configuration. |

| tmav123 | 0:9df942ea84f4 | 152 | unsigned char MDMCFG3; // Modem configuration. |

| tmav123 | 0:9df942ea84f4 | 153 | unsigned char MDMCFG2; // Modem configuration. |

| tmav123 | 0:9df942ea84f4 | 154 | unsigned char MDMCFG1; // Modem configuration. |

| tmav123 | 0:9df942ea84f4 | 155 | unsigned char MDMCFG0; // Modem configuration. |

| tmav123 | 0:9df942ea84f4 | 156 | unsigned char CHANNR; // Channel number. |

| tmav123 | 0:9df942ea84f4 | 157 | unsigned char DEVIATN; // Modem deviation setting (when FSK modulation is enabled). |

| tmav123 | 0:9df942ea84f4 | 158 | unsigned char FREND1; // Front end RX configuration. |

| tmav123 | 0:9df942ea84f4 | 159 | unsigned char FREND0; // Front end RX configuration. |

| tmav123 | 0:9df942ea84f4 | 160 | unsigned char MCSM0; // Main Radio Control State Machine configuration. |

| tmav123 | 0:9df942ea84f4 | 161 | unsigned char FOCCFG; // Frequency Offset Compensation Configuration. |

| tmav123 | 0:9df942ea84f4 | 162 | unsigned char BSCFG; // Bit synchronization Configuration. |

| tmav123 | 0:9df942ea84f4 | 163 | unsigned char AGCCTRL2; // AGC control. |

| tmav123 | 0:9df942ea84f4 | 164 | unsigned char AGCCTRL1; // AGC control. |

| tmav123 | 0:9df942ea84f4 | 165 | unsigned char AGCCTRL0; // AGC control. |

| tmav123 | 0:9df942ea84f4 | 166 | unsigned char FSCAL3; // Frequency synthesizer calibration. |

| tmav123 | 0:9df942ea84f4 | 167 | unsigned char FSCAL2; // Frequency synthesizer calibration. |

| tmav123 | 0:9df942ea84f4 | 168 | unsigned char FSCAL1; // Frequency synthesizer calibration. |

| tmav123 | 0:9df942ea84f4 | 169 | unsigned char FSCAL0; // Frequency synthesizer calibration. |

| tmav123 | 0:9df942ea84f4 | 170 | unsigned char FSTEST; // Frequency synthesizer calibration control |

| tmav123 | 0:9df942ea84f4 | 171 | unsigned char TEST2; // Various test settings. |

| tmav123 | 0:9df942ea84f4 | 172 | unsigned char TEST1; // Various test settings. |

| tmav123 | 0:9df942ea84f4 | 173 | unsigned char TEST0; // Various test settings. |

| tmav123 | 0:9df942ea84f4 | 174 | unsigned char FIFOTHR; // RXFIFO and TXFIFO thresholds. |

| tmav123 | 0:9df942ea84f4 | 175 | unsigned char IOCFG2; // GDO2 output pin configuration |

| tmav123 | 0:9df942ea84f4 | 176 | unsigned char PKTCTRL1; // Packet automation control. |

| tmav123 | 0:9df942ea84f4 | 177 | unsigned char PKTCTRL0; // Packet automation control. |

| tmav123 | 0:9df942ea84f4 | 178 | unsigned char ADDR; // Device address. |

| tmav123 | 0:9df942ea84f4 | 179 | unsigned char PKTLEN; // Packet length. |

| tmav123 | 0:9df942ea84f4 | 180 | unsigned char MCSM1; // Main Radio Control State Machine configuration. |

| tmav123 | 0:9df942ea84f4 | 181 | } RF_SETTINGS; |

| tmav123 | 0:9df942ea84f4 | 182 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 183 | // Definitions to support burst/single access: |

| tmav123 | 0:9df942ea84f4 | 184 | #define WRITE_BURST 0x40 |

| tmav123 | 0:9df942ea84f4 | 185 | #define READ_SINGLE 0x80 |

| tmav123 | 0:9df942ea84f4 | 186 | #define READ_BURST 0xC0 |

| tmav123 | 0:9df942ea84f4 | 187 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 188 | #define CRC_OK 0x80 |

| tmav123 | 0:9df942ea84f4 | 189 | #define RSSI 0 |

| tmav123 | 0:9df942ea84f4 | 190 | #define LQI 1 |

| tmav123 | 0:9df942ea84f4 | 191 | #define BYTES_IN_RXFIFO 0x7F |

| tmav123 | 0:9df942ea84f4 | 192 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 193 | // Definitions for chip status |

| tmav123 | 0:9df942ea84f4 | 194 | #define CHIP_RDY 0x80 |

| tmav123 | 0:9df942ea84f4 | 195 | #define CHIP_STATE_MASK 0x70 |

| tmav123 | 0:9df942ea84f4 | 196 | #define CHIP_STATE_IDLE 0x00 |

| tmav123 | 0:9df942ea84f4 | 197 | #define CHIP_STATE_RX 0x10 |

| tmav123 | 0:9df942ea84f4 | 198 | #define CHIP_STATE_TX 0x20 |

| tmav123 | 0:9df942ea84f4 | 199 | #define CHIP_STATE_FSTON 0x30 |

| tmav123 | 0:9df942ea84f4 | 200 | #define CHIP_STATE_CALIBRATE 0x40 |

| tmav123 | 0:9df942ea84f4 | 201 | #define CHIP_STATE_SETTLING 0x50 |

| tmav123 | 0:9df942ea84f4 | 202 | #define CHIP_STATE_RXFIFO_OVERFLOW 0x60 |

| tmav123 | 0:9df942ea84f4 | 203 | #define CHIP_STATE_TXFIFO_UNDERFLOW 0x70 |

| tmav123 | 0:9df942ea84f4 | 204 | #define FIFO_BYTES_MASK 0x0F |

| tmav123 | 0:9df942ea84f4 | 205 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 206 | /** |

| tmav123 | 0:9df942ea84f4 | 207 | * CC1101 Low-Power Sub-1 GHz RF Transceiver . |

| tmav123 | 0:9df942ea84f4 | 208 | */ |

| tmav123 | 0:9df942ea84f4 | 209 | |

| hillkim7 | 1:e96096a7b90b | 210 | class CC1101 |

| tmav123 | 0:9df942ea84f4 | 211 | { |

| tmav123 | 0:9df942ea84f4 | 212 | public: |

| tmav123 | 0:9df942ea84f4 | 213 | /** |

| tmav123 | 0:9df942ea84f4 | 214 | * Constructor. |

| tmav123 | 0:9df942ea84f4 | 215 | * |

| tmav123 | 0:9df942ea84f4 | 216 | * @param mosi mbed pin to use for MOSI line of SPI interface. |

| tmav123 | 0:9df942ea84f4 | 217 | * @param miso mbed pin to use for MISO line of SPI interface. |

| tmav123 | 0:9df942ea84f4 | 218 | * @param clk mbed pin to use for SCK line of SPI interface. |

| tmav123 | 0:9df942ea84f4 | 219 | * @param csn mbed pin to use for not chip select line of SPI interface. |

| tmav123 | 0:9df942ea84f4 | 220 | * @param RDmiso mbed pin connected to SPI MISO pin for CC1101 RDY read. |

| tmav123 | 0:9df942ea84f4 | 221 | */ |

| hillkim7 | 1:e96096a7b90b | 222 | CC1101(PinName mosi, PinName miso, PinName clk, PinName csn, PinName RDmiso, PinName gdo0, PinName gdo1); |

| tmav123 | 0:9df942ea84f4 | 223 | |

| tmav123 | 0:9df942ea84f4 | 224 | /** |

| tmav123 | 0:9df942ea84f4 | 225 | * Initialize CC1101 parameters. |

| tmav123 | 0:9df942ea84f4 | 226 | */ |

| tmav123 | 0:9df942ea84f4 | 227 | void init(void); |

| tmav123 | 0:9df942ea84f4 | 228 | |

| tmav123 | 0:9df942ea84f4 | 229 | /** |

| tmav123 | 0:9df942ea84f4 | 230 | * This function gets the value of a single specified CCxxx0 register. |

| tmav123 | 0:9df942ea84f4 | 231 | * |

| tmav123 | 0:9df942ea84f4 | 232 | * @param addr Value of the accessed CCxxx0 register |

| tmav123 | 0:9df942ea84f4 | 233 | * @return Value of the accessed CCxxx0 register |

| tmav123 | 0:9df942ea84f4 | 234 | */ |

| tmav123 | 0:9df942ea84f4 | 235 | unsigned char ReadReg(unsigned char addr); |

| tmav123 | 0:9df942ea84f4 | 236 | |

| tmav123 | 0:9df942ea84f4 | 237 | /** |

| tmav123 | 0:9df942ea84f4 | 238 | * This function reads multiple CCxxx0 register, using SPI burst access. |

| tmav123 | 0:9df942ea84f4 | 239 | * |

| tmav123 | 0:9df942ea84f4 | 240 | * @param addr Value of the accessed CCxxx0 register |

| tmav123 | 0:9df942ea84f4 | 241 | * @param *buffer Pointer to a byte array which stores the values read from a |

| tmav123 | 0:9df942ea84f4 | 242 | * corresponding range of CCxxx0 registers. |

| tmav123 | 0:9df942ea84f4 | 243 | * @param count Number of bytes to be read from the subsequent CCxxx0 registers. |

| tmav123 | 0:9df942ea84f4 | 244 | */ |

| tmav123 | 0:9df942ea84f4 | 245 | void ReadBurstReg(unsigned char addr, unsigned char *buffer, unsigned char count); |

| tmav123 | 0:9df942ea84f4 | 246 | |

| tmav123 | 0:9df942ea84f4 | 247 | /** |

| tmav123 | 0:9df942ea84f4 | 248 | * Function for writing to a single CCxxx0 register |

| tmav123 | 0:9df942ea84f4 | 249 | * |

| tmav123 | 0:9df942ea84f4 | 250 | * @param addr Address of the first CCxxx0 register to be accessed. |

| tmav123 | 0:9df942ea84f4 | 251 | * @param value Value to be written to the specified CCxxx0 register. |

| tmav123 | 0:9df942ea84f4 | 252 | */ |

| tmav123 | 0:9df942ea84f4 | 253 | void WriteReg(unsigned char addr, unsigned char value); |

| tmav123 | 0:9df942ea84f4 | 254 | |

| tmav123 | 0:9df942ea84f4 | 255 | /** |

| tmav123 | 0:9df942ea84f4 | 256 | * This function writes to multiple CCxxx0 register, using SPI burst access. |

| tmav123 | 0:9df942ea84f4 | 257 | * |

| tmav123 | 0:9df942ea84f4 | 258 | * @param addr Address of the first CCxxx0 register to be accessed. |

| tmav123 | 0:9df942ea84f4 | 259 | * @param *buffer Array of bytes to be written into a corresponding range of |

| tmav123 | 0:9df942ea84f4 | 260 | * CCxx00 registers, starting by the address specified in _addr_. |

| tmav123 | 0:9df942ea84f4 | 261 | * @param count Number of bytes to be written to the subsequent CCxxx0 registers. |

| tmav123 | 0:9df942ea84f4 | 262 | */ |

| tmav123 | 0:9df942ea84f4 | 263 | void WriteBurstReg(unsigned char addr, unsigned char *buffer, unsigned char count); |

| tmav123 | 0:9df942ea84f4 | 264 | |

| tmav123 | 0:9df942ea84f4 | 265 | /** |

| tmav123 | 0:9df942ea84f4 | 266 | * This function can be used to transmit a packet with packet length up to 63 bytes. |

| tmav123 | 0:9df942ea84f4 | 267 | * |

| tmav123 | 0:9df942ea84f4 | 268 | * @param *txBuffer Pointer to a buffer containing the data that are going to be transmitted |

| tmav123 | 0:9df942ea84f4 | 269 | * @param size The size of the txBuffer |

| tmav123 | 0:9df942ea84f4 | 270 | */ |

| hillkim7 | 1:e96096a7b90b | 271 | void SendPacket(const unsigned char *txBuffer, unsigned char size); |

| tmav123 | 0:9df942ea84f4 | 272 | |

| tmav123 | 0:9df942ea84f4 | 273 | /** |

| tmav123 | 0:9df942ea84f4 | 274 | * This function check if the TX FIFO is empty |

| tmav123 | 0:9df942ea84f4 | 275 | * |

| tmav123 | 0:9df942ea84f4 | 276 | * @return Return value is 1 if the TX FIFO buffer is empty or else 0 |

| tmav123 | 0:9df942ea84f4 | 277 | */ |

| tmav123 | 0:9df942ea84f4 | 278 | unsigned char TxFifoEmpty(void); |

| tmav123 | 0:9df942ea84f4 | 279 | |

| tmav123 | 0:9df942ea84f4 | 280 | /** |

| tmav123 | 0:9df942ea84f4 | 281 | * This function can be used to receive a packet of variable packet length (first byte in the packet |

| tmav123 | 0:9df942ea84f4 | 282 | * must be the length byte). The packet length should not exceed the RX FIFO size. |

| tmav123 | 0:9df942ea84f4 | 283 | * |

| tmav123 | 0:9df942ea84f4 | 284 | * @param *rxBuffer Pointer to the buffer where the incoming data should be stored |

| tmav123 | 0:9df942ea84f4 | 285 | * @param *length Pointer to a variable containing the size of the buffer where the incoming data should be |

| tmav123 | 0:9df942ea84f4 | 286 | * stored. After this function returns, that variable holds the packet length. |

| tmav123 | 0:9df942ea84f4 | 287 | * @return Return value is 1 if CRC OK or else 0 if CRC NOT OK (or no packet was put in the RX FIFO due to filtering) |

| tmav123 | 0:9df942ea84f4 | 288 | */ |

| tmav123 | 0:9df942ea84f4 | 289 | int ReceivePacket(unsigned char *rxBuffer, unsigned char *length); |

| tmav123 | 0:9df942ea84f4 | 290 | |

| tmav123 | 0:9df942ea84f4 | 291 | /** |

| tmav123 | 0:9df942ea84f4 | 292 | * This function check if the RX FIFO is empty |

| tmav123 | 0:9df942ea84f4 | 293 | * |

| tmav123 | 0:9df942ea84f4 | 294 | * @return Return value is 1 if the RX FIFO buffer is empty or else 0 |

| tmav123 | 0:9df942ea84f4 | 295 | */ |

| tmav123 | 0:9df942ea84f4 | 296 | unsigned char RxFifoEmpty(void); |

| tmav123 | 0:9df942ea84f4 | 297 | |

| tmav123 | 0:9df942ea84f4 | 298 | /** |

| tmav123 | 0:9df942ea84f4 | 299 | * This function returns the Chip Status RX register |

| tmav123 | 0:9df942ea84f4 | 300 | * |

| tmav123 | 0:9df942ea84f4 | 301 | * @return Return the Chip Status RX register |

| tmav123 | 0:9df942ea84f4 | 302 | */ |

| tmav123 | 0:9df942ea84f4 | 303 | unsigned char ReadChipStatusRX(void); |

| tmav123 | 0:9df942ea84f4 | 304 | |

| tmav123 | 0:9df942ea84f4 | 305 | /** |

| tmav123 | 0:9df942ea84f4 | 306 | * This function returns the Chip Status TX register |

| tmav123 | 0:9df942ea84f4 | 307 | * |

| tmav123 | 0:9df942ea84f4 | 308 | * @return Return the Chip Status TX register |

| tmav123 | 0:9df942ea84f4 | 309 | */ |

| tmav123 | 0:9df942ea84f4 | 310 | unsigned char ReadChipStatusTX(void); |

| tmav123 | 0:9df942ea84f4 | 311 | |

| tmav123 | 0:9df942ea84f4 | 312 | /** |

| tmav123 | 0:9df942ea84f4 | 313 | * This function returns the RSSI value based from the last packet received |

| tmav123 | 0:9df942ea84f4 | 314 | * |

| tmav123 | 0:9df942ea84f4 | 315 | * @return Return the RSSI value. |

| tmav123 | 0:9df942ea84f4 | 316 | */ |

| tmav123 | 0:9df942ea84f4 | 317 | unsigned char RdRSSI(void); |

| tmav123 | 0:9df942ea84f4 | 318 | |

| tmav123 | 0:9df942ea84f4 | 319 | /** |

| tmav123 | 0:9df942ea84f4 | 320 | * This function returns the LQI value based from the last packet received |

| tmav123 | 0:9df942ea84f4 | 321 | * |

| tmav123 | 0:9df942ea84f4 | 322 | * @return Return the LQI value. |

| tmav123 | 0:9df942ea84f4 | 323 | */ |

| tmav123 | 0:9df942ea84f4 | 324 | unsigned char RdLQI(void); |

| tmav123 | 0:9df942ea84f4 | 325 | |

| tmav123 | 0:9df942ea84f4 | 326 | /** |

| tmav123 | 0:9df942ea84f4 | 327 | * This function flushes the RX FIFO buffer. |

| tmav123 | 0:9df942ea84f4 | 328 | */ |

| tmav123 | 0:9df942ea84f4 | 329 | void FlushRX(void); |

| tmav123 | 0:9df942ea84f4 | 330 | |

| tmav123 | 0:9df942ea84f4 | 331 | /** |

| tmav123 | 0:9df942ea84f4 | 332 | * This function flushes the TX FIFO buffer. |

| tmav123 | 0:9df942ea84f4 | 333 | */ |

| tmav123 | 0:9df942ea84f4 | 334 | void FlushTX(void); |

| tmav123 | 0:9df942ea84f4 | 335 | |

| tmav123 | 0:9df942ea84f4 | 336 | /** |

| tmav123 | 0:9df942ea84f4 | 337 | * This function change the state of CC1101 to RX mode. |

| tmav123 | 0:9df942ea84f4 | 338 | */ |

| tmav123 | 0:9df942ea84f4 | 339 | void RXMode(void); |

| tmav123 | 0:9df942ea84f4 | 340 | |

| hillkim7 | 1:e96096a7b90b | 341 | /** |

| hillkim7 | 1:e96096a7b90b | 342 | * This function return GDO0 input pin status. |

| hillkim7 | 1:e96096a7b90b | 343 | */ |

| hillkim7 | 1:e96096a7b90b | 344 | int GetGDO0(void); |

| hillkim7 | 1:e96096a7b90b | 345 | |

| hillkim7 | 1:e96096a7b90b | 346 | /** |

| hillkim7 | 1:e96096a7b90b | 347 | * This function return GDO1 input pin status. |

| hillkim7 | 1:e96096a7b90b | 348 | */ |

| hillkim7 | 1:e96096a7b90b | 349 | int GetGDO1(void); |

| hillkim7 | 1:e96096a7b90b | 350 | |

| hillkim7 | 1:e96096a7b90b | 351 | |

| hillkim7 | 1:e96096a7b90b | 352 | unsigned char ReadStatus(unsigned char addr); |

| tmav123 | 0:9df942ea84f4 | 353 | protected: |

| tmav123 | 0:9df942ea84f4 | 354 | void RESET_CCxxx0(void); |

| tmav123 | 0:9df942ea84f4 | 355 | void POWER_UP_RESET_CCxxx0(void); |

| tmav123 | 0:9df942ea84f4 | 356 | unsigned char Strobe(unsigned char strobe); |

| tmav123 | 0:9df942ea84f4 | 357 | void WriteRfSettings(RF_SETTINGS *pRfSettings); |

| hillkim7 | 1:e96096a7b90b | 358 | |

| tmav123 | 0:9df942ea84f4 | 359 | SPI _spi; |

| tmav123 | 0:9df942ea84f4 | 360 | DigitalOut _csn; |

| tmav123 | 0:9df942ea84f4 | 361 | DigitalIn _RDmiso; |

| tmav123 | 0:9df942ea84f4 | 362 | unsigned char rssi; |

| tmav123 | 0:9df942ea84f4 | 363 | unsigned char lqi; |

| hillkim7 | 1:e96096a7b90b | 364 | DigitalIn _gdo0; |

| hillkim7 | 1:e96096a7b90b | 365 | DigitalIn _gdo1; |

| tmav123 | 0:9df942ea84f4 | 366 | }; |

| tmav123 | 0:9df942ea84f4 | 367 | /////////////////////////////////////////////////////////////////////////////////////// |

| hillkim7 | 1:e96096a7b90b | 368 | #endif |

| hillkim7 | 1:e96096a7b90b | 369 |