RZ/A1H CMSIS-RTOS RTX BSP for GR-PEACH.

Dependents: GR-PEACH_Azure_Speech ImageZoomInout_Sample ImageRotaion_Sample ImageScroll_Sample ... more

Fork of R_BSP by

SSIF

The SSIF driver implements transmission and reception functionality which uses the SSIF in the RZ/A Series.

Hello World!

Import program

00001 #include "mbed.h" 00002 #include "R_BSP_Ssif.h" 00003 #include "sine_data_tbl.h" 00004 00005 //I2S send only, The upper limit of write buffer is 8. 00006 R_BSP_Ssif ssif(P4_4, P4_5, P4_7, P4_6, 0x80, 8, 0); 00007 00008 static void callback_ssif_write_end(void * p_data, int32_t result, void * p_app_data) { 00009 if (result < 0) { 00010 printf("ssif write callback error %d\n", result); 00011 } 00012 } 00013 00014 int main() { 00015 rbsp_data_conf_t ssif_write_end_conf = {&callback_ssif_write_end, NULL}; 00016 ssif_channel_cfg_t ssif_cfg; 00017 int32_t result; 00018 00019 //I2S Master, 44.1kHz, 16bit, 2ch 00020 ssif_cfg.enabled = true; 00021 ssif_cfg.int_level = 0x78; 00022 ssif_cfg.slave_mode = false; 00023 ssif_cfg.sample_freq = 44100u; 00024 ssif_cfg.clk_select = SSIF_CFG_CKS_AUDIO_X1; 00025 ssif_cfg.multi_ch = SSIF_CFG_MULTI_CH_1; 00026 ssif_cfg.data_word = SSIF_CFG_DATA_WORD_16; 00027 ssif_cfg.system_word = SSIF_CFG_SYSTEM_WORD_32; 00028 ssif_cfg.bclk_pol = SSIF_CFG_FALLING; 00029 ssif_cfg.ws_pol = SSIF_CFG_WS_LOW; 00030 ssif_cfg.padding_pol = SSIF_CFG_PADDING_LOW; 00031 ssif_cfg.serial_alignment = SSIF_CFG_DATA_FIRST; 00032 ssif_cfg.parallel_alignment = SSIF_CFG_LEFT; 00033 ssif_cfg.ws_delay = SSIF_CFG_DELAY; 00034 ssif_cfg.noise_cancel = SSIF_CFG_DISABLE_NOISE_CANCEL; 00035 ssif_cfg.tdm_mode = SSIF_CFG_DISABLE_TDM; 00036 ssif_cfg.romdec_direct.mode = SSIF_CFG_DISABLE_ROMDEC_DIRECT; 00037 ssif_cfg.romdec_direct.p_cbfunc = NULL; 00038 result = ssif.ConfigChannel(&ssif_cfg); 00039 if (result < 0) { 00040 printf("ssif config error %d\n", result); 00041 } 00042 00043 while (1) { 00044 //The upper limit of write buffer is 8. 00045 result = ssif.write((void *)sin_data_44100Hz_16bit_2ch, 00046 sizeof(sin_data_44100Hz_16bit_2ch), &ssif_write_end_conf); 00047 if (result < 0) { 00048 printf("ssif write api error %d\n", result); 00049 } 00050 } 00051 }

API

Import library

Public Member Functions |

|

| R_BSP_Ssif (PinName sck, PinName ws, PinName tx, PinName rx, uint8_t int_level=0x80, int32_t max_write_num=16, int32_t max_read_num=16) | |

|

Constructor.

|

|

| virtual | ~R_BSP_Ssif () |

|

Destructor.

|

|

| int32_t | GetSsifChNo (void) |

|

Get a value of SSIF channel number.

|

|

| bool | ConfigChannel (const ssif_channel_cfg_t *const p_ch_cfg) |

|

Save configuration to the SSIF driver.

|

|

| bool | GetStatus (uint32_t *const p_status) |

|

Get a value of SSISR register.

|

|

| int32_t | write (void *const p_data, uint32_t data_size, const rbsp_data_conf_t *const p_data_conf=NULL) |

|

Write count bytes to the file associated.

|

|

| int32_t | read (void *const p_data, uint32_t data_size, const rbsp_data_conf_t *const p_data_conf=NULL) |

|

Read count bytes to the file associated.

|

|

Protected Member Functions |

|

| void | write_init (void *handle, void *p_func_a, int32_t max_buff_num=16) |

|

Write init.

|

|

| void | read_init (void *handle, void *p_func_a, int32_t max_buff_num=16) |

|

Read init.

|

|

Interface

See the Pinout page for more details

SCUX

The SCUX module consists of a sampling rate converter, a digital volume unit, and a mixer.

The SCUX driver can perform asynchronous and synchronous sampling rate conversions using the sampling rate converter. The SCUX driver uses the DMA transfer mode to input and output audio data.

Hello World!

Import program

00001 #include "mbed.h" 00002 #include "R_BSP_Scux.h" 00003 #include "USBHostMSD.h" 00004 00005 R_BSP_Scux scux(SCUX_CH_0); 00006 00007 #define WRITE_SAMPLE_NUM (128) 00008 #define READ_SAMPLE_NUM (2048) 00009 00010 const short sin_data[WRITE_SAMPLE_NUM] = { 00011 0x0000,0x0000,0x0C8C,0x0C8C,0x18F9,0x18F9,0x2528,0x2528 00012 ,0x30FB,0x30FB,0x3C56,0x3C56,0x471C,0x471C,0x5133,0x5133 00013 ,0x5A82,0x5A82,0x62F1,0x62F1,0x6A6D,0x6A6D,0x70E2,0x70E2 00014 ,0x7641,0x7641,0x7A7C,0x7A7C,0x7D89,0x7D89,0x7F61,0x7F61 00015 ,0x7FFF,0x7FFF,0x7F61,0x7F61,0x7D89,0x7D89,0x7A7C,0x7A7C 00016 ,0x7641,0x7641,0x70E2,0x70E2,0x6A6D,0x6A6D,0x62F1,0x62F1 00017 ,0x5A82,0x5A82,0x5133,0x5133,0x471C,0x471C,0x3C56,0x3C56 00018 ,0x30FB,0x30FB,0x2528,0x2528,0x18F9,0x18F9,0x0C8C,0x0C8C 00019 ,0x0000,0x0000,0xF374,0xF374,0xE707,0xE707,0xDAD8,0xDAD8 00020 ,0xCF05,0xCF05,0xC3AA,0xC3AA,0xB8E4,0xB8E4,0xAECD,0xAECD 00021 ,0xA57E,0xA57E,0x9D0F,0x9D0F,0x9593,0x9593,0x8F1E,0x8F1E 00022 ,0x89BF,0x89BF,0x8584,0x8584,0x8277,0x8277,0x809F,0x809F 00023 ,0x8001,0x8001,0x809F,0x809F,0x8277,0x8277,0x8584,0x8584 00024 ,0x89BF,0x89BF,0x8F1E,0x8F1E,0x9593,0x9593,0x9D0F,0x9D0F 00025 ,0xA57E,0xA57E,0xAECD,0xAECD,0xB8E4,0xB8E4,0xC3AA,0xC3AA 00026 ,0xCF05,0xCF05,0xDAD8,0xDAD8,0xE707,0xE707,0xF374,0xF374 00027 }; 00028 00029 #if defined(__ICCARM__) 00030 #pragma data_alignment=4 00031 short write_buff[WRITE_SAMPLE_NUM]@ ".mirrorram"; 00032 #pragma data_alignment=4 00033 short read_buff[READ_SAMPLE_NUM]@ ".mirrorram"; 00034 #else 00035 short write_buff[WRITE_SAMPLE_NUM] __attribute((section("NC_BSS"),aligned(4))); 00036 short read_buff[READ_SAMPLE_NUM] __attribute((section("NC_BSS"),aligned(4))); 00037 #endif 00038 00039 void scux_setup(void); 00040 void write_task(void const*); 00041 void file_output_to_usb(void); 00042 00043 int main(void) { 00044 // set up SRC parameters. 00045 scux_setup(); 00046 00047 printf("Sampling rate conversion Start.\n"); 00048 // start accepting transmit/receive requests. 00049 scux.TransStart(); 00050 00051 // create a new thread to write to SCUX. 00052 Thread writeTask(write_task, NULL, osPriorityNormal, 1024 * 4); 00053 00054 // receive request to the SCUX driver. 00055 scux.read(read_buff, sizeof(read_buff)); 00056 printf("Sampling rate conversion End.\n"); 00057 00058 // output binary file to USB port 0. 00059 file_output_to_usb(); 00060 } 00061 00062 void scux_setup(void) { 00063 scux_src_usr_cfg_t src_cfg; 00064 00065 src_cfg.src_enable = true; 00066 src_cfg.word_len = SCUX_DATA_LEN_16; 00067 src_cfg.mode_sync = true; 00068 src_cfg.input_rate = SAMPLING_RATE_48000HZ; 00069 src_cfg.output_rate = SAMPLING_RATE_96000HZ; 00070 src_cfg.select_in_data_ch[0] = SELECT_IN_DATA_CH_0; 00071 src_cfg.select_in_data_ch[1] = SELECT_IN_DATA_CH_1; 00072 00073 scux.SetSrcCfg(&src_cfg); 00074 } 00075 00076 void scux_flush_callback(int scux_ch) { 00077 // do nothing 00078 } 00079 00080 void write_task(void const*) { 00081 memcpy(write_buff, sin_data, sizeof(write_buff)); 00082 // send request to the SCUX driver. 00083 scux.write(write_buff, sizeof(write_buff)); 00084 00085 // stop the acceptance of transmit/receive requests. 00086 scux.FlushStop(&scux_flush_callback); 00087 } 00088 00089 void file_output_to_usb(void) { 00090 FILE * fp = NULL; 00091 int i; 00092 00093 USBHostMSD msd("usb"); 00094 00095 // try to connect a MSD device 00096 for(i = 0; i < 10; i++) { 00097 if (msd.connect()) { 00098 break; 00099 } 00100 wait(0.5); 00101 } 00102 00103 if (msd.connected()) { 00104 fp = fopen("/usb/scux_input.dat", "rb"); 00105 if (fp == NULL) { 00106 fp = fopen("/usb/scux_input.dat", "wb"); 00107 if (fp != NULL) { 00108 fwrite(write_buff, sizeof(short), WRITE_SAMPLE_NUM, fp); 00109 fclose(fp); 00110 printf("Output binary file(Input data) to USB.\n"); 00111 } else { 00112 printf("Failed to output binary file(Input data).\n"); 00113 } 00114 } else { 00115 printf("Binary file(Input data) exists.\n"); 00116 fclose(fp); 00117 } 00118 00119 fp = fopen("/usb/scux_output.dat", "rb"); 00120 if (fp == NULL) { 00121 fp = fopen("/usb/scux_output.dat", "wb"); 00122 if (fp != NULL) { 00123 fwrite(read_buff, sizeof(short), READ_SAMPLE_NUM, fp); 00124 fclose(fp); 00125 printf("Output binary file(Output data) to USB.\n"); 00126 } else { 00127 printf("Failed to output binary file(Output data).\n"); 00128 } 00129 } else { 00130 printf("Binary file(Output data) exists.\n"); 00131 fclose(fp); 00132 } 00133 } else { 00134 printf("Failed to connect to the USB device.\n"); 00135 } 00136 }

API

Import library

Public Member Functions |

|

| R_BSP_Scux ( scux_ch_num_t channel, uint8_t int_level=0x80, int32_t max_write_num=16, int32_t max_read_num=16) | |

|

Constructor: Initializes and opens the channel designated by the SCUX driver.

|

|

| virtual | ~R_BSP_Scux (void) |

|

Destructor: Closes the channel designated by the SCUX driver and exits.

|

|

| bool | TransStart (void) |

|

Sets up the SCUX HW and starts operation, then starts accepting write/read requests.

|

|

| bool | FlushStop (void(*const callback)(int32_t)) |

|

Stops accepting write/read requests, flushes out all data in the SCUX that is requested for transfer, then stops the HW operation.

|

|

| bool | ClearStop (void) |

|

Discards all data in the SCUX that is requested for transfer before stopping the hardware operation and stops accepting write/read requests.

|

|

| bool | SetSrcCfg (const scux_src_usr_cfg_t *const p_src_param) |

|

Sets up SRC parameters.

|

|

| bool | GetWriteStat (uint32_t *const p_write_stat) |

|

Obtains the state information of the write request.

|

|

| bool | GetReadStat (uint32_t *const p_read_stat) |

|

Obtains the state information of the read request.

|

|

| int32_t | write (void *const p_data, uint32_t data_size, const rbsp_data_conf_t *const p_data_conf=NULL) |

|

Write count bytes to the file associated.

|

|

| int32_t | read (void *const p_data, uint32_t data_size, const rbsp_data_conf_t *const p_data_conf=NULL) |

|

Read count bytes to the file associated.

|

|

Protected Member Functions |

|

| void | write_init (void *handle, void *p_func_a, int32_t max_buff_num=16) |

|

Write init.

|

|

| void | read_init (void *handle, void *p_func_a, int32_t max_buff_num=16) |

|

Read init.

|

|

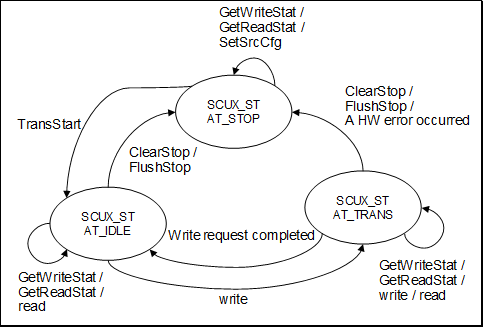

Write request state transition diagram

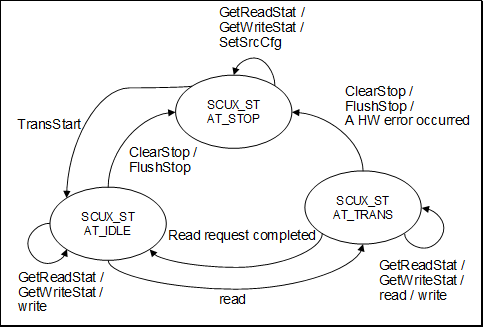

Read request state transition diagram

RenesasBSP/drv_src/ssif/ssif.h@7:30ebba78fff0, 2015-12-16 (annotated)

- Committer:

- dkato

- Date:

- Wed Dec 16 06:33:17 2015 +0000

- Revision:

- 7:30ebba78fff0

- Parent:

- 0:702bf7b2b7d8

Standardization of processing

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| dkato | 0:702bf7b2b7d8 | 1 | /******************************************************************************* |

| dkato | 0:702bf7b2b7d8 | 2 | * DISCLAIMER |

| dkato | 0:702bf7b2b7d8 | 3 | * This software is supplied by Renesas Electronics Corporation and is only |

| dkato | 0:702bf7b2b7d8 | 4 | * intended for use with Renesas products. No other uses are authorized. This |

| dkato | 0:702bf7b2b7d8 | 5 | * software is owned by Renesas Electronics Corporation and is protected under |

| dkato | 0:702bf7b2b7d8 | 6 | * all applicable laws, including copyright laws. |

| dkato | 0:702bf7b2b7d8 | 7 | * THIS SOFTWARE IS PROVIDED "AS IS" AND RENESAS MAKES NO WARRANTIES REGARDING |

| dkato | 0:702bf7b2b7d8 | 8 | * THIS SOFTWARE, WHETHER EXPRESS, IMPLIED OR STATUTORY, INCLUDING BUT NOT |

| dkato | 0:702bf7b2b7d8 | 9 | * LIMITED TO WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE |

| dkato | 0:702bf7b2b7d8 | 10 | * AND NON-INFRINGEMENT. ALL SUCH WARRANTIES ARE EXPRESSLY DISCLAIMED. |

| dkato | 0:702bf7b2b7d8 | 11 | * TO THE MAXIMUM EXTENT PERMITTED NOT PROHIBITED BY LAW, NEITHER RENESAS |

| dkato | 0:702bf7b2b7d8 | 12 | * ELECTRONICS CORPORATION NOR ANY OF ITS AFFILIATED COMPANIES SHALL BE LIABLE |

| dkato | 0:702bf7b2b7d8 | 13 | * FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES FOR |

| dkato | 0:702bf7b2b7d8 | 14 | * ANY REASON RELATED TO THIS SOFTWARE, EVEN IF RENESAS OR ITS AFFILIATES HAVE |

| dkato | 0:702bf7b2b7d8 | 15 | * BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. |

| dkato | 0:702bf7b2b7d8 | 16 | * Renesas reserves the right, without notice, to make changes to this software |

| dkato | 0:702bf7b2b7d8 | 17 | * and to discontinue the availability of this software. By using this software, |

| dkato | 0:702bf7b2b7d8 | 18 | * you agree to the additional terms and conditions found by accessing the |

| dkato | 0:702bf7b2b7d8 | 19 | * following link: |

| dkato | 0:702bf7b2b7d8 | 20 | * http://www.renesas.com/disclaimer |

| dkato | 0:702bf7b2b7d8 | 21 | * Copyright (C) 2013-2014 Renesas Electronics Corporation. All rights reserved. |

| dkato | 0:702bf7b2b7d8 | 22 | *******************************************************************************/ |

| dkato | 0:702bf7b2b7d8 | 23 | |

| dkato | 0:702bf7b2b7d8 | 24 | /****************************************************************************** |

| dkato | 0:702bf7b2b7d8 | 25 | * File Name : ssif.h |

| dkato | 0:702bf7b2b7d8 | 26 | * $Rev: 891 $ |

| dkato | 0:702bf7b2b7d8 | 27 | * $Date:: 2014-06-27 10:40:52 +0900#$ |

| dkato | 0:702bf7b2b7d8 | 28 | * Description : SSIF driver functions header |

| dkato | 0:702bf7b2b7d8 | 29 | ******************************************************************************/ |

| dkato | 0:702bf7b2b7d8 | 30 | |

| dkato | 0:702bf7b2b7d8 | 31 | #ifndef SSIF_H |

| dkato | 0:702bf7b2b7d8 | 32 | #define SSIF_H |

| dkato | 0:702bf7b2b7d8 | 33 | |

| dkato | 0:702bf7b2b7d8 | 34 | /******************************************************************************* |

| dkato | 0:702bf7b2b7d8 | 35 | Includes <System Includes>, "Project Includes" |

| dkato | 0:702bf7b2b7d8 | 36 | *******************************************************************************/ |

| dkato | 0:702bf7b2b7d8 | 37 | #include "aioif.h" |

| dkato | 0:702bf7b2b7d8 | 38 | #include "iodefine.h" |

| dkato | 0:702bf7b2b7d8 | 39 | #include "ssif_if.h" |

| dkato | 0:702bf7b2b7d8 | 40 | #include "bsp_drv_cmn.h" |

| dkato | 0:702bf7b2b7d8 | 41 | |

| dkato | 0:702bf7b2b7d8 | 42 | /****************************************************************************** |

| dkato | 0:702bf7b2b7d8 | 43 | Macro definitions |

| dkato | 0:702bf7b2b7d8 | 44 | ******************************************************************************/ |

| dkato | 0:702bf7b2b7d8 | 45 | |

| dkato | 0:702bf7b2b7d8 | 46 | #define SSIF_CHNUM_0 (0u) |

| dkato | 0:702bf7b2b7d8 | 47 | #define SSIF_CHNUM_1 (1u) |

| dkato | 0:702bf7b2b7d8 | 48 | #define SSIF_CHNUM_2 (2u) |

| dkato | 0:702bf7b2b7d8 | 49 | #define SSIF_CHNUM_3 (3u) |

| dkato | 0:702bf7b2b7d8 | 50 | #define SSIF_CHNUM_4 (4u) |

| dkato | 0:702bf7b2b7d8 | 51 | #define SSIF_CHNUM_5 (5u) |

| dkato | 0:702bf7b2b7d8 | 52 | |

| dkato | 0:702bf7b2b7d8 | 53 | #define SSIF_CHSTR_0 "\\0" |

| dkato | 0:702bf7b2b7d8 | 54 | #define SSIF_CHSTR_1 "\\1" |

| dkato | 0:702bf7b2b7d8 | 55 | #define SSIF_CHSTR_2 "\\2" |

| dkato | 0:702bf7b2b7d8 | 56 | #define SSIF_CHSTR_3 "\\3" |

| dkato | 0:702bf7b2b7d8 | 57 | #define SSIF_CHSTR_4 "\\4" |

| dkato | 0:702bf7b2b7d8 | 58 | #define SSIF_CHSTR_5 "\\5" |

| dkato | 0:702bf7b2b7d8 | 59 | |

| dkato | 0:702bf7b2b7d8 | 60 | #define SSIF_MAX_PATH_LEN (32u) |

| dkato | 0:702bf7b2b7d8 | 61 | |

| dkato | 0:702bf7b2b7d8 | 62 | #define SSIF_CR_SHIFT_CKS (30u) |

| dkato | 0:702bf7b2b7d8 | 63 | #define SSIF_CR_SHIFT_TUIEN (29u) |

| dkato | 0:702bf7b2b7d8 | 64 | #define SSIF_CR_SHIFT_TOIEN (28u) |

| dkato | 0:702bf7b2b7d8 | 65 | #define SSIF_CR_SHIFT_RUIEN (27u) |

| dkato | 0:702bf7b2b7d8 | 66 | #define SSIF_CR_SHIFT_ROIEN (26u) |

| dkato | 0:702bf7b2b7d8 | 67 | #define SSIF_CR_SHIFT_IIEN (25u) |

| dkato | 0:702bf7b2b7d8 | 68 | #define SSIF_CR_SHIFT_CHNL (22u) |

| dkato | 0:702bf7b2b7d8 | 69 | #define SSIF_CR_SHIFT_DWL (19u) |

| dkato | 0:702bf7b2b7d8 | 70 | #define SSIF_CR_SHIFT_SWL (16u) |

| dkato | 0:702bf7b2b7d8 | 71 | #define SSIF_CR_SHIFT_SCKD (15u) |

| dkato | 0:702bf7b2b7d8 | 72 | #define SSIF_CR_SHIFT_SWSD (14u) |

| dkato | 0:702bf7b2b7d8 | 73 | #define SSIF_CR_SHIFT_SCKP (13u) |

| dkato | 0:702bf7b2b7d8 | 74 | #define SSIF_CR_SHIFT_SWSP (12u) |

| dkato | 0:702bf7b2b7d8 | 75 | #define SSIF_CR_SHIFT_SPDP (11u) |

| dkato | 0:702bf7b2b7d8 | 76 | #define SSIF_CR_SHIFT_SDTA (10u) |

| dkato | 0:702bf7b2b7d8 | 77 | #define SSIF_CR_SHIFT_PDTA ( 9u) |

| dkato | 0:702bf7b2b7d8 | 78 | #define SSIF_CR_SHIFT_DEL ( 8u) |

| dkato | 0:702bf7b2b7d8 | 79 | #define SSIF_CR_SHIFT_CKDV ( 4u) |

| dkato | 0:702bf7b2b7d8 | 80 | #define SSIF_CR_SHIFT_MUEN ( 3u) |

| dkato | 0:702bf7b2b7d8 | 81 | #define SSIF_CR_SHIFT_TEN ( 1u) |

| dkato | 0:702bf7b2b7d8 | 82 | #define SSIF_CR_SHIFT_REN ( 0u) |

| dkato | 0:702bf7b2b7d8 | 83 | |

| dkato | 0:702bf7b2b7d8 | 84 | #define SSIF_CR_BIT_CKS (1u << SSIF_CR_SHIFT_CKS) |

| dkato | 0:702bf7b2b7d8 | 85 | #define SSIF_CR_BIT_TUIEN (1u << SSIF_CR_SHIFT_TUIEN) |

| dkato | 0:702bf7b2b7d8 | 86 | #define SSIF_CR_BIT_TOIEN (1u << SSIF_CR_SHIFT_TOIEN) |

| dkato | 0:702bf7b2b7d8 | 87 | #define SSIF_CR_BIT_RUIEN (1u << SSIF_CR_SHIFT_RUIEN) |

| dkato | 0:702bf7b2b7d8 | 88 | #define SSIF_CR_BIT_ROIEN (1u << SSIF_CR_SHIFT_ROIEN) |

| dkato | 0:702bf7b2b7d8 | 89 | #define SSIF_CR_BIT_IIEN (1u << SSIF_CR_SHIFT_IIEN) |

| dkato | 0:702bf7b2b7d8 | 90 | #define SSIF_CR_BITS_CHNL (3u << SSIF_CR_SHIFT_CHNL) |

| dkato | 0:702bf7b2b7d8 | 91 | #define SSIF_CR_BITS_DWL (7u << SSIF_CR_SHIFT_DWL) |

| dkato | 0:702bf7b2b7d8 | 92 | #define SSIF_CR_BITS_SWL (7u << SSIF_CR_SHIFT_SWL) |

| dkato | 0:702bf7b2b7d8 | 93 | #define SSIF_CR_BIT_SCKD (1u << SSIF_CR_SHIFT_SCKD) |

| dkato | 0:702bf7b2b7d8 | 94 | #define SSIF_CR_BIT_SWSD (1u << SSIF_CR_SHIFT_SWSD) |

| dkato | 0:702bf7b2b7d8 | 95 | #define SSIF_CR_BIT_SCKP (1u << SSIF_CR_SHIFT_SCKP) |

| dkato | 0:702bf7b2b7d8 | 96 | #define SSIF_CR_BIT_SWSP (1u << SSIF_CR_SHIFT_SWSP) |

| dkato | 0:702bf7b2b7d8 | 97 | #define SSIF_CR_BIT_SPDP (1u << SSIF_CR_SHIFT_SPDP) |

| dkato | 0:702bf7b2b7d8 | 98 | #define SSIF_CR_BIT_SDTA (1u << SSIF_CR_SHIFT_SDTA) |

| dkato | 0:702bf7b2b7d8 | 99 | #define SSIF_CR_BIT_PDTA (1u << SSIF_CR_SHIFT_PDTA) |

| dkato | 0:702bf7b2b7d8 | 100 | #define SSIF_CR_BIT_DEL (1u << SSIF_CR_SHIFT_DEL) |

| dkato | 0:702bf7b2b7d8 | 101 | #define SSIF_CR_BITS_CKDV (0xfu << SSIF_CR_SHIFT_CKDV) |

| dkato | 0:702bf7b2b7d8 | 102 | #define SSIF_CR_BIT_MUEN (1u << SSIF_CR_SHIFT_MUEN) |

| dkato | 0:702bf7b2b7d8 | 103 | #define SSIF_CR_BIT_TEN (1u << SSIF_CR_SHIFT_TEN) |

| dkato | 0:702bf7b2b7d8 | 104 | #define SSIF_CR_BIT_REN (1u << SSIF_CR_SHIFT_REN) |

| dkato | 0:702bf7b2b7d8 | 105 | #define SSIF_CR_INT_ERR_MASK (SSIF_CR_BIT_TUIEN | SSIF_CR_BIT_TOIEN | SSIF_CR_BIT_RUIEN | SSIF_CR_BIT_ROIEN) |

| dkato | 0:702bf7b2b7d8 | 106 | |

| dkato | 0:702bf7b2b7d8 | 107 | #define SSIF_SR_SHIFT_TUIRQ (29u) |

| dkato | 0:702bf7b2b7d8 | 108 | #define SSIF_SR_SHIFT_TOIRQ (28u) |

| dkato | 0:702bf7b2b7d8 | 109 | #define SSIF_SR_SHIFT_RUIRQ (27u) |

| dkato | 0:702bf7b2b7d8 | 110 | #define SSIF_SR_SHIFT_ROIRQ (26u) |

| dkato | 0:702bf7b2b7d8 | 111 | #define SSIF_SR_SHIFT_IIRQ (25u) |

| dkato | 0:702bf7b2b7d8 | 112 | #define SSIF_SR_SHIFT_IDST ( 0u) |

| dkato | 0:702bf7b2b7d8 | 113 | |

| dkato | 0:702bf7b2b7d8 | 114 | #define SSIF_SR_BIT_TUIRQ (1u << SSIF_SR_SHIFT_TUIRQ) |

| dkato | 0:702bf7b2b7d8 | 115 | #define SSIF_SR_BIT_TOIRQ (1u << SSIF_SR_SHIFT_TOIRQ) |

| dkato | 0:702bf7b2b7d8 | 116 | #define SSIF_SR_BIT_RUIRQ (1u << SSIF_SR_SHIFT_RUIRQ) |

| dkato | 0:702bf7b2b7d8 | 117 | #define SSIF_SR_BIT_ROIRQ (1u << SSIF_SR_SHIFT_ROIRQ) |

| dkato | 0:702bf7b2b7d8 | 118 | #define SSIF_SR_BIT_IIRQ (1u << SSIF_SR_SHIFT_IIRQ) |

| dkato | 0:702bf7b2b7d8 | 119 | #define SSIF_SR_BIT_IDST (1u << SSIF_SR_SHIFT_IDST) |

| dkato | 0:702bf7b2b7d8 | 120 | #define SSIF_SR_INT_ERR_MASK (SSIF_SR_BIT_TUIRQ | SSIF_SR_BIT_TOIRQ | SSIF_SR_BIT_RUIRQ | SSIF_SR_BIT_ROIRQ) |

| dkato | 0:702bf7b2b7d8 | 121 | |

| dkato | 0:702bf7b2b7d8 | 122 | #define SSIF_FCR_SHIFT_TIE (3u) |

| dkato | 0:702bf7b2b7d8 | 123 | #define SSIF_FCR_SHIFT_RIE (2u) |

| dkato | 0:702bf7b2b7d8 | 124 | #define SSIF_FCR_SHIFT_TFRST (1u) |

| dkato | 0:702bf7b2b7d8 | 125 | #define SSIF_FCR_SHIFT_RFRST (0u) |

| dkato | 0:702bf7b2b7d8 | 126 | |

| dkato | 0:702bf7b2b7d8 | 127 | #define SSIF_FCR_BIT_TIE (1u << SSIF_FCR_SHIFT_TIE) |

| dkato | 0:702bf7b2b7d8 | 128 | #define SSIF_FCR_BIT_RIE (1u << SSIF_FCR_SHIFT_RIE) |

| dkato | 0:702bf7b2b7d8 | 129 | #define SSIF_FCR_BIT_TFRST (1u << SSIF_FCR_SHIFT_TFRST) |

| dkato | 0:702bf7b2b7d8 | 130 | #define SSIF_FCR_BIT_RFRST (1u << SSIF_FCR_SHIFT_RFRST) |

| dkato | 0:702bf7b2b7d8 | 131 | |

| dkato | 0:702bf7b2b7d8 | 132 | #define SSIF_TDMR_SHIFT_CONT (8u) |

| dkato | 0:702bf7b2b7d8 | 133 | #define SSIF_TDMR_SHIFT_TDM (0u) |

| dkato | 0:702bf7b2b7d8 | 134 | |

| dkato | 0:702bf7b2b7d8 | 135 | #define SSIF_TDMR_BIT_CONT (1u << SSIF_TDMR_SHIFT_CONT) |

| dkato | 0:702bf7b2b7d8 | 136 | #define SSIF_TDMR_BIT_TDM (1u << SSIF_TDMR_SHIFT_TDM) |

| dkato | 0:702bf7b2b7d8 | 137 | |

| dkato | 0:702bf7b2b7d8 | 138 | /* noise canceled bit */ |

| dkato | 0:702bf7b2b7d8 | 139 | #define GPIO_SNCR_BIT_SSI5NCE (1u << 5) |

| dkato | 0:702bf7b2b7d8 | 140 | #define GPIO_SNCR_BIT_SSI4NCE (1u << 4) |

| dkato | 0:702bf7b2b7d8 | 141 | #define GPIO_SNCR_BIT_SSI3NCE (1u << 3) |

| dkato | 0:702bf7b2b7d8 | 142 | #define GPIO_SNCR_BIT_SSI2NCE (1u << 2) |

| dkato | 0:702bf7b2b7d8 | 143 | #define GPIO_SNCR_BIT_SSI1NCE (1u << 1) |

| dkato | 0:702bf7b2b7d8 | 144 | #define GPIO_SNCR_BIT_SSI0NCE (1u << 0) |

| dkato | 0:702bf7b2b7d8 | 145 | |

| dkato | 0:702bf7b2b7d8 | 146 | /****************************************************************************** |

| dkato | 0:702bf7b2b7d8 | 147 | Private global variables and functions |

| dkato | 0:702bf7b2b7d8 | 148 | ******************************************************************************/ |

| dkato | 0:702bf7b2b7d8 | 149 | |

| dkato | 0:702bf7b2b7d8 | 150 | /************************************************************************* |

| dkato | 0:702bf7b2b7d8 | 151 | Enumerated Types |

| dkato | 0:702bf7b2b7d8 | 152 | *************************************************************************/ |

| dkato | 0:702bf7b2b7d8 | 153 | typedef enum { |

| dkato | 0:702bf7b2b7d8 | 154 | SSIF_DRVSTS_UNINIT = 0, |

| dkato | 0:702bf7b2b7d8 | 155 | SSIF_DRVSTS_INIT |

| dkato | 0:702bf7b2b7d8 | 156 | } ssif_drv_stat_t; |

| dkato | 0:702bf7b2b7d8 | 157 | |

| dkato | 0:702bf7b2b7d8 | 158 | typedef enum |

| dkato | 0:702bf7b2b7d8 | 159 | { |

| dkato | 0:702bf7b2b7d8 | 160 | SSIF_CHSTS_UNINIT = 0, |

| dkato | 0:702bf7b2b7d8 | 161 | SSIF_CHSTS_INIT, |

| dkato | 0:702bf7b2b7d8 | 162 | SSIF_CHSTS_OPEN |

| dkato | 0:702bf7b2b7d8 | 163 | } ssif_ch_stat_t; |

| dkato | 0:702bf7b2b7d8 | 164 | |

| dkato | 0:702bf7b2b7d8 | 165 | typedef enum |

| dkato | 0:702bf7b2b7d8 | 166 | { |

| dkato | 0:702bf7b2b7d8 | 167 | SSIF_ASYNC_W = 0, |

| dkato | 0:702bf7b2b7d8 | 168 | SSIF_ASYNC_R |

| dkato | 0:702bf7b2b7d8 | 169 | } ssif_rw_mode_t; |

| dkato | 0:702bf7b2b7d8 | 170 | |

| dkato | 0:702bf7b2b7d8 | 171 | /** Serial bit clock direction */ |

| dkato | 0:702bf7b2b7d8 | 172 | typedef enum |

| dkato | 0:702bf7b2b7d8 | 173 | { |

| dkato | 0:702bf7b2b7d8 | 174 | SSIF_CFG_CLOCK_IN = 0, /**< Clock IN - Slave mode */ |

| dkato | 0:702bf7b2b7d8 | 175 | SSIF_CFG_CLOCK_OUT = 1 /**< Clock OUT - Master mode */ |

| dkato | 0:702bf7b2b7d8 | 176 | } ssif_chcfg_clock_dir_t; |

| dkato | 0:702bf7b2b7d8 | 177 | |

| dkato | 0:702bf7b2b7d8 | 178 | |

| dkato | 0:702bf7b2b7d8 | 179 | /** Serial word select direction */ |

| dkato | 0:702bf7b2b7d8 | 180 | typedef enum |

| dkato | 0:702bf7b2b7d8 | 181 | { |

| dkato | 0:702bf7b2b7d8 | 182 | SSIF_CFG_WS_IN = 0, /**< Word select IN - Slave mode */ |

| dkato | 0:702bf7b2b7d8 | 183 | SSIF_CFG_WS_OUT = 1 /**< Word select OUT - Master mode */ |

| dkato | 0:702bf7b2b7d8 | 184 | } ssif_chcfg_ws_dir_t; |

| dkato | 0:702bf7b2b7d8 | 185 | |

| dkato | 0:702bf7b2b7d8 | 186 | |

| dkato | 0:702bf7b2b7d8 | 187 | /************************************************************************* |

| dkato | 0:702bf7b2b7d8 | 188 | Structures |

| dkato | 0:702bf7b2b7d8 | 189 | *************************************************************************/ |

| dkato | 0:702bf7b2b7d8 | 190 | typedef struct ssif_info_ch |

| dkato | 0:702bf7b2b7d8 | 191 | { |

| dkato | 0:702bf7b2b7d8 | 192 | uint32_t channel; |

| dkato | 0:702bf7b2b7d8 | 193 | bool_t enabled; |

| dkato | 0:702bf7b2b7d8 | 194 | bool_t slave_mode; |

| dkato | 0:702bf7b2b7d8 | 195 | uint32_t sample_freq; |

| dkato | 0:702bf7b2b7d8 | 196 | ssif_ch_stat_t ch_stat; |

| dkato | 0:702bf7b2b7d8 | 197 | osSemaphoreId sem_access; |

| dkato | 0:702bf7b2b7d8 | 198 | AHF_S tx_que; |

| dkato | 0:702bf7b2b7d8 | 199 | AHF_S rx_que; |

| dkato | 0:702bf7b2b7d8 | 200 | int_t dma_rx_ch; |

| dkato | 0:702bf7b2b7d8 | 201 | int_t dma_tx_ch; |

| dkato | 0:702bf7b2b7d8 | 202 | bool_t is_full_duplex; /* full/half duplex */ |

| dkato | 0:702bf7b2b7d8 | 203 | int_t openflag; |

| dkato | 0:702bf7b2b7d8 | 204 | AIOCB* p_aio_tx_curr; |

| dkato | 0:702bf7b2b7d8 | 205 | AIOCB* p_aio_tx_next; |

| dkato | 0:702bf7b2b7d8 | 206 | AIOCB* p_aio_rx_curr; |

| dkato | 0:702bf7b2b7d8 | 207 | AIOCB* p_aio_rx_next; |

| dkato | 0:702bf7b2b7d8 | 208 | ssif_chcfg_cks_t clk_select; |

| dkato | 0:702bf7b2b7d8 | 209 | ssif_chcfg_multi_ch_t multi_ch; |

| dkato | 0:702bf7b2b7d8 | 210 | ssif_chcfg_data_word_t data_word; |

| dkato | 0:702bf7b2b7d8 | 211 | ssif_chcfg_system_word_t system_word; |

| dkato | 0:702bf7b2b7d8 | 212 | ssif_chcfg_clock_dir_t clock_direction; |

| dkato | 0:702bf7b2b7d8 | 213 | ssif_chcfg_ws_dir_t ws_direction; |

| dkato | 0:702bf7b2b7d8 | 214 | ssif_chcfg_clock_pol_t bclk_pol; |

| dkato | 0:702bf7b2b7d8 | 215 | ssif_chcfg_ws_pol_t ws_pol; |

| dkato | 0:702bf7b2b7d8 | 216 | ssif_chcfg_padding_pol_t padding_pol; |

| dkato | 0:702bf7b2b7d8 | 217 | ssif_chcfg_serial_alignment_t serial_alignment; |

| dkato | 0:702bf7b2b7d8 | 218 | ssif_chcfg_parallel_alignment_t parallel_alignment; |

| dkato | 0:702bf7b2b7d8 | 219 | ssif_chcfg_ws_delay_t ws_delay; |

| dkato | 0:702bf7b2b7d8 | 220 | ssif_chcfg_noise_cancel_t noise_cancel; |

| dkato | 0:702bf7b2b7d8 | 221 | ssif_chcfg_tdm_t tdm_mode; |

| dkato | 0:702bf7b2b7d8 | 222 | ssif_chcfg_ckdv_t clk_div; |

| dkato | 0:702bf7b2b7d8 | 223 | ssif_chcfg_romdec_t romdec_direct; |

| dkato | 0:702bf7b2b7d8 | 224 | } ssif_info_ch_t; |

| dkato | 0:702bf7b2b7d8 | 225 | |

| dkato | 0:702bf7b2b7d8 | 226 | |

| dkato | 0:702bf7b2b7d8 | 227 | typedef struct ssif_info_drv |

| dkato | 0:702bf7b2b7d8 | 228 | { |

| dkato | 0:702bf7b2b7d8 | 229 | ssif_drv_stat_t drv_stat; |

| dkato | 0:702bf7b2b7d8 | 230 | ssif_info_ch_t info_ch[SSIF_NUM_CHANS]; |

| dkato | 0:702bf7b2b7d8 | 231 | } ssif_info_drv_t; |

| dkato | 0:702bf7b2b7d8 | 232 | |

| dkato | 0:702bf7b2b7d8 | 233 | extern volatile struct st_ssif* const g_ssireg[SSIF_NUM_CHANS]; |

| dkato | 0:702bf7b2b7d8 | 234 | |

| dkato | 0:702bf7b2b7d8 | 235 | /****************************************************************************** |

| dkato | 0:702bf7b2b7d8 | 236 | Function Prototypes |

| dkato | 0:702bf7b2b7d8 | 237 | *****************************************************************************/ |

| dkato | 0:702bf7b2b7d8 | 238 | #if(1) /* mbed */ |

| dkato | 0:702bf7b2b7d8 | 239 | int_t SSIF_InitialiseOne(const int_t channel, const ssif_channel_cfg_t* const p_cfg_data); |

| dkato | 0:702bf7b2b7d8 | 240 | int_t SSIF_UnInitialiseOne(const int_t channel); |

| dkato | 7:30ebba78fff0 | 241 | #endif /* end mbed */ |

| dkato | 0:702bf7b2b7d8 | 242 | int_t SSIF_Initialise(const ssif_channel_cfg_t* const p_cfg_data); |

| dkato | 0:702bf7b2b7d8 | 243 | int_t SSIF_UnInitialise(void); |

| dkato | 0:702bf7b2b7d8 | 244 | int_t SSIF_EnableChannel(ssif_info_ch_t* const p_info_ch); |

| dkato | 0:702bf7b2b7d8 | 245 | int_t SSIF_DisableChannel(ssif_info_ch_t* const p_info_ch); |

| dkato | 0:702bf7b2b7d8 | 246 | void SSIF_ErrorRecovery(ssif_info_ch_t* const p_info_ch); |

| dkato | 0:702bf7b2b7d8 | 247 | |

| dkato | 0:702bf7b2b7d8 | 248 | void SSIF_PostAsyncIo(ssif_info_ch_t* const p_info_ch, AIOCB* const p_aio); |

| dkato | 0:702bf7b2b7d8 | 249 | void SSIF_PostAsyncCancel(ssif_info_ch_t* const p_info_ch, AIOCB* const p_aio); |

| dkato | 0:702bf7b2b7d8 | 250 | |

| dkato | 0:702bf7b2b7d8 | 251 | int_t SSIF_IOCTL_ConfigChannel(ssif_info_ch_t* const p_info_ch, |

| dkato | 0:702bf7b2b7d8 | 252 | const ssif_channel_cfg_t* const p_ch_cfg); |

| dkato | 0:702bf7b2b7d8 | 253 | int_t SSIF_IOCTL_GetStatus(const ssif_info_ch_t* const p_info_ch, uint32_t* const p_status); |

| dkato | 0:702bf7b2b7d8 | 254 | |

| dkato | 0:702bf7b2b7d8 | 255 | int_t SSIF_InitDMA(ssif_info_ch_t* const p_info_ch); |

| dkato | 0:702bf7b2b7d8 | 256 | void SSIF_UnInitDMA(ssif_info_ch_t* const p_info_ch); |

| dkato | 0:702bf7b2b7d8 | 257 | void SSIF_CancelDMA(const ssif_info_ch_t* const p_info_ch); |

| dkato | 0:702bf7b2b7d8 | 258 | int_t SSIF_RestartDMA(ssif_info_ch_t* const p_info_ch); |

| dkato | 0:702bf7b2b7d8 | 259 | |

| dkato | 0:702bf7b2b7d8 | 260 | int_t SSIF_SWLtoLen(const ssif_chcfg_system_word_t ssicr_swl); |

| dkato | 0:702bf7b2b7d8 | 261 | int_t SSIF_DWLtoLen(const ssif_chcfg_data_word_t ssicr_dwl); |

| dkato | 0:702bf7b2b7d8 | 262 | |

| dkato | 0:702bf7b2b7d8 | 263 | extern ssif_info_drv_t g_ssif_info_drv; |

| dkato | 0:702bf7b2b7d8 | 264 | |

| dkato | 0:702bf7b2b7d8 | 265 | #endif /* SSIF_H */ |