Temporary Connector Reversed Version

Dependencies: UniGraphic mbed vt100

afero_poc15_180403R , J1 のピン配置を反転させたヴァージョンです。

Color2系を使用するためには以下のピンをジャンパで接続してください。

J1-D7 <-> J1-D0

J1-D6 <-> J1-D1

(調査中) また、こちらでテストした範囲では、

FRDM-KL25Z の V3.3 を、Modulo2 の VCC_3V3 ピンに接続してやる必要がありました。

尚、J1-D1, D0 を使用するために UART を無効にしているため

ログは表示されません。

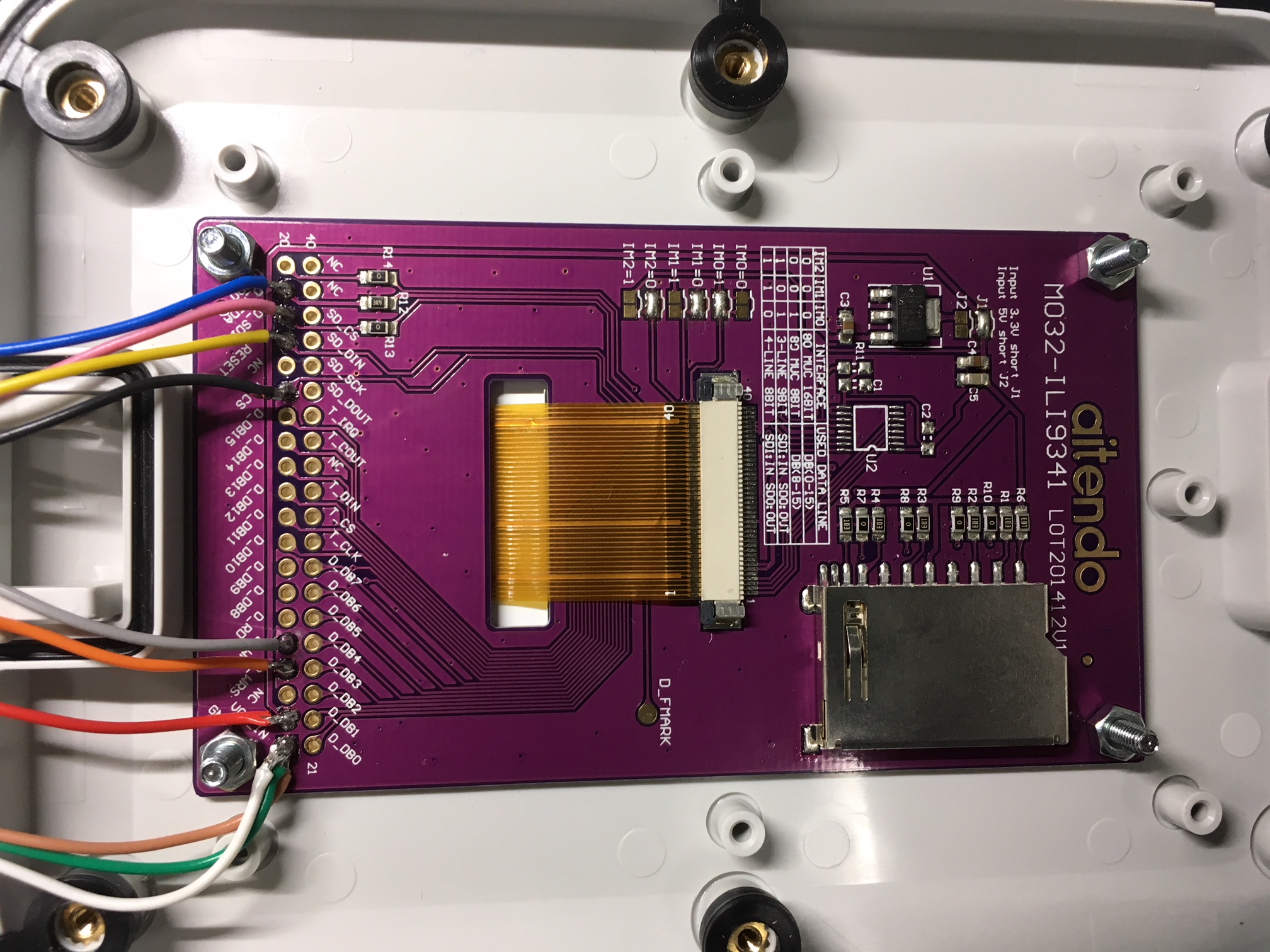

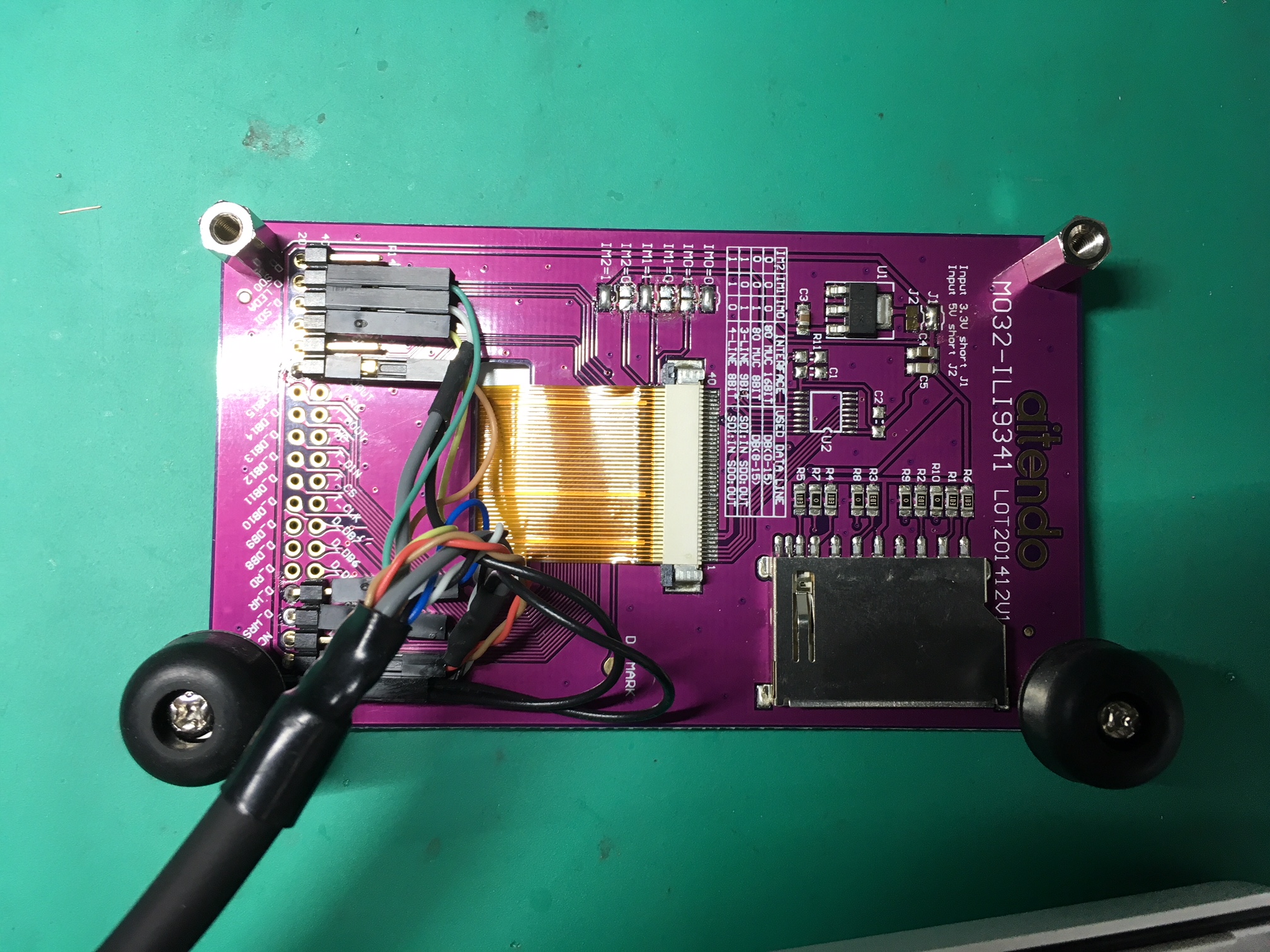

TFTモジュールについて

aitendoのTFTモジュールはデフォルトでは8bit bus モードになっています。

半田のジャンパを変えて、SPIの設定にしてください。

サーミスタについて

POC1.5 では サーミスタは 25℃の時に抵抗値が 50.0kΩになる502AT-11 が

4.95kΩのプルアップ(実際は10kΩx2の並列)で使用されていました。

今回の試作では抵抗値が 10.0kΩの 103AT-11 が

5.1kΩのプルアップで使用されていますので、係数を合わせるために

SMTC502AT-11 のコンストラクタを

R0 = 10.0

R1 = 5.1

B = 3435

T0 = 298.15

で呼ぶように変更しました。

edge_utils/edge_reset_mgr.cpp@1:6c54dc8acf96, 2018-04-24 (annotated)

- Committer:

- Rhyme

- Date:

- Tue Apr 24 12:18:10 2018 +0000

- Revision:

- 1:6c54dc8acf96

- Parent:

- 0:0b6732b53bf4

to adjust with 103AT-11 with 5.1k pull-up, the constructor of 502AT-11 is called with R0=10.0, R1=5.1, B=3435, T0=298.15

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| Rhyme | 0:0b6732b53bf4 | 1 | #include "mbed.h" |

| Rhyme | 0:0b6732b53bf4 | 2 | #include "edge_reset_mgr.h" |

| Rhyme | 0:0b6732b53bf4 | 3 | |

| Rhyme | 0:0b6732b53bf4 | 4 | /** |

| Rhyme | 0:0b6732b53bf4 | 5 | * System Reset Status Register 0 (RCM_SRS0) 0x4007_F000 |

| Rhyme | 0:0b6732b53bf4 | 6 | * |

| Rhyme | 0:0b6732b53bf4 | 7 | * bit[7] : POR Power-On Reset |

| Rhyme | 0:0b6732b53bf4 | 8 | * bit[6] : PIN External Reset Pin |

| Rhyme | 0:0b6732b53bf4 | 9 | * bit[5] : WDOG Watchdog |

| Rhyme | 0:0b6732b53bf4 | 10 | * bit[4] : (Reserved) |

| Rhyme | 0:0b6732b53bf4 | 11 | * bit[3] : LOL Loss-of-Lock Reset |

| Rhyme | 0:0b6732b53bf4 | 12 | * bit[2] : LOC Loss-of-Clock Reset |

| Rhyme | 0:0b6732b53bf4 | 13 | * bit[1] : LVD Low-Voltage Detect Reset |

| Rhyme | 0:0b6732b53bf4 | 14 | * bit[0] : WAKEUP Low Leakage Wakeup Reset |

| Rhyme | 0:0b6732b53bf4 | 15 | */ |

| Rhyme | 0:0b6732b53bf4 | 16 | #define REG_RCM_SRS0 (uint8_t *)0x4007F000 |

| Rhyme | 0:0b6732b53bf4 | 17 | #define POR_RESET_BIT 0x80 |

| Rhyme | 0:0b6732b53bf4 | 18 | #define PIN_RESET_BIT 0x40 |

| Rhyme | 0:0b6732b53bf4 | 19 | #define WDG_RESET_BIT 0x20 |

| Rhyme | 0:0b6732b53bf4 | 20 | #define LOL_RESET_BIT 0x08 |

| Rhyme | 0:0b6732b53bf4 | 21 | #define LOC_RESET_BIT 0x04 |

| Rhyme | 0:0b6732b53bf4 | 22 | #define LVD_RESET_BIT 0x02 |

| Rhyme | 0:0b6732b53bf4 | 23 | #define WUP_RESET_BIT 0x01 |

| Rhyme | 0:0b6732b53bf4 | 24 | |

| Rhyme | 0:0b6732b53bf4 | 25 | /** |

| Rhyme | 0:0b6732b53bf4 | 26 | * System Reset Status Register 1 (RCM_SRS1) 0x4007_F001 |

| Rhyme | 0:0b6732b53bf4 | 27 | * |

| Rhyme | 0:0b6732b53bf4 | 28 | * bit[7:6] (Reserved) |

| Rhyme | 0:0b6732b53bf4 | 29 | * bit[5] : SACKERR Stop Mode Acknowledge Error Reset |

| Rhyme | 0:0b6732b53bf4 | 30 | * bit[4] : (Reserved) |

| Rhyme | 0:0b6732b53bf4 | 31 | * bit[3] : MDM_AP MDM-AP System Reset Request |

| Rhyme | 0:0b6732b53bf4 | 32 | * bit[2] : SW Software Reset |

| Rhyme | 0:0b6732b53bf4 | 33 | * bit[1] : LOCKUP Core Lockup |

| Rhyme | 0:0b6732b53bf4 | 34 | * bit[0] : (Reserved) |

| Rhyme | 0:0b6732b53bf4 | 35 | */ |

| Rhyme | 0:0b6732b53bf4 | 36 | #define REG_RCM_SRS1 (uint8_t *)0x4007F001 |

| Rhyme | 0:0b6732b53bf4 | 37 | #define SACK_RESET_BIT 0x20 |

| Rhyme | 0:0b6732b53bf4 | 38 | #define MDM_RESET_BIT 0x08 |

| Rhyme | 0:0b6732b53bf4 | 39 | #define SW_RESET_BIT 0x04 |

| Rhyme | 0:0b6732b53bf4 | 40 | #define LOCKUP_RESET_BIT 0x02 |

| Rhyme | 0:0b6732b53bf4 | 41 | |

| Rhyme | 0:0b6732b53bf4 | 42 | #define IDX_POR_RESET 0 |

| Rhyme | 0:0b6732b53bf4 | 43 | #define IDX_PIN_RESET 1 |

| Rhyme | 0:0b6732b53bf4 | 44 | #define IDX_WDG_RESET 2 |

| Rhyme | 0:0b6732b53bf4 | 45 | #define IDX_LOL_RESET 3 |

| Rhyme | 0:0b6732b53bf4 | 46 | #define IDX_LOC_RESET 4 |

| Rhyme | 0:0b6732b53bf4 | 47 | #define IDX_LVD_RESET 5 |

| Rhyme | 0:0b6732b53bf4 | 48 | #define IDX_WUP_RESET 6 |

| Rhyme | 0:0b6732b53bf4 | 49 | #define IDX_SACK_RESET 7 |

| Rhyme | 0:0b6732b53bf4 | 50 | #define IDX_MDM_RESET 8 |

| Rhyme | 0:0b6732b53bf4 | 51 | #define IDX_SW_RESET 9 |

| Rhyme | 0:0b6732b53bf4 | 52 | #define IDX_LOCKUP_RESET 10 |

| Rhyme | 0:0b6732b53bf4 | 53 | |

| Rhyme | 0:0b6732b53bf4 | 54 | const char *reset_reason[] = { |

| Rhyme | 0:0b6732b53bf4 | 55 | "Power On Reset", |

| Rhyme | 0:0b6732b53bf4 | 56 | "Reset Pin Asserted", |

| Rhyme | 0:0b6732b53bf4 | 57 | "Watch Dog Reset", |

| Rhyme | 0:0b6732b53bf4 | 58 | "Loss of Lock Reset", |

| Rhyme | 0:0b6732b53bf4 | 59 | "Loss of Clock Reset", |

| Rhyme | 0:0b6732b53bf4 | 60 | "Low Voltage Detect Reset", |

| Rhyme | 0:0b6732b53bf4 | 61 | "Low Leakage Wakeup Reset", |

| Rhyme | 0:0b6732b53bf4 | 62 | "Stop Mode Acknowledge Error Reset", |

| Rhyme | 0:0b6732b53bf4 | 63 | "MDM-AP System Reset Request", |

| Rhyme | 0:0b6732b53bf4 | 64 | "Software Reset", |

| Rhyme | 0:0b6732b53bf4 | 65 | "Core Lockup Reset", |

| Rhyme | 0:0b6732b53bf4 | 66 | 0 |

| Rhyme | 0:0b6732b53bf4 | 67 | } ; |

| Rhyme | 0:0b6732b53bf4 | 68 | |

| Rhyme | 0:0b6732b53bf4 | 69 | void print_reset_reason(void) |

| Rhyme | 0:0b6732b53bf4 | 70 | { |

| Rhyme | 0:0b6732b53bf4 | 71 | extern char *reset_reason_str ; |

| Rhyme | 0:0b6732b53bf4 | 72 | int idx = 0 ; |

| Rhyme | 0:0b6732b53bf4 | 73 | uint8_t *data = REG_RCM_SRS0 ; |

| Rhyme | 0:0b6732b53bf4 | 74 | if (*data & POR_RESET_BIT) { |

| Rhyme | 0:0b6732b53bf4 | 75 | idx = IDX_POR_RESET ; |

| Rhyme | 0:0b6732b53bf4 | 76 | } |

| Rhyme | 0:0b6732b53bf4 | 77 | if (*data & PIN_RESET_BIT) { |

| Rhyme | 0:0b6732b53bf4 | 78 | idx = IDX_PIN_RESET ; |

| Rhyme | 0:0b6732b53bf4 | 79 | } |

| Rhyme | 0:0b6732b53bf4 | 80 | if (*data & WDG_RESET_BIT) { |

| Rhyme | 0:0b6732b53bf4 | 81 | idx = IDX_WDG_RESET ; |

| Rhyme | 0:0b6732b53bf4 | 82 | } |

| Rhyme | 0:0b6732b53bf4 | 83 | if (*data & LOL_RESET_BIT) { |

| Rhyme | 0:0b6732b53bf4 | 84 | idx = IDX_LOL_RESET ; |

| Rhyme | 0:0b6732b53bf4 | 85 | } |

| Rhyme | 0:0b6732b53bf4 | 86 | if (*data & LVD_RESET_BIT) { |

| Rhyme | 0:0b6732b53bf4 | 87 | idx = IDX_LVD_RESET ; |

| Rhyme | 0:0b6732b53bf4 | 88 | } |

| Rhyme | 0:0b6732b53bf4 | 89 | if (*data & LOC_RESET_BIT) { |

| Rhyme | 0:0b6732b53bf4 | 90 | idx = IDX_LOC_RESET ; |

| Rhyme | 0:0b6732b53bf4 | 91 | } |

| Rhyme | 0:0b6732b53bf4 | 92 | if (*data & WUP_RESET_BIT) { |

| Rhyme | 0:0b6732b53bf4 | 93 | idx = IDX_WUP_RESET ; |

| Rhyme | 0:0b6732b53bf4 | 94 | } |

| Rhyme | 0:0b6732b53bf4 | 95 | data = REG_RCM_SRS1 ; |

| Rhyme | 0:0b6732b53bf4 | 96 | if (*data & SACK_RESET_BIT) { |

| Rhyme | 0:0b6732b53bf4 | 97 | idx = IDX_SACK_RESET ; |

| Rhyme | 0:0b6732b53bf4 | 98 | } |

| Rhyme | 0:0b6732b53bf4 | 99 | if (*data & MDM_RESET_BIT) { |

| Rhyme | 0:0b6732b53bf4 | 100 | idx = IDX_MDM_RESET ; |

| Rhyme | 0:0b6732b53bf4 | 101 | } |

| Rhyme | 0:0b6732b53bf4 | 102 | if (*data & SW_RESET_BIT) { |

| Rhyme | 0:0b6732b53bf4 | 103 | idx = IDX_SW_RESET ; |

| Rhyme | 0:0b6732b53bf4 | 104 | } |

| Rhyme | 0:0b6732b53bf4 | 105 | if (*data & LOCKUP_RESET_BIT) { |

| Rhyme | 0:0b6732b53bf4 | 106 | idx = IDX_LOCKUP_RESET ; |

| Rhyme | 0:0b6732b53bf4 | 107 | } |

| Rhyme | 0:0b6732b53bf4 | 108 | printf("%s\n", reset_reason[idx]) ; |

| Rhyme | 0:0b6732b53bf4 | 109 | reset_reason_str = (char *)reset_reason[idx] ; |

| Rhyme | 0:0b6732b53bf4 | 110 | } |

| Rhyme | 0:0b6732b53bf4 | 111 | |

| Rhyme | 0:0b6732b53bf4 | 112 | /** |

| Rhyme | 0:0b6732b53bf4 | 113 | * Software Reset |

| Rhyme | 0:0b6732b53bf4 | 114 | * |

| Rhyme | 0:0b6732b53bf4 | 115 | * From Cortex-M0 Devices Generic User Guide |

| Rhyme | 0:0b6732b53bf4 | 116 | * 4.3.4 Application Interrupt and Reset Control Register |

| Rhyme | 0:0b6732b53bf4 | 117 | * |

| Rhyme | 0:0b6732b53bf4 | 118 | * Bit[31:16] : VECTCKEY |

| Rhyme | 0:0b6732b53bf4 | 119 | * Bit[15] : ENDIANESS |

| Rhyme | 0:0b6732b53bf4 | 120 | * Bit[14:3] : (Reserved) |

| Rhyme | 0:0b6732b53bf4 | 121 | * Bit[2] : SYSRESETREQ |

| Rhyme | 0:0b6732b53bf4 | 122 | * Bit[1] : VECTCLRACTIVE (reserved for debug use) |

| Rhyme | 0:0b6732b53bf4 | 123 | * Bit[0] : (Reserved) |

| Rhyme | 0:0b6732b53bf4 | 124 | * |

| Rhyme | 0:0b6732b53bf4 | 125 | * Note: To trigger software reset, both VECTKEY=0x05FA and SYSRESETREQ |

| Rhyme | 0:0b6732b53bf4 | 126 | * must be written at once, therefore the value will be |

| Rhyme | 0:0b6732b53bf4 | 127 | * 0x05FA0004 |

| Rhyme | 0:0b6732b53bf4 | 128 | */ |

| Rhyme | 0:0b6732b53bf4 | 129 | |

| Rhyme | 0:0b6732b53bf4 | 130 | void software_reset(void) |

| Rhyme | 0:0b6732b53bf4 | 131 | { |

| Rhyme | 0:0b6732b53bf4 | 132 | SCB->AIRCR = 0x05FA0004 ; |

| Rhyme | 0:0b6732b53bf4 | 133 | } |

| Rhyme | 0:0b6732b53bf4 | 134 | |

| Rhyme | 0:0b6732b53bf4 | 135 | /** |

| Rhyme | 0:0b6732b53bf4 | 136 | * reset_watch_dog |

| Rhyme | 0:0b6732b53bf4 | 137 | * reset the watch dog counter |

| Rhyme | 0:0b6732b53bf4 | 138 | * this function must be called within the limit (1sec) |

| Rhyme | 0:0b6732b53bf4 | 139 | */ |

| Rhyme | 0:0b6732b53bf4 | 140 | |

| Rhyme | 0:0b6732b53bf4 | 141 | void reset_watch_dog(void) |

| Rhyme | 0:0b6732b53bf4 | 142 | { |

| Rhyme | 0:0b6732b53bf4 | 143 | SIM->SRVCOP = (uint32_t)0x55u; |

| Rhyme | 0:0b6732b53bf4 | 144 | SIM->SRVCOP = (uint32_t)0xAAu; |

| Rhyme | 0:0b6732b53bf4 | 145 | } |

La Suno

La Suno