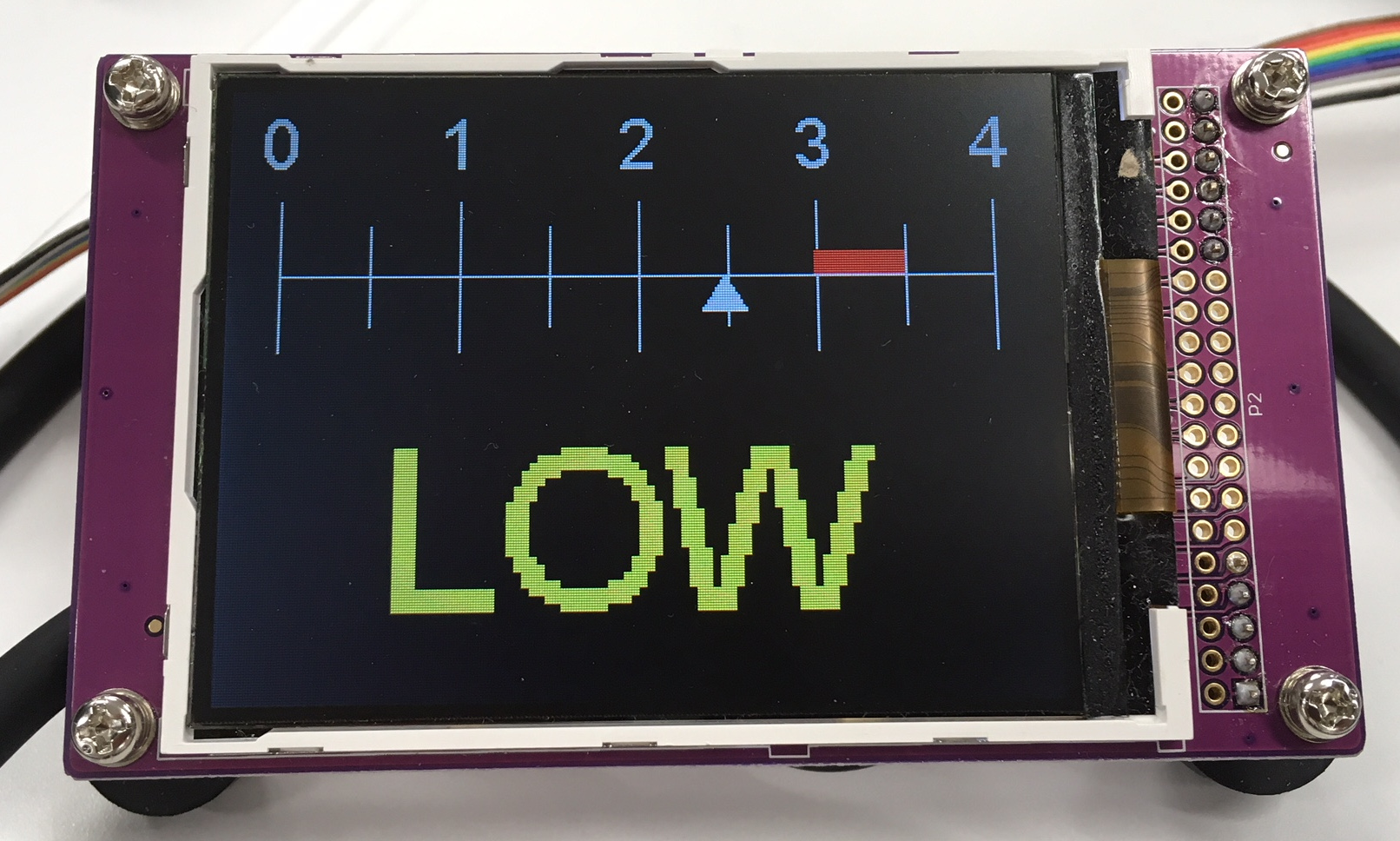

Release candidate version. The pointer in GAS Pressure display is changed to a triangle.

Dependencies: UniGraphic mbed vt100

Please note, at 2-Mar-2018 the current version of mbed-lib has a defect in Ticker.

https://os.mbed.com/forum/bugs-suggestions/topic/29287/

So, mbed lib version 157 is intentionally being used.

Please do not update mbed library until the problem in the above URL is fixed.

In this version, format of GAS Pressure Display has been changed.

moto

sensors/LM75B.cpp@0:774324cbc5a6, 2018-03-02 (annotated)

- Committer:

- Rhyme

- Date:

- Fri Mar 02 07:56:09 2018 +0000

- Revision:

- 0:774324cbc5a6

Release candidate version. GAS Pressure pointer is now a triangle.; Some source file clean-up was done.

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| Rhyme | 0:774324cbc5a6 | 1 | #include "mbed.h" |

| Rhyme | 0:774324cbc5a6 | 2 | #include "LM75B.h" |

| Rhyme | 0:774324cbc5a6 | 3 | #include "af_mgr.h" |

| Rhyme | 0:774324cbc5a6 | 4 | |

| Rhyme | 0:774324cbc5a6 | 5 | /* Register list */ |

| Rhyme | 0:774324cbc5a6 | 6 | #define PTR_CONF 0x01 |

| Rhyme | 0:774324cbc5a6 | 7 | #define PTR_TEMP 0x00 |

| Rhyme | 0:774324cbc5a6 | 8 | #define PTR_TOS 0x03 |

| Rhyme | 0:774324cbc5a6 | 9 | #define PTR_THYST 0x02 |

| Rhyme | 0:774324cbc5a6 | 10 | |

| Rhyme | 0:774324cbc5a6 | 11 | /* Configuration register */ |

| Rhyme | 0:774324cbc5a6 | 12 | /* B[7:5] : Reserved */ |

| Rhyme | 0:774324cbc5a6 | 13 | /* B[4:3] : OS_F_QUE[1:0] OS fault queue value */ |

| Rhyme | 0:774324cbc5a6 | 14 | #define CONFIG_QUE_1 0x00 |

| Rhyme | 0:774324cbc5a6 | 15 | #define CONFIG_QUE_2 (0x01 << 3) |

| Rhyme | 0:774324cbc5a6 | 16 | #define CONFIG_QUE_4 (0x10 << 3) |

| Rhyme | 0:774324cbc5a6 | 17 | #define CONFIG_QUE_6 (0x11 << 3) |

| Rhyme | 0:774324cbc5a6 | 18 | /* B[2] : OS_POL 0 = OS active LOW, 1 = OS active HIGH */ |

| Rhyme | 0:774324cbc5a6 | 19 | #define CONFIG_OS_POL_L 0x00 |

| Rhyme | 0:774324cbc5a6 | 20 | #define CONFIG_OS_POL_H (0x01 << 2) |

| Rhyme | 0:774324cbc5a6 | 21 | /* B[1] : OS_COMP_INT 0 = OS comparator, 1 = OS interrupt */ |

| Rhyme | 0:774324cbc5a6 | 22 | #define CONFIG_OS_COMP 0x00 |

| Rhyme | 0:774324cbc5a6 | 23 | #define CONFIG_OS_INT (0x01 << 1) |

| Rhyme | 0:774324cbc5a6 | 24 | /* B[0] : SHUTDOWN 0 = normal, 1 = shutdown */ |

| Rhyme | 0:774324cbc5a6 | 25 | #define CONFIG_NORMARL 0x00 |

| Rhyme | 0:774324cbc5a6 | 26 | #define CONFIG_SHUTDOWN 0x01 |

| Rhyme | 0:774324cbc5a6 | 27 | |

| Rhyme | 0:774324cbc5a6 | 28 | /* Temperature register */ |

| Rhyme | 0:774324cbc5a6 | 29 | /* D[15:5] = 11 bit data 0.125 * temp data */ |

| Rhyme | 0:774324cbc5a6 | 30 | /* D[4:0] : reserved */ |

| Rhyme | 0:774324cbc5a6 | 31 | |

| Rhyme | 0:774324cbc5a6 | 32 | /* Tos register */ |

| Rhyme | 0:774324cbc5a6 | 33 | /* D[15:7] = 9 bit data */ |

| Rhyme | 0:774324cbc5a6 | 34 | /* D[6:0] : reserved */ |

| Rhyme | 0:774324cbc5a6 | 35 | |

| Rhyme | 0:774324cbc5a6 | 36 | /* Thyst register */ |

| Rhyme | 0:774324cbc5a6 | 37 | /* D[15:7] = 9 ibt data */ |

| Rhyme | 0:774324cbc5a6 | 38 | /* D[6:0] : reserved */ |

| Rhyme | 0:774324cbc5a6 | 39 | |

| Rhyme | 0:774324cbc5a6 | 40 | LM75B::LM75B(I2C *i2c, int addr) : m_addr(addr<<1) { |

| Rhyme | 0:774324cbc5a6 | 41 | p_i2c = i2c ; |

| Rhyme | 0:774324cbc5a6 | 42 | p_i2c->frequency(100000); /* 100kHz */ |

| Rhyme | 0:774324cbc5a6 | 43 | // activate the peripheral |

| Rhyme | 0:774324cbc5a6 | 44 | } |

| Rhyme | 0:774324cbc5a6 | 45 | |

| Rhyme | 0:774324cbc5a6 | 46 | LM75B::~LM75B() { } |

| Rhyme | 0:774324cbc5a6 | 47 | |

| Rhyme | 0:774324cbc5a6 | 48 | int LM75B::temp(int8_t *temp) |

| Rhyme | 0:774324cbc5a6 | 49 | { |

| Rhyme | 0:774324cbc5a6 | 50 | int result ; |

| Rhyme | 0:774324cbc5a6 | 51 | char t[1] = { 0x00 } ; |

| Rhyme | 0:774324cbc5a6 | 52 | result = p_i2c->write(m_addr, t, 1, true) ; |

| Rhyme | 0:774324cbc5a6 | 53 | if (result == 0) { |

| Rhyme | 0:774324cbc5a6 | 54 | result = p_i2c->read(m_addr, t, 1) ; |

| Rhyme | 0:774324cbc5a6 | 55 | } |

| Rhyme | 0:774324cbc5a6 | 56 | if (result == 0) { |

| Rhyme | 0:774324cbc5a6 | 57 | *temp = (int8_t)t[0] ; |

| Rhyme | 0:774324cbc5a6 | 58 | } |

| Rhyme | 0:774324cbc5a6 | 59 | return( result ) ; |

| Rhyme | 0:774324cbc5a6 | 60 | } |

| Rhyme | 0:774324cbc5a6 | 61 | |

| Rhyme | 0:774324cbc5a6 | 62 | int LM75B::getTemp(float *temp) |

| Rhyme | 0:774324cbc5a6 | 63 | { |

| Rhyme | 0:774324cbc5a6 | 64 | int result ; |

| Rhyme | 0:774324cbc5a6 | 65 | char t[2] = { 0, 0 } ; |

| Rhyme | 0:774324cbc5a6 | 66 | int16_t iTemp = 0 ; |

| Rhyme | 0:774324cbc5a6 | 67 | result = p_i2c->write(m_addr, t, 1) ; /* write pointer byte 0x00 */ |

| Rhyme | 0:774324cbc5a6 | 68 | if (result == 0) { |

| Rhyme | 0:774324cbc5a6 | 69 | result = p_i2c->read(m_addr, t, 2) ; /* read MSB, LSB */ |

| Rhyme | 0:774324cbc5a6 | 70 | } |

| Rhyme | 0:774324cbc5a6 | 71 | if (result == 0) { |

| Rhyme | 0:774324cbc5a6 | 72 | iTemp = (t[0] << 8) | t[1] ; |

| Rhyme | 0:774324cbc5a6 | 73 | iTemp >>= 5 ; |

| Rhyme | 0:774324cbc5a6 | 74 | *temp = 0.125 * iTemp ; |

| Rhyme | 0:774324cbc5a6 | 75 | } |

| Rhyme | 0:774324cbc5a6 | 76 | return( result ) ; |

| Rhyme | 0:774324cbc5a6 | 77 | } |

| Rhyme | 0:774324cbc5a6 | 78 | |

| Rhyme | 0:774324cbc5a6 | 79 | int LM75B::getConfig(uint8_t ptr_byte, uint8_t *config_data) |

| Rhyme | 0:774324cbc5a6 | 80 | { |

| Rhyme | 0:774324cbc5a6 | 81 | int result ; |

| Rhyme | 0:774324cbc5a6 | 82 | char config = 0x00 ; /* default value */ |

| Rhyme | 0:774324cbc5a6 | 83 | result = p_i2c->write(m_addr, (char*)(&ptr_byte), 1, true) ; |

| Rhyme | 0:774324cbc5a6 | 84 | if (result == 0) { |

| Rhyme | 0:774324cbc5a6 | 85 | result = p_i2c->read(m_addr, &config, 1) ; |

| Rhyme | 0:774324cbc5a6 | 86 | } |

| Rhyme | 0:774324cbc5a6 | 87 | if (result == 0) { |

| Rhyme | 0:774324cbc5a6 | 88 | *config_data = config ; |

| Rhyme | 0:774324cbc5a6 | 89 | } |

| Rhyme | 0:774324cbc5a6 | 90 | return( result ) ; |

| Rhyme | 0:774324cbc5a6 | 91 | } |

| Rhyme | 0:774324cbc5a6 | 92 | |

| Rhyme | 0:774324cbc5a6 | 93 | int LM75B::setConfig(uint8_t ptr_byte, uint8_t config_data) |

| Rhyme | 0:774324cbc5a6 | 94 | { |

| Rhyme | 0:774324cbc5a6 | 95 | int result ; |

| Rhyme | 0:774324cbc5a6 | 96 | char t[2] ; |

| Rhyme | 0:774324cbc5a6 | 97 | t[0] = ptr_byte ; |

| Rhyme | 0:774324cbc5a6 | 98 | t[1] = config_data ; |

| Rhyme | 0:774324cbc5a6 | 99 | result = p_i2c->write(m_addr, t, 2, true) ; |

| Rhyme | 0:774324cbc5a6 | 100 | return( result ) ; |

| Rhyme | 0:774324cbc5a6 | 101 | } |

| Rhyme | 0:774324cbc5a6 | 102 | |

| Rhyme | 0:774324cbc5a6 | 103 | int LM75B::readRegs(int addr, uint8_t * data, int len) |

| Rhyme | 0:774324cbc5a6 | 104 | { |

| Rhyme | 0:774324cbc5a6 | 105 | int result ; |

| Rhyme | 0:774324cbc5a6 | 106 | char t[1] = {addr}; |

| Rhyme | 0:774324cbc5a6 | 107 | __disable_irq() ; // Disable Interrupts |

| Rhyme | 0:774324cbc5a6 | 108 | result = p_i2c->write(m_addr, t, 1, true); |

| Rhyme | 0:774324cbc5a6 | 109 | if (result == 0) { |

| Rhyme | 0:774324cbc5a6 | 110 | result = p_i2c->read(m_addr, (char *)data, len); |

| Rhyme | 0:774324cbc5a6 | 111 | } |

| Rhyme | 0:774324cbc5a6 | 112 | __enable_irq() ; // Enable Interrupts |

| Rhyme | 0:774324cbc5a6 | 113 | return( result ) ; |

| Rhyme | 0:774324cbc5a6 | 114 | } |

| Rhyme | 0:774324cbc5a6 | 115 | |

| Rhyme | 0:774324cbc5a6 | 116 | int LM75B::writeRegs(uint8_t * data, int len) { |

| Rhyme | 0:774324cbc5a6 | 117 | int result ; |

| Rhyme | 0:774324cbc5a6 | 118 | __disable_irq() ; // Disable Interrupts |

| Rhyme | 0:774324cbc5a6 | 119 | result = p_i2c->write(m_addr, (char *)data, len); |

| Rhyme | 0:774324cbc5a6 | 120 | __enable_irq() ; // Enable Interrupts |

| Rhyme | 0:774324cbc5a6 | 121 | return( result ) ; |

| Rhyme | 0:774324cbc5a6 | 122 | } |

La Suno

La Suno