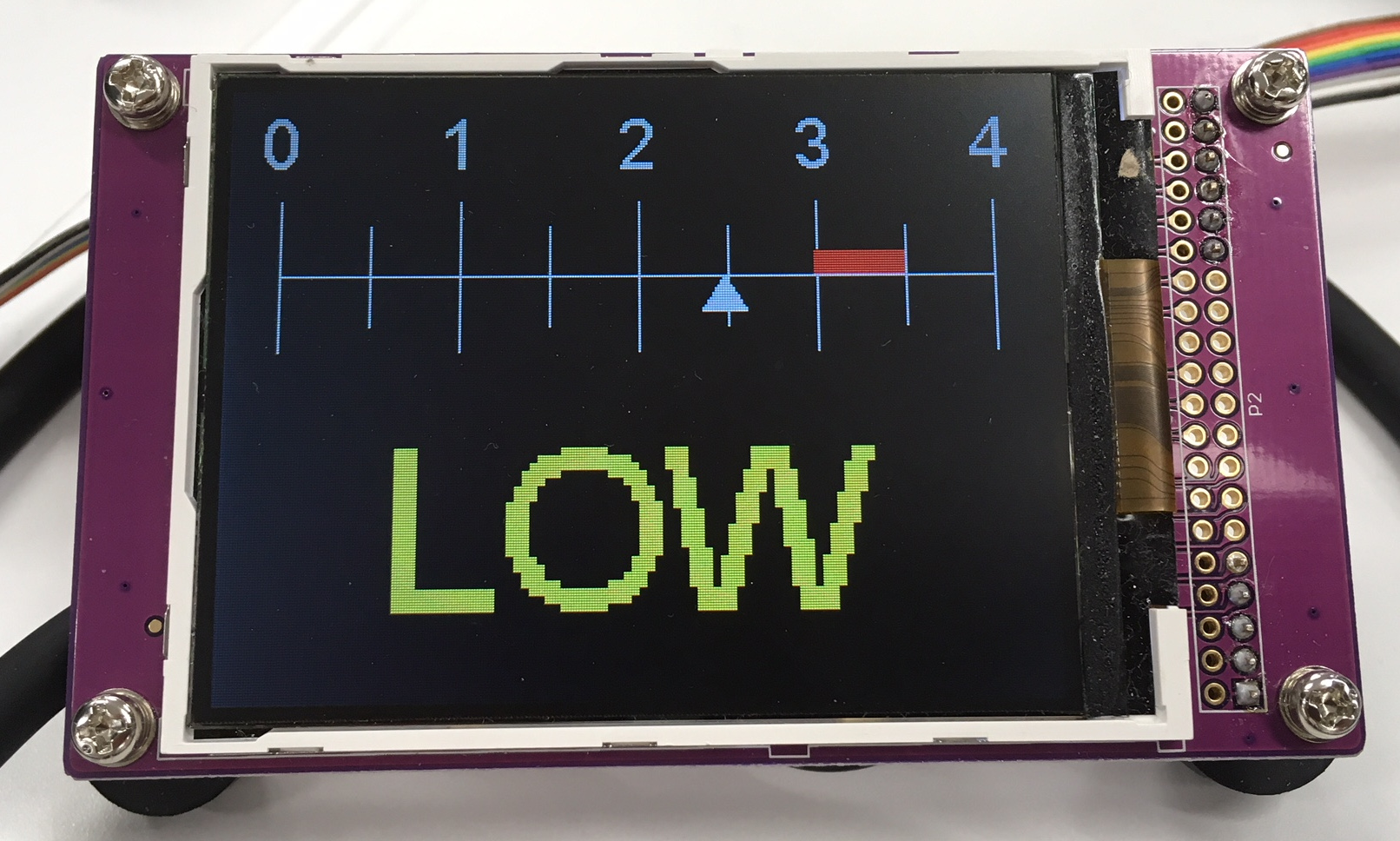

Release candidate version. The pointer in GAS Pressure display is changed to a triangle.

Dependencies: UniGraphic mbed vt100

Please note, at 2-Mar-2018 the current version of mbed-lib has a defect in Ticker.

https://os.mbed.com/forum/bugs-suggestions/topic/29287/

So, mbed lib version 157 is intentionally being used.

Please do not update mbed library until the problem in the above URL is fixed.

In this version, format of GAS Pressure Display has been changed.

moto

sensors/MMA8451Q.cpp@0:774324cbc5a6, 2018-03-02 (annotated)

- Committer:

- Rhyme

- Date:

- Fri Mar 02 07:56:09 2018 +0000

- Revision:

- 0:774324cbc5a6

Release candidate version. GAS Pressure pointer is now a triangle.; Some source file clean-up was done.

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| Rhyme | 0:774324cbc5a6 | 1 | /** |

| Rhyme | 0:774324cbc5a6 | 2 | * MMA8451Q 3-Axis, 14-bit/8-bit Digital Accelerometer |

| Rhyme | 0:774324cbc5a6 | 3 | */ |

| Rhyme | 0:774324cbc5a6 | 4 | |

| Rhyme | 0:774324cbc5a6 | 5 | #include "mbed.h" |

| Rhyme | 0:774324cbc5a6 | 6 | #include "MMA8451Q.h" |

| Rhyme | 0:774324cbc5a6 | 7 | #include "af_mgr.h" |

| Rhyme | 0:774324cbc5a6 | 8 | |

| Rhyme | 0:774324cbc5a6 | 9 | #define REG_STATUS 0x00 // when F_MODE = 00 |

| Rhyme | 0:774324cbc5a6 | 10 | #define REG_FIFO_STATUS 0x00 // when F_MODE > 0 |

| Rhyme | 0:774324cbc5a6 | 11 | #define REG_XYZ_FIFO 0x01 // Root pointer to XYZ FIFO data |

| Rhyme | 0:774324cbc5a6 | 12 | #define REG_OUT_X_MSB 0x01 // 8 MSBs of 14-bit sample |

| Rhyme | 0:774324cbc5a6 | 13 | #define REG_OUT_X_LSB 0x02 // 6 LSBs of 14-bit sample |

| Rhyme | 0:774324cbc5a6 | 14 | #define REG_OUT_Y_MSB 0x03 |

| Rhyme | 0:774324cbc5a6 | 15 | #define REG_OUT_Y_LSB 0x04 |

| Rhyme | 0:774324cbc5a6 | 16 | #define REG_OUT_Z_MSB 0x05 |

| Rhyme | 0:774324cbc5a6 | 17 | #define REG_OUT_Z_LSB 0x06 |

| Rhyme | 0:774324cbc5a6 | 18 | #define REG_F_SETUP 0x09 // FIFO setup |

| Rhyme | 0:774324cbc5a6 | 19 | #define REG_TRIG_CFG 0x0A // Map of FIFO daa capture events |

| Rhyme | 0:774324cbc5a6 | 20 | #define REG_SYSMOD 0x0B // Current System Mode |

| Rhyme | 0:774324cbc5a6 | 21 | #define REG_INT_SOURCE 0x0C // Interrupt status |

| Rhyme | 0:774324cbc5a6 | 22 | #define REG_WHO_AM_I 0x0D // Device ID (0x1A) |

| Rhyme | 0:774324cbc5a6 | 23 | #define REG_XYZ_DATA_CFG 0x0E // Dynamic Range Settings |

| Rhyme | 0:774324cbc5a6 | 24 | #define REG_HP_FILTER_CUTOFF 0x0F // Cutoff freq is set to 16Hz@800Hz |

| Rhyme | 0:774324cbc5a6 | 25 | #define REG_PL_STATUS 0x10 // Landscape/Portrait orientation status |

| Rhyme | 0:774324cbc5a6 | 26 | #define REG_PL_CFG 0x11 // Landscape/Portrait configuration |

| Rhyme | 0:774324cbc5a6 | 27 | #define REG_PL_COUNT 0x12 // Landscape/Portrait debounce counter |

| Rhyme | 0:774324cbc5a6 | 28 | #define REG_PL_BF_ZCOMP 0x13 // Back/Front, Z-Lock Trip threshold |

| Rhyme | 0:774324cbc5a6 | 29 | #define REG_P_L_THS_REG 0x14 // Portrait to Landscape Trip Angle is 29 degree |

| Rhyme | 0:774324cbc5a6 | 30 | #define REG_FF_MT_CFG 0x15 // Freefall/Motion function block configuration |

| Rhyme | 0:774324cbc5a6 | 31 | #define REG_FF_MT_SRC 0x16 // Freefall/Motion event source register |

| Rhyme | 0:774324cbc5a6 | 32 | #define REG_FF_MT_THS 0x17 // Freefall/Motion threshold register |

| Rhyme | 0:774324cbc5a6 | 33 | #define REG_FF_MT_COUNT 0x18 // Freefall/Motion debounce counter |

| Rhyme | 0:774324cbc5a6 | 34 | // TRANSIENT |

| Rhyme | 0:774324cbc5a6 | 35 | #define REG_TRANSIENT_CFG 0x1D // Transient functional block configuration |

| Rhyme | 0:774324cbc5a6 | 36 | #define REG_TRANSIENT_SRC 0x1E // Transient event status register |

| Rhyme | 0:774324cbc5a6 | 37 | #define REG_TRANSIENT_THS 0x1F // Transient event threshold |

| Rhyme | 0:774324cbc5a6 | 38 | #define REG_TRANSIENT_COUNT 0x20 // Transient debounce counter |

| Rhyme | 0:774324cbc5a6 | 39 | // PULSE |

| Rhyme | 0:774324cbc5a6 | 40 | #define REG_PULSE_CFG 0x21 // ELE, Double_XYZ or Single_XYZ |

| Rhyme | 0:774324cbc5a6 | 41 | #define REG_PULSE_SRC 0x22 // EA, Double_XYZ or Single_XYZ |

| Rhyme | 0:774324cbc5a6 | 42 | #define REG_PULSE_THSX 0x23 // X pulse threshold |

| Rhyme | 0:774324cbc5a6 | 43 | #define REG_PULSE_THSY 0x24 // Y pulse threshold |

| Rhyme | 0:774324cbc5a6 | 44 | #define REG_PULSE_THSZ 0x25 // Z pulse threshold |

| Rhyme | 0:774324cbc5a6 | 45 | #define REG_PULSE_TMLT 0x26 // Time limit for pulse |

| Rhyme | 0:774324cbc5a6 | 46 | #define REG_PULSE_LTCY 0x27 // Latency time for 2nd pulse |

| Rhyme | 0:774324cbc5a6 | 47 | #define REG_PULSE_WIND 0x28 // Window time for 2nd pulse |

| Rhyme | 0:774324cbc5a6 | 48 | #define REG_ASLP_COUNT 0x29 // Counter setting for Auto-SLEEP |

| Rhyme | 0:774324cbc5a6 | 49 | // Control Registers |

| Rhyme | 0:774324cbc5a6 | 50 | #define REG_CTRL_REG1 0x2A // ODR = 800Hz, STANDBY Mode |

| Rhyme | 0:774324cbc5a6 | 51 | #define REG_CTRL_REG2 0x2B // Sleep Enable, OS Modes, RST, ST |

| Rhyme | 0:774324cbc5a6 | 52 | #define REG_CTRL_REG3 0x2C // Wake from Sleep, IPOL, PP_OD |

| Rhyme | 0:774324cbc5a6 | 53 | #define REG_CTRL_REG4 0x2D // Interrupt enable register |

| Rhyme | 0:774324cbc5a6 | 54 | #define REG_CTRL_REG5 0x2E // Interrupt pin (INT1/INT2) map |

| Rhyme | 0:774324cbc5a6 | 55 | // User Offset |

| Rhyme | 0:774324cbc5a6 | 56 | #define REG_OFF_X 0x2F // X-axis offset adjust |

| Rhyme | 0:774324cbc5a6 | 57 | #define REG_OFF_Y 0x30 // Y-axis offset adjust |

| Rhyme | 0:774324cbc5a6 | 58 | #define REG_OFF_Z 0x31 // Z-axis offset adjust |

| Rhyme | 0:774324cbc5a6 | 59 | |

| Rhyme | 0:774324cbc5a6 | 60 | // Value definitions |

| Rhyme | 0:774324cbc5a6 | 61 | #define BIT_TRIG_TRANS 0x20 // Transient interrupt trigger bit |

| Rhyme | 0:774324cbc5a6 | 62 | #define BIT_TRIG_LNDPRT 0x10 // Landscape/Portrati Orientation |

| Rhyme | 0:774324cbc5a6 | 63 | #define BIT_TRIG_PULSE 0x08 // Pulse interrupt trigger bit |

| Rhyme | 0:774324cbc5a6 | 64 | #define BIT_TRIG_FF_MT 0x04 // Freefall/Motion trigger bit |

| Rhyme | 0:774324cbc5a6 | 65 | |

| Rhyme | 0:774324cbc5a6 | 66 | MMA8451Q::MMA8451Q(I2C *i2c, int addr) : m_addr(addr<<1) { |

| Rhyme | 0:774324cbc5a6 | 67 | // activate the peripheral |

| Rhyme | 0:774324cbc5a6 | 68 | p_i2c = i2c ; |

| Rhyme | 0:774324cbc5a6 | 69 | uint8_t data[2] = {REG_CTRL_REG1, 0x01}; |

| Rhyme | 0:774324cbc5a6 | 70 | writeRegs(data, 2); |

| Rhyme | 0:774324cbc5a6 | 71 | } |

| Rhyme | 0:774324cbc5a6 | 72 | |

| Rhyme | 0:774324cbc5a6 | 73 | MMA8451Q::~MMA8451Q() { } |

| Rhyme | 0:774324cbc5a6 | 74 | |

| Rhyme | 0:774324cbc5a6 | 75 | int MMA8451Q::readRegs(int addr, uint8_t * data, int len) |

| Rhyme | 0:774324cbc5a6 | 76 | { |

| Rhyme | 0:774324cbc5a6 | 77 | char t[1] = {addr}; |

| Rhyme | 0:774324cbc5a6 | 78 | int result ; |

| Rhyme | 0:774324cbc5a6 | 79 | __disable_irq() ; // Disable Interrupts |

| Rhyme | 0:774324cbc5a6 | 80 | result = p_i2c->write(m_addr, t, 1, true); |

| Rhyme | 0:774324cbc5a6 | 81 | if (result == 0) { |

| Rhyme | 0:774324cbc5a6 | 82 | result = p_i2c->read(m_addr, (char *)data, len); |

| Rhyme | 0:774324cbc5a6 | 83 | } |

| Rhyme | 0:774324cbc5a6 | 84 | __enable_irq() ; // Enable Interrupts |

| Rhyme | 0:774324cbc5a6 | 85 | return( result ) ; |

| Rhyme | 0:774324cbc5a6 | 86 | } |

| Rhyme | 0:774324cbc5a6 | 87 | |

| Rhyme | 0:774324cbc5a6 | 88 | int MMA8451Q::writeRegs(uint8_t * data, int len) |

| Rhyme | 0:774324cbc5a6 | 89 | { |

| Rhyme | 0:774324cbc5a6 | 90 | int result ; |

| Rhyme | 0:774324cbc5a6 | 91 | __disable_irq() ; // Disable Interrupts |

| Rhyme | 0:774324cbc5a6 | 92 | result = p_i2c->write(m_addr, (char *)data, len); |

| Rhyme | 0:774324cbc5a6 | 93 | __enable_irq() ; // Enable Interrupts |

| Rhyme | 0:774324cbc5a6 | 94 | return( result ) ; |

| Rhyme | 0:774324cbc5a6 | 95 | } |

| Rhyme | 0:774324cbc5a6 | 96 | |

| Rhyme | 0:774324cbc5a6 | 97 | int MMA8451Q::getAllRawData(int16_t value[]) |

| Rhyme | 0:774324cbc5a6 | 98 | { |

| Rhyme | 0:774324cbc5a6 | 99 | int result ; |

| Rhyme | 0:774324cbc5a6 | 100 | uint8_t data[6] ; |

| Rhyme | 0:774324cbc5a6 | 101 | result = readRegs(REG_OUT_X_MSB, data, 6) ; |

| Rhyme | 0:774324cbc5a6 | 102 | if (result == 0) { |

| Rhyme | 0:774324cbc5a6 | 103 | value[0] = ((int16_t)((data[0] << 8) | data[1])) >> 2 ; |

| Rhyme | 0:774324cbc5a6 | 104 | value[1] = ((int16_t)((data[2] << 8) | data[3])) >> 2 ; |

| Rhyme | 0:774324cbc5a6 | 105 | value[2] = ((int16_t)((data[4] << 8) | data[5])) >> 2 ; |

| Rhyme | 0:774324cbc5a6 | 106 | } |

| Rhyme | 0:774324cbc5a6 | 107 | return( result ) ; |

| Rhyme | 0:774324cbc5a6 | 108 | } |

| Rhyme | 0:774324cbc5a6 | 109 | |

| Rhyme | 0:774324cbc5a6 | 110 | int MMA8451Q::getAllData(float fvalue[]) |

| Rhyme | 0:774324cbc5a6 | 111 | { |

| Rhyme | 0:774324cbc5a6 | 112 | int result ; |

| Rhyme | 0:774324cbc5a6 | 113 | uint8_t data[6] ; |

| Rhyme | 0:774324cbc5a6 | 114 | result = readRegs(REG_OUT_X_MSB, data, 6) ; |

| Rhyme | 0:774324cbc5a6 | 115 | if (result == 0) { |

| Rhyme | 0:774324cbc5a6 | 116 | fvalue[0] = (float)((int16_t)((data[0] << 8) | data[1])) / 16384.0 ; |

| Rhyme | 0:774324cbc5a6 | 117 | fvalue[1] = (float)((int16_t)((data[2] << 8) | data[3])) / 16384.0 ; |

| Rhyme | 0:774324cbc5a6 | 118 | fvalue[2] = (float)((int16_t)((data[4] << 8) | data[5])) / 16384.0 ; |

| Rhyme | 0:774324cbc5a6 | 119 | } |

| Rhyme | 0:774324cbc5a6 | 120 | return( result ) ; |

| Rhyme | 0:774324cbc5a6 | 121 | } |

| Rhyme | 0:774324cbc5a6 | 122 | |

| Rhyme | 0:774324cbc5a6 | 123 | int16_t MMA8451Q::getRawData(uint8_t addr) |

| Rhyme | 0:774324cbc5a6 | 124 | { |

| Rhyme | 0:774324cbc5a6 | 125 | int16_t value ; |

| Rhyme | 0:774324cbc5a6 | 126 | uint8_t data[2] ; |

| Rhyme | 0:774324cbc5a6 | 127 | readRegs(addr, data, 2) ; |

| Rhyme | 0:774324cbc5a6 | 128 | value = ((int16_t)((data[0] << 8) | data[1])) >> 2 ; |

| Rhyme | 0:774324cbc5a6 | 129 | return( value ) ; |

| Rhyme | 0:774324cbc5a6 | 130 | } |

| Rhyme | 0:774324cbc5a6 | 131 | |

| Rhyme | 0:774324cbc5a6 | 132 | int16_t MMA8451Q::getRawX(void) |

| Rhyme | 0:774324cbc5a6 | 133 | { |

| Rhyme | 0:774324cbc5a6 | 134 | int16_t value ; |

| Rhyme | 0:774324cbc5a6 | 135 | value = getRawData(REG_OUT_X_MSB) ; |

| Rhyme | 0:774324cbc5a6 | 136 | return( value ) ; |

| Rhyme | 0:774324cbc5a6 | 137 | } |

| Rhyme | 0:774324cbc5a6 | 138 | |

| Rhyme | 0:774324cbc5a6 | 139 | int16_t MMA8451Q::getRawY(void) |

| Rhyme | 0:774324cbc5a6 | 140 | { |

| Rhyme | 0:774324cbc5a6 | 141 | int16_t value ; |

| Rhyme | 0:774324cbc5a6 | 142 | value = getRawData(REG_OUT_Y_MSB) ; |

| Rhyme | 0:774324cbc5a6 | 143 | return( value ) ; |

| Rhyme | 0:774324cbc5a6 | 144 | } |

| Rhyme | 0:774324cbc5a6 | 145 | |

| Rhyme | 0:774324cbc5a6 | 146 | int16_t MMA8451Q::getRawZ(void) |

| Rhyme | 0:774324cbc5a6 | 147 | { |

| Rhyme | 0:774324cbc5a6 | 148 | int16_t value ; |

| Rhyme | 0:774324cbc5a6 | 149 | value = getRawData(REG_OUT_Z_MSB) ; |

| Rhyme | 0:774324cbc5a6 | 150 | return( value ) ; |

| Rhyme | 0:774324cbc5a6 | 151 | } |

| Rhyme | 0:774324cbc5a6 | 152 | |

| Rhyme | 0:774324cbc5a6 | 153 | float MMA8451Q::getAccX(void) |

| Rhyme | 0:774324cbc5a6 | 154 | { |

| Rhyme | 0:774324cbc5a6 | 155 | return(((float)getRawX())/4096.0) ; |

| Rhyme | 0:774324cbc5a6 | 156 | } |

| Rhyme | 0:774324cbc5a6 | 157 | |

| Rhyme | 0:774324cbc5a6 | 158 | float MMA8451Q::getAccY(void) |

| Rhyme | 0:774324cbc5a6 | 159 | { |

| Rhyme | 0:774324cbc5a6 | 160 | return(((float)getRawY())/4096.0) ; |

| Rhyme | 0:774324cbc5a6 | 161 | } |

| Rhyme | 0:774324cbc5a6 | 162 | |

| Rhyme | 0:774324cbc5a6 | 163 | float MMA8451Q::getAccZ(void) |

| Rhyme | 0:774324cbc5a6 | 164 | { |

| Rhyme | 0:774324cbc5a6 | 165 | return(((float)getRawZ())/4096.0) ; |

| Rhyme | 0:774324cbc5a6 | 166 | } |

La Suno

La Suno