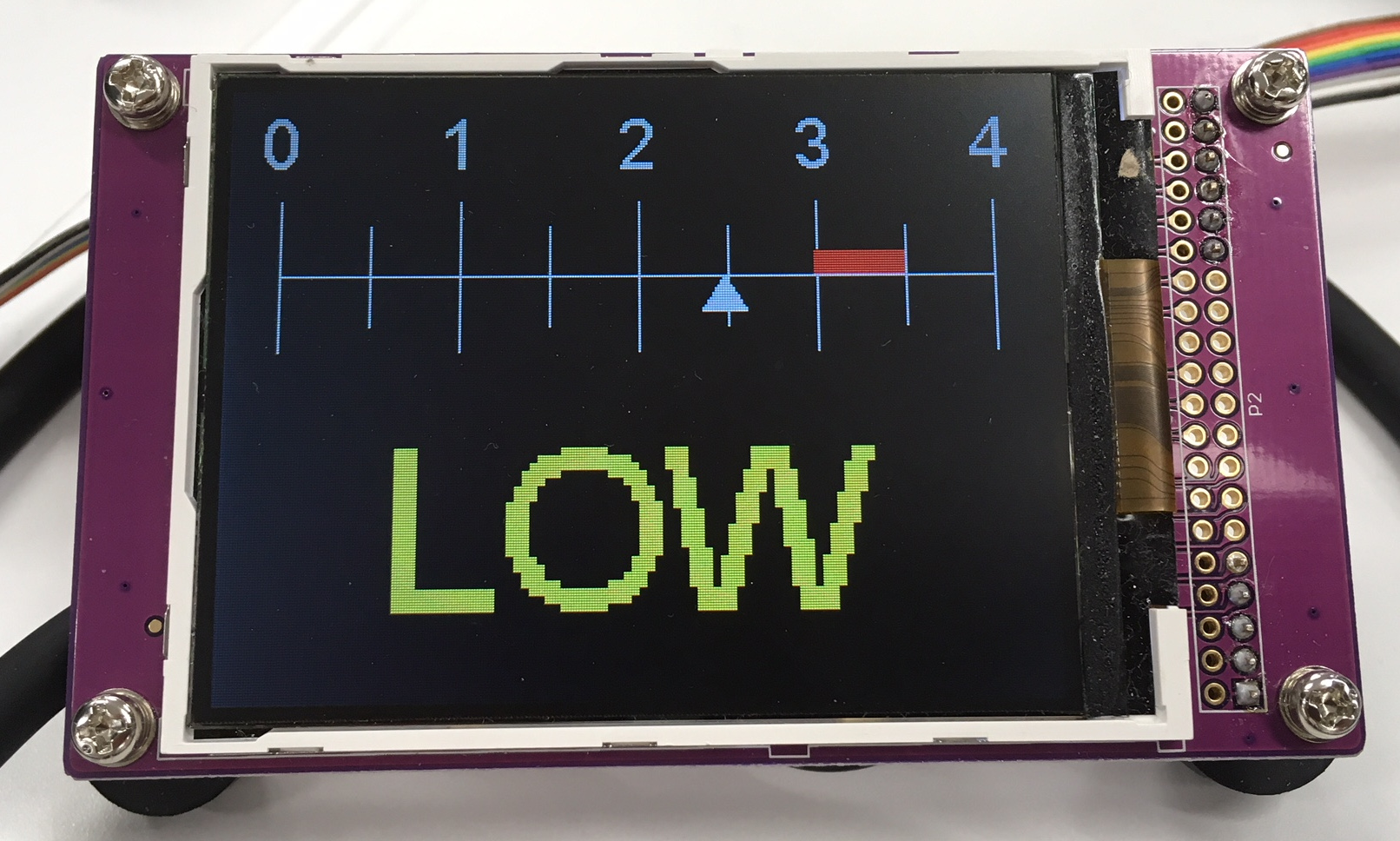

Release candidate version. The pointer in GAS Pressure display is changed to a triangle.

Dependencies: UniGraphic mbed vt100

Please note, at 2-Mar-2018 the current version of mbed-lib has a defect in Ticker.

https://os.mbed.com/forum/bugs-suggestions/topic/29287/

So, mbed lib version 157 is intentionally being used.

Please do not update mbed library until the problem in the above URL is fixed.

In this version, format of GAS Pressure Display has been changed.

moto

edge_utils/edge_reset_mgr.cpp@0:774324cbc5a6, 2018-03-02 (annotated)

- Committer:

- Rhyme

- Date:

- Fri Mar 02 07:56:09 2018 +0000

- Revision:

- 0:774324cbc5a6

Release candidate version. GAS Pressure pointer is now a triangle.; Some source file clean-up was done.

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| Rhyme | 0:774324cbc5a6 | 1 | #include "mbed.h" |

| Rhyme | 0:774324cbc5a6 | 2 | #include "edge_reset_mgr.h" |

| Rhyme | 0:774324cbc5a6 | 3 | |

| Rhyme | 0:774324cbc5a6 | 4 | /** |

| Rhyme | 0:774324cbc5a6 | 5 | * System Reset Status Register 0 (RCM_SRS0) 0x4007_F000 |

| Rhyme | 0:774324cbc5a6 | 6 | * |

| Rhyme | 0:774324cbc5a6 | 7 | * bit[7] : POR Power-On Reset |

| Rhyme | 0:774324cbc5a6 | 8 | * bit[6] : PIN External Reset Pin |

| Rhyme | 0:774324cbc5a6 | 9 | * bit[5] : WDOG Watchdog |

| Rhyme | 0:774324cbc5a6 | 10 | * bit[4] : (Reserved) |

| Rhyme | 0:774324cbc5a6 | 11 | * bit[3] : LOL Loss-of-Lock Reset |

| Rhyme | 0:774324cbc5a6 | 12 | * bit[2] : LOC Loss-of-Clock Reset |

| Rhyme | 0:774324cbc5a6 | 13 | * bit[1] : LVD Low-Voltage Detect Reset |

| Rhyme | 0:774324cbc5a6 | 14 | * bit[0] : WAKEUP Low Leakage Wakeup Reset |

| Rhyme | 0:774324cbc5a6 | 15 | */ |

| Rhyme | 0:774324cbc5a6 | 16 | #define REG_RCM_SRS0 (uint8_t *)0x4007F000 |

| Rhyme | 0:774324cbc5a6 | 17 | #define POR_RESET_BIT 0x80 |

| Rhyme | 0:774324cbc5a6 | 18 | #define PIN_RESET_BIT 0x40 |

| Rhyme | 0:774324cbc5a6 | 19 | #define WDG_RESET_BIT 0x20 |

| Rhyme | 0:774324cbc5a6 | 20 | #define LOL_RESET_BIT 0x08 |

| Rhyme | 0:774324cbc5a6 | 21 | #define LOC_RESET_BIT 0x04 |

| Rhyme | 0:774324cbc5a6 | 22 | #define LVD_RESET_BIT 0x02 |

| Rhyme | 0:774324cbc5a6 | 23 | #define WUP_RESET_BIT 0x01 |

| Rhyme | 0:774324cbc5a6 | 24 | |

| Rhyme | 0:774324cbc5a6 | 25 | /** |

| Rhyme | 0:774324cbc5a6 | 26 | * System Reset Status Register 1 (RCM_SRS1) 0x4007_F001 |

| Rhyme | 0:774324cbc5a6 | 27 | * |

| Rhyme | 0:774324cbc5a6 | 28 | * bit[7:6] (Reserved) |

| Rhyme | 0:774324cbc5a6 | 29 | * bit[5] : SACKERR Stop Mode Acknowledge Error Reset |

| Rhyme | 0:774324cbc5a6 | 30 | * bit[4] : (Reserved) |

| Rhyme | 0:774324cbc5a6 | 31 | * bit[3] : MDM_AP MDM-AP System Reset Request |

| Rhyme | 0:774324cbc5a6 | 32 | * bit[2] : SW Software Reset |

| Rhyme | 0:774324cbc5a6 | 33 | * bit[1] : LOCKUP Core Lockup |

| Rhyme | 0:774324cbc5a6 | 34 | * bit[0] : (Reserved) |

| Rhyme | 0:774324cbc5a6 | 35 | */ |

| Rhyme | 0:774324cbc5a6 | 36 | #define REG_RCM_SRS1 (uint8_t *)0x4007F001 |

| Rhyme | 0:774324cbc5a6 | 37 | #define SACK_RESET_BIT 0x20 |

| Rhyme | 0:774324cbc5a6 | 38 | #define MDM_RESET_BIT 0x08 |

| Rhyme | 0:774324cbc5a6 | 39 | #define SW_RESET_BIT 0x04 |

| Rhyme | 0:774324cbc5a6 | 40 | #define LOCKUP_RESET_BIT 0x02 |

| Rhyme | 0:774324cbc5a6 | 41 | |

| Rhyme | 0:774324cbc5a6 | 42 | #define IDX_POR_RESET 0 |

| Rhyme | 0:774324cbc5a6 | 43 | #define IDX_PIN_RESET 1 |

| Rhyme | 0:774324cbc5a6 | 44 | #define IDX_WDG_RESET 2 |

| Rhyme | 0:774324cbc5a6 | 45 | #define IDX_LOL_RESET 3 |

| Rhyme | 0:774324cbc5a6 | 46 | #define IDX_LOC_RESET 4 |

| Rhyme | 0:774324cbc5a6 | 47 | #define IDX_LVD_RESET 5 |

| Rhyme | 0:774324cbc5a6 | 48 | #define IDX_WUP_RESET 6 |

| Rhyme | 0:774324cbc5a6 | 49 | #define IDX_SACK_RESET 7 |

| Rhyme | 0:774324cbc5a6 | 50 | #define IDX_MDM_RESET 8 |

| Rhyme | 0:774324cbc5a6 | 51 | #define IDX_SW_RESET 9 |

| Rhyme | 0:774324cbc5a6 | 52 | #define IDX_LOCKUP_RESET 10 |

| Rhyme | 0:774324cbc5a6 | 53 | |

| Rhyme | 0:774324cbc5a6 | 54 | const char *reset_reason[] = { |

| Rhyme | 0:774324cbc5a6 | 55 | "Power On Reset", |

| Rhyme | 0:774324cbc5a6 | 56 | "Reset Pin Asserted", |

| Rhyme | 0:774324cbc5a6 | 57 | "Watch Dog Reset", |

| Rhyme | 0:774324cbc5a6 | 58 | "Loss of Lock Reset", |

| Rhyme | 0:774324cbc5a6 | 59 | "Loss of Clock Reset", |

| Rhyme | 0:774324cbc5a6 | 60 | "Low Voltage Detect Reset", |

| Rhyme | 0:774324cbc5a6 | 61 | "Low Leakage Wakeup Reset", |

| Rhyme | 0:774324cbc5a6 | 62 | "Stop Mode Acknowledge Error Reset", |

| Rhyme | 0:774324cbc5a6 | 63 | "MDM-AP System Reset Request", |

| Rhyme | 0:774324cbc5a6 | 64 | "Software Reset", |

| Rhyme | 0:774324cbc5a6 | 65 | "Core Lockup Reset", |

| Rhyme | 0:774324cbc5a6 | 66 | 0 |

| Rhyme | 0:774324cbc5a6 | 67 | } ; |

| Rhyme | 0:774324cbc5a6 | 68 | |

| Rhyme | 0:774324cbc5a6 | 69 | void print_reset_reason(void) |

| Rhyme | 0:774324cbc5a6 | 70 | { |

| Rhyme | 0:774324cbc5a6 | 71 | extern char *reset_reason_str ; |

| Rhyme | 0:774324cbc5a6 | 72 | int idx = 0 ; |

| Rhyme | 0:774324cbc5a6 | 73 | uint8_t *data = REG_RCM_SRS0 ; |

| Rhyme | 0:774324cbc5a6 | 74 | if (*data & POR_RESET_BIT) { |

| Rhyme | 0:774324cbc5a6 | 75 | idx = IDX_POR_RESET ; |

| Rhyme | 0:774324cbc5a6 | 76 | } |

| Rhyme | 0:774324cbc5a6 | 77 | if (*data & PIN_RESET_BIT) { |

| Rhyme | 0:774324cbc5a6 | 78 | idx = IDX_PIN_RESET ; |

| Rhyme | 0:774324cbc5a6 | 79 | } |

| Rhyme | 0:774324cbc5a6 | 80 | if (*data & WDG_RESET_BIT) { |

| Rhyme | 0:774324cbc5a6 | 81 | idx = IDX_WDG_RESET ; |

| Rhyme | 0:774324cbc5a6 | 82 | } |

| Rhyme | 0:774324cbc5a6 | 83 | if (*data & LOL_RESET_BIT) { |

| Rhyme | 0:774324cbc5a6 | 84 | idx = IDX_LOL_RESET ; |

| Rhyme | 0:774324cbc5a6 | 85 | } |

| Rhyme | 0:774324cbc5a6 | 86 | if (*data & LVD_RESET_BIT) { |

| Rhyme | 0:774324cbc5a6 | 87 | idx = IDX_LVD_RESET ; |

| Rhyme | 0:774324cbc5a6 | 88 | } |

| Rhyme | 0:774324cbc5a6 | 89 | if (*data & LOC_RESET_BIT) { |

| Rhyme | 0:774324cbc5a6 | 90 | idx = IDX_LOC_RESET ; |

| Rhyme | 0:774324cbc5a6 | 91 | } |

| Rhyme | 0:774324cbc5a6 | 92 | if (*data & WUP_RESET_BIT) { |

| Rhyme | 0:774324cbc5a6 | 93 | idx = IDX_WUP_RESET ; |

| Rhyme | 0:774324cbc5a6 | 94 | } |

| Rhyme | 0:774324cbc5a6 | 95 | data = REG_RCM_SRS1 ; |

| Rhyme | 0:774324cbc5a6 | 96 | if (*data & SACK_RESET_BIT) { |

| Rhyme | 0:774324cbc5a6 | 97 | idx = IDX_SACK_RESET ; |

| Rhyme | 0:774324cbc5a6 | 98 | } |

| Rhyme | 0:774324cbc5a6 | 99 | if (*data & MDM_RESET_BIT) { |

| Rhyme | 0:774324cbc5a6 | 100 | idx = IDX_MDM_RESET ; |

| Rhyme | 0:774324cbc5a6 | 101 | } |

| Rhyme | 0:774324cbc5a6 | 102 | if (*data & SW_RESET_BIT) { |

| Rhyme | 0:774324cbc5a6 | 103 | idx = IDX_SW_RESET ; |

| Rhyme | 0:774324cbc5a6 | 104 | } |

| Rhyme | 0:774324cbc5a6 | 105 | if (*data & LOCKUP_RESET_BIT) { |

| Rhyme | 0:774324cbc5a6 | 106 | idx = IDX_LOCKUP_RESET ; |

| Rhyme | 0:774324cbc5a6 | 107 | } |

| Rhyme | 0:774324cbc5a6 | 108 | printf("%s\n", reset_reason[idx]) ; |

| Rhyme | 0:774324cbc5a6 | 109 | reset_reason_str = (char *)reset_reason[idx] ; |

| Rhyme | 0:774324cbc5a6 | 110 | } |

| Rhyme | 0:774324cbc5a6 | 111 | |

| Rhyme | 0:774324cbc5a6 | 112 | /** |

| Rhyme | 0:774324cbc5a6 | 113 | * Software Reset |

| Rhyme | 0:774324cbc5a6 | 114 | * |

| Rhyme | 0:774324cbc5a6 | 115 | * From Cortex-M0 Devices Generic User Guide |

| Rhyme | 0:774324cbc5a6 | 116 | * 4.3.4 Application Interrupt and Reset Control Register |

| Rhyme | 0:774324cbc5a6 | 117 | * |

| Rhyme | 0:774324cbc5a6 | 118 | * Bit[31:16] : VECTCKEY |

| Rhyme | 0:774324cbc5a6 | 119 | * Bit[15] : ENDIANESS |

| Rhyme | 0:774324cbc5a6 | 120 | * Bit[14:3] : (Reserved) |

| Rhyme | 0:774324cbc5a6 | 121 | * Bit[2] : SYSRESETREQ |

| Rhyme | 0:774324cbc5a6 | 122 | * Bit[1] : VECTCLRACTIVE (reserved for debug use) |

| Rhyme | 0:774324cbc5a6 | 123 | * Bit[0] : (Reserved) |

| Rhyme | 0:774324cbc5a6 | 124 | * |

| Rhyme | 0:774324cbc5a6 | 125 | * Note: To trigger software reset, both VECTKEY=0x05FA and SYSRESETREQ |

| Rhyme | 0:774324cbc5a6 | 126 | * must be written at once, therefore the value will be |

| Rhyme | 0:774324cbc5a6 | 127 | * 0x05FA0004 |

| Rhyme | 0:774324cbc5a6 | 128 | */ |

| Rhyme | 0:774324cbc5a6 | 129 | |

| Rhyme | 0:774324cbc5a6 | 130 | void software_reset(void) |

| Rhyme | 0:774324cbc5a6 | 131 | { |

| Rhyme | 0:774324cbc5a6 | 132 | SCB->AIRCR = 0x05FA0004 ; |

| Rhyme | 0:774324cbc5a6 | 133 | } |

| Rhyme | 0:774324cbc5a6 | 134 | |

| Rhyme | 0:774324cbc5a6 | 135 | /** |

| Rhyme | 0:774324cbc5a6 | 136 | * reset_watch_dog |

| Rhyme | 0:774324cbc5a6 | 137 | * reset the watch dog counter |

| Rhyme | 0:774324cbc5a6 | 138 | * this function must be called within the limit (1sec) |

| Rhyme | 0:774324cbc5a6 | 139 | */ |

| Rhyme | 0:774324cbc5a6 | 140 | |

| Rhyme | 0:774324cbc5a6 | 141 | void reset_watch_dog(void) |

| Rhyme | 0:774324cbc5a6 | 142 | { |

| Rhyme | 0:774324cbc5a6 | 143 | SIM->SRVCOP = (uint32_t)0x55u; |

| Rhyme | 0:774324cbc5a6 | 144 | SIM->SRVCOP = (uint32_t)0xAAu; |

| Rhyme | 0:774324cbc5a6 | 145 | } |

La Suno

La Suno