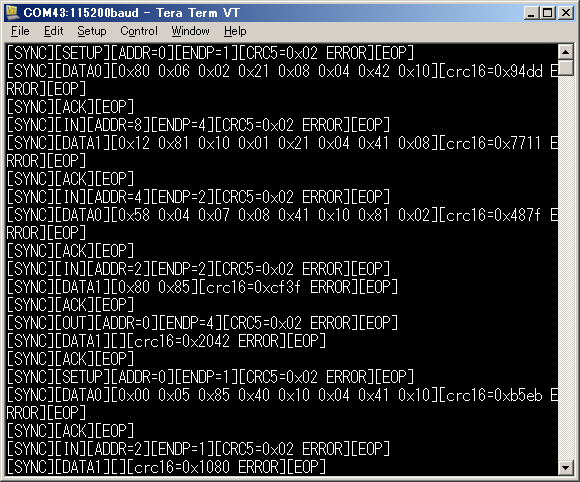

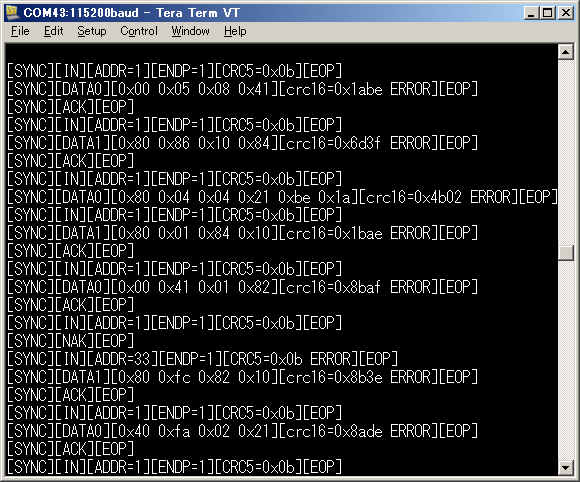

USB protocol analyzer

control:

interrupt in:

UsbCapture.s@0:0faa55631ffe, 2014-06-18 (annotated)

- Committer:

- va009039

- Date:

- Wed Jun 18 01:33:32 2014 +0000

- Revision:

- 0:0faa55631ffe

first commit

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| va009039 | 0:0faa55631ffe | 1 | ; UsbCapture.s 2014/5/21 |

| va009039 | 0:0faa55631ffe | 2 | ; |

| va009039 | 0:0faa55631ffe | 3 | AREA USBCAPTURE,CODE,READONLY |

| va009039 | 0:0faa55631ffe | 4 | |

| va009039 | 0:0faa55631ffe | 5 | |

| va009039 | 0:0faa55631ffe | 6 | ; uint8_t* usbcapture_lpc1114(uint8_t* buf, uint8_t* end) |

| va009039 | 0:0faa55631ffe | 7 | ; |

| va009039 | 0:0faa55631ffe | 8 | ;[ADDR][OUT ][SYNC] |1110}{0}{0}{0}{1|10}{0}{0}{0}{0}{0}{0} |

| va009039 | 0:0faa55631ffe | 9 | ;[ADDR][IN ][SYNC] |0}{110}{10}{0}{1|10}{0}{0}{0}{0}{0}{0} |

| va009039 | 0:0faa55631ffe | 10 | ;[ADDR][SETUP][SYNC] |0}{0}{10}{110}{1|10}{0}{0}{0}{0}{0}{0} |

| va009039 | 0:0faa55631ffe | 11 | ; |

| va009039 | 0:0faa55631ffe | 12 | ;[data][DATA0][SYNC] |110}{0}{0}{0}{11|10}{0}{0}{0}{0}{0}{0} |

| va009039 | 0:0faa55631ffe | 13 | ;[data][DATA1][SYNC] |0}{10}{0}{10}{11|10}{0}{0}{0}{0}{0}{0} |

| va009039 | 0:0faa55631ffe | 14 | ; |

| va009039 | 0:0faa55631ffe | 15 | ;[EOP ][ACK ][SYNC] |110}{10}{0}{10}|{10}{0}{0}{0}{0}{0}{0} |

| va009039 | 0:0faa55631ffe | 16 | ;[EOP ][NAK ][SYNC] |0}{10}{110}{10}|{10}{0}{0}{0}{0}{0}{0} |

| va009039 | 0:0faa55631ffe | 17 | ;[EOP ][STALL][SYNC] |0}{0}{0}{11110}|{10}{0}{0}{0}{0}{0}{0} |

| va009039 | 0:0faa55631ffe | 18 | ; |

| va009039 | 0:0faa55631ffe | 19 | ;{0} : 32 cycle |

| va009039 | 0:0faa55631ffe | 20 | ;{10} : 64 cycle |

| va009039 | 0:0faa55631ffe | 21 | ;{110} : 96 cycle |

| va009039 | 0:0faa55631ffe | 22 | ;{1110} : 128 cycle |

| va009039 | 0:0faa55631ffe | 23 | ;{11110} : 160 cycle |

| va009039 | 0:0faa55631ffe | 24 | ;{111110} : 192 cycle |

| va009039 | 0:0faa55631ffe | 25 | ;{1111110} : 224 cycle |

| va009039 | 0:0faa55631ffe | 26 | ; |

| va009039 | 0:0faa55631ffe | 27 | |

| va009039 | 0:0faa55631ffe | 28 | EXPORT usbcapture_lpc1114 |

| va009039 | 0:0faa55631ffe | 29 | |

| va009039 | 0:0faa55631ffe | 30 | CYCLE equ 32 |

| va009039 | 0:0faa55631ffe | 31 | GPIO1 equ 0x50010c00 |

| va009039 | 0:0faa55631ffe | 32 | CT16B1 equ 0x40010000 |

| va009039 | 0:0faa55631ffe | 33 | _IR equ 0x00 |

| va009039 | 0:0faa55631ffe | 34 | _TC equ 0x08 |

| va009039 | 0:0faa55631ffe | 35 | _CR0 equ 0x2c |

| va009039 | 0:0faa55631ffe | 36 | CR0Int equ (1<<4) |

| va009039 | 0:0faa55631ffe | 37 | |

| va009039 | 0:0faa55631ffe | 38 | ; PID |

| va009039 | 0:0faa55631ffe | 39 | ACK equ 0x02 |

| va009039 | 0:0faa55631ffe | 40 | NAK equ 0x0a |

| va009039 | 0:0faa55631ffe | 41 | STALL equ 0x0e |

| va009039 | 0:0faa55631ffe | 42 | DATA0 equ 0x03 |

| va009039 | 0:0faa55631ffe | 43 | DATA1 equ 0x0b |

| va009039 | 0:0faa55631ffe | 44 | IN equ 0x09 |

| va009039 | 0:0faa55631ffe | 45 | OUT equ 0x01 |

| va009039 | 0:0faa55631ffe | 46 | SETUP equ 0x0d |

| va009039 | 0:0faa55631ffe | 47 | |

| va009039 | 0:0faa55631ffe | 48 | MACRO |

| va009039 | 0:0faa55631ffe | 49 | init_param |

| va009039 | 0:0faa55631ffe | 50 | LDR r4, =GPIO1 ; USB_DM(P1_9),USB_DP(P1_8) |

| va009039 | 0:0faa55631ffe | 51 | LDR r5, =CT16B1 ; CT16B1 |

| va009039 | 0:0faa55631ffe | 52 | MOVS r6, #CR0Int ; CR0 interrupt mask |

| va009039 | 0:0faa55631ffe | 53 | MOVS r3, #1 ; prev_CR0 |

| va009039 | 0:0faa55631ffe | 54 | MEND |

| va009039 | 0:0faa55631ffe | 55 | |

| va009039 | 0:0faa55631ffe | 56 | MACRO |

| va009039 | 0:0faa55631ffe | 57 | save_raw |

| va009039 | 0:0faa55631ffe | 58 | STRB r2,[r0] |

| va009039 | 0:0faa55631ffe | 59 | ADDS r0, r0, #1 |

| va009039 | 0:0faa55631ffe | 60 | MEND |

| va009039 | 0:0faa55631ffe | 61 | |

| va009039 | 0:0faa55631ffe | 62 | MACRO |

| va009039 | 0:0faa55631ffe | 63 | read |

| va009039 | 0:0faa55631ffe | 64 | 1 LDR r2, [r5,#_IR] |

| va009039 | 0:0faa55631ffe | 65 | TST r2, r6 |

| va009039 | 0:0faa55631ffe | 66 | BEQ %b1 |

| va009039 | 0:0faa55631ffe | 67 | LDR r2, [r5,#_CR0] |

| va009039 | 0:0faa55631ffe | 68 | STR r6, [r5,#_IR] |

| va009039 | 0:0faa55631ffe | 69 | SUBS r2, r2, r3 |

| va009039 | 0:0faa55631ffe | 70 | ADDS r3, r3, r2 |

| va009039 | 0:0faa55631ffe | 71 | UXTB r2, r2 |

| va009039 | 0:0faa55631ffe | 72 | MEND |

| va009039 | 0:0faa55631ffe | 73 | |

| va009039 | 0:0faa55631ffe | 74 | MACRO |

| va009039 | 0:0faa55631ffe | 75 | readNB $skip |

| va009039 | 0:0faa55631ffe | 76 | LDR r2, [r5,#_IR] |

| va009039 | 0:0faa55631ffe | 77 | TST r2, r6 |

| va009039 | 0:0faa55631ffe | 78 | BEQ $skip |

| va009039 | 0:0faa55631ffe | 79 | LDR r2, [r5,#_CR0] |

| va009039 | 0:0faa55631ffe | 80 | STR r6, [r5,#_IR] |

| va009039 | 0:0faa55631ffe | 81 | SUBS r2, r2, r3 |

| va009039 | 0:0faa55631ffe | 82 | ADDS r3, r3, r2 |

| va009039 | 0:0faa55631ffe | 83 | UXTB r2, r2 |

| va009039 | 0:0faa55631ffe | 84 | MEND |

| va009039 | 0:0faa55631ffe | 85 | |

| va009039 | 0:0faa55631ffe | 86 | MACRO |

| va009039 | 0:0faa55631ffe | 87 | read_TC |

| va009039 | 0:0faa55631ffe | 88 | LDR r2, [r5,#_TC] |

| va009039 | 0:0faa55631ffe | 89 | SUBS r2, r2, r3 |

| va009039 | 0:0faa55631ffe | 90 | ADDS r3, r3, r2 |

| va009039 | 0:0faa55631ffe | 91 | UXTB r2, r2 |

| va009039 | 0:0faa55631ffe | 92 | MEND |

| va009039 | 0:0faa55631ffe | 93 | |

| va009039 | 0:0faa55631ffe | 94 | MACRO |

| va009039 | 0:0faa55631ffe | 95 | if_1bit_gt $goto |

| va009039 | 0:0faa55631ffe | 96 | CMP r2, #CYCLE+CYCLE/2 |

| va009039 | 0:0faa55631ffe | 97 | BGT $goto |

| va009039 | 0:0faa55631ffe | 98 | MEND |

| va009039 | 0:0faa55631ffe | 99 | |

| va009039 | 0:0faa55631ffe | 100 | MACRO |

| va009039 | 0:0faa55631ffe | 101 | if_1bit_le $goto |

| va009039 | 0:0faa55631ffe | 102 | CMP r2, #CYCLE+CYCLE/2 |

| va009039 | 0:0faa55631ffe | 103 | BLE $goto |

| va009039 | 0:0faa55631ffe | 104 | MEND |

| va009039 | 0:0faa55631ffe | 105 | |

| va009039 | 0:0faa55631ffe | 106 | MACRO |

| va009039 | 0:0faa55631ffe | 107 | if_2bit_le $goto |

| va009039 | 0:0faa55631ffe | 108 | CMP r2, #CYCLE*2+CYCLE/2 |

| va009039 | 0:0faa55631ffe | 109 | BLE $goto |

| va009039 | 0:0faa55631ffe | 110 | MEND |

| va009039 | 0:0faa55631ffe | 111 | |

| va009039 | 0:0faa55631ffe | 112 | MACRO |

| va009039 | 0:0faa55631ffe | 113 | if_3bit_le $goto |

| va009039 | 0:0faa55631ffe | 114 | CMP r2, #CYCLE*3+CYCLE/2 |

| va009039 | 0:0faa55631ffe | 115 | BLE $goto |

| va009039 | 0:0faa55631ffe | 116 | MEND |

| va009039 | 0:0faa55631ffe | 117 | |

| va009039 | 0:0faa55631ffe | 118 | MACRO |

| va009039 | 0:0faa55631ffe | 119 | eopNB $skip |

| va009039 | 0:0faa55631ffe | 120 | LDR r2, [r4] ; EOP(USB_DM=0,USB_DP=0) ? |

| va009039 | 0:0faa55631ffe | 121 | TST r2, r2 |

| va009039 | 0:0faa55631ffe | 122 | BNE $skip ; no |

| va009039 | 0:0faa55631ffe | 123 | MEND |

| va009039 | 0:0faa55631ffe | 124 | |

| va009039 | 0:0faa55631ffe | 125 | usbcapture_lpc1114 |

| va009039 | 0:0faa55631ffe | 126 | CAPTURE PUSH {r4-r7} |

| va009039 | 0:0faa55631ffe | 127 | init_param |

| va009039 | 0:0faa55631ffe | 128 | |

| va009039 | 0:0faa55631ffe | 129 | SYNC |

| va009039 | 0:0faa55631ffe | 130 | read |

| va009039 | 0:0faa55631ffe | 131 | if_1bit_gt SYNC |

| va009039 | 0:0faa55631ffe | 132 | read |

| va009039 | 0:0faa55631ffe | 133 | if_1bit_gt SYNC |

| va009039 | 0:0faa55631ffe | 134 | read |

| va009039 | 0:0faa55631ffe | 135 | if_1bit_gt SYNC |

| va009039 | 0:0faa55631ffe | 136 | SYNC_67bit |

| va009039 | 0:0faa55631ffe | 137 | read |

| va009039 | 0:0faa55631ffe | 138 | if_1bit_le SYNC_67bit |

| va009039 | 0:0faa55631ffe | 139 | if_2bit_le PID_ACK_NAK_STALL |

| va009039 | 0:0faa55631ffe | 140 | if_3bit_le PID_IN_OUT_SETUP |

| va009039 | 0:0faa55631ffe | 141 | |

| va009039 | 0:0faa55631ffe | 142 | PID_DATA0_DATA1 |

| va009039 | 0:0faa55631ffe | 143 | read |

| va009039 | 0:0faa55631ffe | 144 | if_1bit_le PID_DATA0 |

| va009039 | 0:0faa55631ffe | 145 | |

| va009039 | 0:0faa55631ffe | 146 | PID_DATA1 |

| va009039 | 0:0faa55631ffe | 147 | read |

| va009039 | 0:0faa55631ffe | 148 | read |

| va009039 | 0:0faa55631ffe | 149 | MOVS r2, #DATA1 |

| va009039 | 0:0faa55631ffe | 150 | save_raw |

| va009039 | 0:0faa55631ffe | 151 | B DATA_CRC16 |

| va009039 | 0:0faa55631ffe | 152 | |

| va009039 | 0:0faa55631ffe | 153 | PID_DATA0 |

| va009039 | 0:0faa55631ffe | 154 | read |

| va009039 | 0:0faa55631ffe | 155 | read |

| va009039 | 0:0faa55631ffe | 156 | MOVS r2, #DATA0 |

| va009039 | 0:0faa55631ffe | 157 | save_raw |

| va009039 | 0:0faa55631ffe | 158 | B DATA_CRC16 |

| va009039 | 0:0faa55631ffe | 159 | |

| va009039 | 0:0faa55631ffe | 160 | PID_ACK_NAK_STALL |

| va009039 | 0:0faa55631ffe | 161 | read |

| va009039 | 0:0faa55631ffe | 162 | if_2bit_le PID_ACK_NAK |

| va009039 | 0:0faa55631ffe | 163 | |

| va009039 | 0:0faa55631ffe | 164 | PID_STALL |

| va009039 | 0:0faa55631ffe | 165 | read |

| va009039 | 0:0faa55631ffe | 166 | read |

| va009039 | 0:0faa55631ffe | 167 | MOVS r2, #STALL |

| va009039 | 0:0faa55631ffe | 168 | save_raw |

| va009039 | 0:0faa55631ffe | 169 | B EOP_WAIT |

| va009039 | 0:0faa55631ffe | 170 | |

| va009039 | 0:0faa55631ffe | 171 | PID_ACK_NAK |

| va009039 | 0:0faa55631ffe | 172 | read |

| va009039 | 0:0faa55631ffe | 173 | if_1bit_le PID_ACK |

| va009039 | 0:0faa55631ffe | 174 | |

| va009039 | 0:0faa55631ffe | 175 | PID_NAK |

| va009039 | 0:0faa55631ffe | 176 | read ; 10b |

| va009039 | 0:0faa55631ffe | 177 | read ; 0b |

| va009039 | 0:0faa55631ffe | 178 | MOVS r2, #NAK |

| va009039 | 0:0faa55631ffe | 179 | save_raw |

| va009039 | 0:0faa55631ffe | 180 | B EOP_WAIT |

| va009039 | 0:0faa55631ffe | 181 | |

| va009039 | 0:0faa55631ffe | 182 | PID_ACK |

| va009039 | 0:0faa55631ffe | 183 | read |

| va009039 | 0:0faa55631ffe | 184 | MOVS r2, #ACK |

| va009039 | 0:0faa55631ffe | 185 | save_raw |

| va009039 | 0:0faa55631ffe | 186 | B EOP_WAIT |

| va009039 | 0:0faa55631ffe | 187 | |

| va009039 | 0:0faa55631ffe | 188 | PID_IN_OUT_SETUP |

| va009039 | 0:0faa55631ffe | 189 | read |

| va009039 | 0:0faa55631ffe | 190 | if_1bit_le PID_IN_OUT |

| va009039 | 0:0faa55631ffe | 191 | |

| va009039 | 0:0faa55631ffe | 192 | PID_SETUP |

| va009039 | 0:0faa55631ffe | 193 | read |

| va009039 | 0:0faa55631ffe | 194 | read |

| va009039 | 0:0faa55631ffe | 195 | MOVS r2, #SETUP |

| va009039 | 0:0faa55631ffe | 196 | save_raw |

| va009039 | 0:0faa55631ffe | 197 | B ADDR_ENDP_CRC5 |

| va009039 | 0:0faa55631ffe | 198 | |

| va009039 | 0:0faa55631ffe | 199 | PID_IN_OUT |

| va009039 | 0:0faa55631ffe | 200 | read |

| va009039 | 0:0faa55631ffe | 201 | if_1bit_le PID_OUT |

| va009039 | 0:0faa55631ffe | 202 | |

| va009039 | 0:0faa55631ffe | 203 | PID_IN |

| va009039 | 0:0faa55631ffe | 204 | read |

| va009039 | 0:0faa55631ffe | 205 | MOVS r2, #IN |

| va009039 | 0:0faa55631ffe | 206 | save_raw |

| va009039 | 0:0faa55631ffe | 207 | |

| va009039 | 0:0faa55631ffe | 208 | DATA_CRC16 |

| va009039 | 0:0faa55631ffe | 209 | ADDR_ENDP_CRC5 |

| va009039 | 0:0faa55631ffe | 210 | 20 |

| va009039 | 0:0faa55631ffe | 211 | readNB %f30 |

| va009039 | 0:0faa55631ffe | 212 | save_raw |

| va009039 | 0:0faa55631ffe | 213 | CMP r0, r1 |

| va009039 | 0:0faa55631ffe | 214 | BGE %f90 ; buffer full ? |

| va009039 | 0:0faa55631ffe | 215 | B %b20 |

| va009039 | 0:0faa55631ffe | 216 | 30 |

| va009039 | 0:0faa55631ffe | 217 | eopNB %b20 |

| va009039 | 0:0faa55631ffe | 218 | STRB r2, [r0,#1] |

| va009039 | 0:0faa55631ffe | 219 | read_TC |

| va009039 | 0:0faa55631ffe | 220 | STRB r2, [r0,#0] |

| va009039 | 0:0faa55631ffe | 221 | ADDS r0, r0, #2 |

| va009039 | 0:0faa55631ffe | 222 | B EOP |

| va009039 | 0:0faa55631ffe | 223 | |

| va009039 | 0:0faa55631ffe | 224 | PID_OUT |

| va009039 | 0:0faa55631ffe | 225 | read |

| va009039 | 0:0faa55631ffe | 226 | MOVS r2, #OUT |

| va009039 | 0:0faa55631ffe | 227 | save_raw |

| va009039 | 0:0faa55631ffe | 228 | B ADDR_ENDP_CRC5 |

| va009039 | 0:0faa55631ffe | 229 | |

| va009039 | 0:0faa55631ffe | 230 | EOP_WAIT |

| va009039 | 0:0faa55631ffe | 231 | 10 |

| va009039 | 0:0faa55631ffe | 232 | eopNB %b10 |

| va009039 | 0:0faa55631ffe | 233 | save_raw |

| va009039 | 0:0faa55631ffe | 234 | CMP r0, r1 |

| va009039 | 0:0faa55631ffe | 235 | BGE EXIT |

| va009039 | 0:0faa55631ffe | 236 | B SYNC |

| va009039 | 0:0faa55631ffe | 237 | EOP |

| va009039 | 0:0faa55631ffe | 238 | CMP r0, r1 |

| va009039 | 0:0faa55631ffe | 239 | BGE EXIT ; buffer full ? |

| va009039 | 0:0faa55631ffe | 240 | B SYNC |

| va009039 | 0:0faa55631ffe | 241 | EXIT |

| va009039 | 0:0faa55631ffe | 242 | 90 POP {r4-r7} |

| va009039 | 0:0faa55631ffe | 243 | BX lr ; return, buf = r0 |

| va009039 | 0:0faa55631ffe | 244 | |

| va009039 | 0:0faa55631ffe | 245 | ERROR POP {r4-r7} |

| va009039 | 0:0faa55631ffe | 246 | BX lr |

| va009039 | 0:0faa55631ffe | 247 | |

| va009039 | 0:0faa55631ffe | 248 | ALIGN |

| va009039 | 0:0faa55631ffe | 249 | END |

| va009039 | 0:0faa55631ffe | 250 |