Fork of mbed-src file paths change. LPC1114FN28 use only.

Fork of mbed-src by

Information

この情報は2013/10/28時点での解決方法です。

現在はmbed-src、標準ライブラリで問題なくコンパイルが可能です。

・使う物

LPC1114FN28

mbed SDK

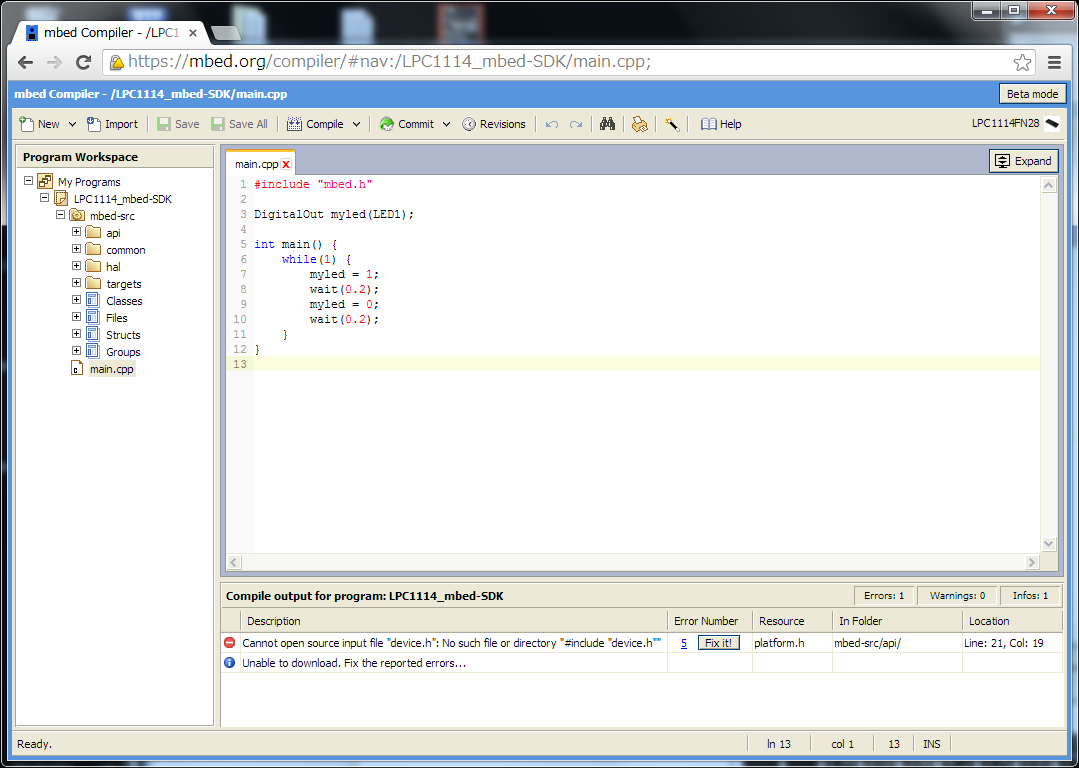

LPC1114FN28でmbed-SDKのLibraryを使うとCompile出来ない。(2013/10/28)

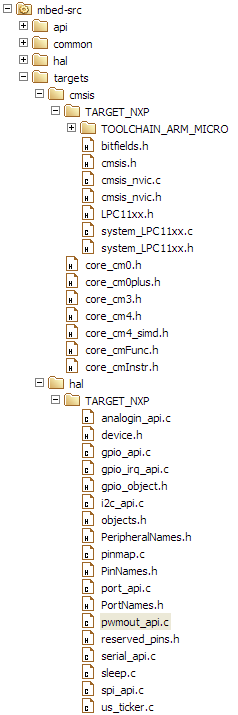

パスが通ってないだけのようなのでファイルを以下に移動する。

| mbed-src\targets\cmsis\TARGET_NXP\TARGET_LPC11XX_11CXX\ mbed-src\targets\cmsis\TARGET_NXP\TARGET_LPC11XX_11CXX\TARGET_LPC11XX\ |

にあるファイルをすべて

| mbed-src\targets\cmsis\TARGET_NXP\ |

へ移動

mbed-src\targets\cmsis\TARGET_NXP\TARGET_LPC11XX_11CXX\にある

| TOOLCHAIN_ARM_MICRO |

をフォルダごと

| mbed-src\targets\cmsis\TARGET_NXP\ |

へ移動

| mbed-src\targets\hal\TARGET_NXP\TARGET_LPC11XX_11CXX\ mbed-src\targets\hal\TARGET_NXP\TARGET_LPC11XX_11CXX\TARGET_LPC11XX\ |

にあるファイルをすべて

| mbed-src\targets\hal\TARGET_NXP\ |

へ移動

移動後は以下のような構成になると思います。

※不要なファイルは削除してあります。

|

ファイルの移動が面倒なので以下に本家からフォークしたライブラリを置いておきます。

Import librarymbed-src-LPC1114FN28

Fork of mbed-src file paths change. LPC1114FN28 use only.

エラーが出力される場合

"TOOLCHAIN_ARM_MICRO"が無いとエラーになる。

| Error: Undefined symbol _initial_sp (referred from entry2.o). Error: Undefined symbol _heap_base (referred from malloc.o). Error: Undefined symbol _heap_limit (referred from malloc.o). |

LPC1114FN28はMicrolibを使ってCompileされるため上記のエラーになるようです。

targets/hal/TARGET_NXP/TARGET_LPC408X/gpio_irq_api.c@15:4892fe388435, 2013-08-07 (annotated)

- Committer:

- bogdanm

- Date:

- Wed Aug 07 16:43:59 2013 +0300

- Revision:

- 15:4892fe388435

- Child:

- 29:6ac4027eff2b

Added LPC4088 target and interrupt chaining code

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| bogdanm | 15:4892fe388435 | 1 | /* mbed Microcontroller Library |

| bogdanm | 15:4892fe388435 | 2 | * Copyright (c) 2006-2013 ARM Limited |

| bogdanm | 15:4892fe388435 | 3 | * |

| bogdanm | 15:4892fe388435 | 4 | * Licensed under the Apache License, Version 2.0 (the "License"); |

| bogdanm | 15:4892fe388435 | 5 | * you may not use this file except in compliance with the License. |

| bogdanm | 15:4892fe388435 | 6 | * You may obtain a copy of the License at |

| bogdanm | 15:4892fe388435 | 7 | * |

| bogdanm | 15:4892fe388435 | 8 | * http://www.apache.org/licenses/LICENSE-2.0 |

| bogdanm | 15:4892fe388435 | 9 | * |

| bogdanm | 15:4892fe388435 | 10 | * Unless required by applicable law or agreed to in writing, software |

| bogdanm | 15:4892fe388435 | 11 | * distributed under the License is distributed on an "AS IS" BASIS, |

| bogdanm | 15:4892fe388435 | 12 | * WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied. |

| bogdanm | 15:4892fe388435 | 13 | * See the License for the specific language governing permissions and |

| bogdanm | 15:4892fe388435 | 14 | * limitations under the License. |

| bogdanm | 15:4892fe388435 | 15 | */ |

| bogdanm | 15:4892fe388435 | 16 | #include <stddef.h> |

| bogdanm | 15:4892fe388435 | 17 | #include "gpio_irq_api.h" |

| bogdanm | 15:4892fe388435 | 18 | #include "error.h" |

| bogdanm | 15:4892fe388435 | 19 | #include "cmsis.h" |

| bogdanm | 15:4892fe388435 | 20 | |

| bogdanm | 15:4892fe388435 | 21 | #define CHANNEL_NUM 64 |

| bogdanm | 15:4892fe388435 | 22 | |

| bogdanm | 15:4892fe388435 | 23 | static uint32_t channel_ids[CHANNEL_NUM] = {0}; |

| bogdanm | 15:4892fe388435 | 24 | static gpio_irq_handler irq_handler; |

| bogdanm | 15:4892fe388435 | 25 | |

| bogdanm | 15:4892fe388435 | 26 | static void handle_interrupt_in(void) { |

| bogdanm | 15:4892fe388435 | 27 | // Read in all current interrupt registers. We do this once as the |

| bogdanm | 15:4892fe388435 | 28 | // GPIO interrupt registers are on the APB bus, and this is slow. |

| bogdanm | 15:4892fe388435 | 29 | uint32_t rise0 = LPC_GPIOINT->IO0IntStatR; |

| bogdanm | 15:4892fe388435 | 30 | uint32_t fall0 = LPC_GPIOINT->IO0IntStatF; |

| bogdanm | 15:4892fe388435 | 31 | uint32_t rise2 = LPC_GPIOINT->IO2IntStatR; |

| bogdanm | 15:4892fe388435 | 32 | uint32_t fall2 = LPC_GPIOINT->IO2IntStatF; |

| bogdanm | 15:4892fe388435 | 33 | uint32_t mask0 = 0; |

| bogdanm | 15:4892fe388435 | 34 | uint32_t mask2 = 0; |

| bogdanm | 15:4892fe388435 | 35 | int i; |

| bogdanm | 15:4892fe388435 | 36 | |

| bogdanm | 15:4892fe388435 | 37 | // P0.0-0.31 |

| bogdanm | 15:4892fe388435 | 38 | for (i = 0; i < 32; i++) { |

| bogdanm | 15:4892fe388435 | 39 | uint32_t pmask = (1 << i); |

| bogdanm | 15:4892fe388435 | 40 | if (rise0 & pmask) { |

| bogdanm | 15:4892fe388435 | 41 | mask0 |= pmask; |

| bogdanm | 15:4892fe388435 | 42 | if (channel_ids[i] != 0) |

| bogdanm | 15:4892fe388435 | 43 | irq_handler(channel_ids[i], IRQ_RISE); |

| bogdanm | 15:4892fe388435 | 44 | } |

| bogdanm | 15:4892fe388435 | 45 | if (fall0 & pmask) { |

| bogdanm | 15:4892fe388435 | 46 | mask0 |= pmask; |

| bogdanm | 15:4892fe388435 | 47 | if (channel_ids[i] != 0) |

| bogdanm | 15:4892fe388435 | 48 | irq_handler(channel_ids[i], IRQ_FALL); |

| bogdanm | 15:4892fe388435 | 49 | } |

| bogdanm | 15:4892fe388435 | 50 | } |

| bogdanm | 15:4892fe388435 | 51 | |

| bogdanm | 15:4892fe388435 | 52 | // P2.0-2.31 |

| bogdanm | 15:4892fe388435 | 53 | for (i = 0; i < 32; i++) { |

| bogdanm | 15:4892fe388435 | 54 | uint32_t pmask = (1 << i); |

| bogdanm | 15:4892fe388435 | 55 | int channel_index = i + 32; |

| bogdanm | 15:4892fe388435 | 56 | if (rise2 & pmask) { |

| bogdanm | 15:4892fe388435 | 57 | mask2 |= pmask; |

| bogdanm | 15:4892fe388435 | 58 | if (channel_ids[channel_index] != 0) |

| bogdanm | 15:4892fe388435 | 59 | irq_handler(channel_ids[channel_index], IRQ_RISE); |

| bogdanm | 15:4892fe388435 | 60 | } |

| bogdanm | 15:4892fe388435 | 61 | if (fall2 & pmask) { |

| bogdanm | 15:4892fe388435 | 62 | mask2 |= pmask; |

| bogdanm | 15:4892fe388435 | 63 | if (channel_ids[channel_index] != 0) |

| bogdanm | 15:4892fe388435 | 64 | irq_handler(channel_ids[channel_index], IRQ_FALL); |

| bogdanm | 15:4892fe388435 | 65 | } |

| bogdanm | 15:4892fe388435 | 66 | } |

| bogdanm | 15:4892fe388435 | 67 | |

| bogdanm | 15:4892fe388435 | 68 | // Clear the interrupts we just handled |

| bogdanm | 15:4892fe388435 | 69 | LPC_GPIOINT->IO0IntClr = mask0; |

| bogdanm | 15:4892fe388435 | 70 | LPC_GPIOINT->IO2IntClr = mask2; |

| bogdanm | 15:4892fe388435 | 71 | } |

| bogdanm | 15:4892fe388435 | 72 | |

| bogdanm | 15:4892fe388435 | 73 | int gpio_irq_init(gpio_irq_t *obj, PinName pin, gpio_irq_handler handler, uint32_t id) { |

| bogdanm | 15:4892fe388435 | 74 | if (pin == NC) return -1; |

| bogdanm | 15:4892fe388435 | 75 | |

| bogdanm | 15:4892fe388435 | 76 | irq_handler = handler; |

| bogdanm | 15:4892fe388435 | 77 | |

| bogdanm | 15:4892fe388435 | 78 | obj->port = ((int)(LPC_GPIO0_BASE+pin) & ~0x1F); |

| bogdanm | 15:4892fe388435 | 79 | obj->pin = (int)pin % 32; |

| bogdanm | 15:4892fe388435 | 80 | |

| bogdanm | 15:4892fe388435 | 81 | // Interrupts available only on GPIO0 and GPIO2 |

| bogdanm | 15:4892fe388435 | 82 | if (obj->port != LPC_GPIO0_BASE && obj->port != LPC_GPIO2_BASE) { |

| bogdanm | 15:4892fe388435 | 83 | error("pins on this port cannot generate interrupts\n"); |

| bogdanm | 15:4892fe388435 | 84 | } |

| bogdanm | 15:4892fe388435 | 85 | |

| bogdanm | 15:4892fe388435 | 86 | // put us in the interrupt table |

| bogdanm | 15:4892fe388435 | 87 | int index = (obj->port == LPC_GPIO0_BASE) ? obj->pin : obj->pin + 32; |

| bogdanm | 15:4892fe388435 | 88 | channel_ids[index] = id; |

| bogdanm | 15:4892fe388435 | 89 | obj->ch = index; |

| bogdanm | 15:4892fe388435 | 90 | |

| bogdanm | 15:4892fe388435 | 91 | NVIC_SetVector(GPIO_IRQn, (uint32_t)handle_interrupt_in); |

| bogdanm | 15:4892fe388435 | 92 | NVIC_EnableIRQ(GPIO_IRQn); |

| bogdanm | 15:4892fe388435 | 93 | |

| bogdanm | 15:4892fe388435 | 94 | return 0; |

| bogdanm | 15:4892fe388435 | 95 | } |

| bogdanm | 15:4892fe388435 | 96 | |

| bogdanm | 15:4892fe388435 | 97 | void gpio_irq_free(gpio_irq_t *obj) { |

| bogdanm | 15:4892fe388435 | 98 | channel_ids[obj->ch] = 0; |

| bogdanm | 15:4892fe388435 | 99 | } |

| bogdanm | 15:4892fe388435 | 100 | |

| bogdanm | 15:4892fe388435 | 101 | void gpio_irq_set(gpio_irq_t *obj, gpio_irq_event event, uint32_t enable) { |

| bogdanm | 15:4892fe388435 | 102 | // ensure nothing is pending |

| bogdanm | 15:4892fe388435 | 103 | switch (obj->port) { |

| bogdanm | 15:4892fe388435 | 104 | case LPC_GPIO0_BASE: LPC_GPIOINT->IO0IntClr = 1 << obj->pin; break; |

| bogdanm | 15:4892fe388435 | 105 | case LPC_GPIO2_BASE: LPC_GPIOINT->IO2IntClr = 1 << obj->pin; break; |

| bogdanm | 15:4892fe388435 | 106 | } |

| bogdanm | 15:4892fe388435 | 107 | |

| bogdanm | 15:4892fe388435 | 108 | // enable the pin interrupt |

| bogdanm | 15:4892fe388435 | 109 | if (event == IRQ_RISE) { |

| bogdanm | 15:4892fe388435 | 110 | switch (obj->port) { |

| bogdanm | 15:4892fe388435 | 111 | case LPC_GPIO0_BASE: |

| bogdanm | 15:4892fe388435 | 112 | if (enable) { |

| bogdanm | 15:4892fe388435 | 113 | LPC_GPIOINT->IO0IntEnR |= 1 << obj->pin; |

| bogdanm | 15:4892fe388435 | 114 | } else { |

| bogdanm | 15:4892fe388435 | 115 | LPC_GPIOINT->IO0IntEnR &= ~(1 << obj->pin); |

| bogdanm | 15:4892fe388435 | 116 | } |

| bogdanm | 15:4892fe388435 | 117 | break; |

| bogdanm | 15:4892fe388435 | 118 | case LPC_GPIO2_BASE: |

| bogdanm | 15:4892fe388435 | 119 | if (enable) { |

| bogdanm | 15:4892fe388435 | 120 | LPC_GPIOINT->IO2IntEnR |= 1 << obj->pin; |

| bogdanm | 15:4892fe388435 | 121 | } else { |

| bogdanm | 15:4892fe388435 | 122 | LPC_GPIOINT->IO2IntEnR &= ~(1 << obj->pin); |

| bogdanm | 15:4892fe388435 | 123 | } |

| bogdanm | 15:4892fe388435 | 124 | break; |

| bogdanm | 15:4892fe388435 | 125 | } |

| bogdanm | 15:4892fe388435 | 126 | } else { |

| bogdanm | 15:4892fe388435 | 127 | switch (obj->port) { |

| bogdanm | 15:4892fe388435 | 128 | case LPC_GPIO0_BASE: |

| bogdanm | 15:4892fe388435 | 129 | if (enable) { |

| bogdanm | 15:4892fe388435 | 130 | LPC_GPIOINT->IO0IntEnF |= 1 << obj->pin; |

| bogdanm | 15:4892fe388435 | 131 | } else { |

| bogdanm | 15:4892fe388435 | 132 | LPC_GPIOINT->IO0IntEnF &= ~(1 << obj->pin); |

| bogdanm | 15:4892fe388435 | 133 | } |

| bogdanm | 15:4892fe388435 | 134 | break; |

| bogdanm | 15:4892fe388435 | 135 | case LPC_GPIO2_BASE: |

| bogdanm | 15:4892fe388435 | 136 | if (enable) { |

| bogdanm | 15:4892fe388435 | 137 | LPC_GPIOINT->IO2IntEnF |= 1 << obj->pin; |

| bogdanm | 15:4892fe388435 | 138 | } else { |

| bogdanm | 15:4892fe388435 | 139 | LPC_GPIOINT->IO2IntEnF &= ~(1 << obj->pin); |

| bogdanm | 15:4892fe388435 | 140 | } |

| bogdanm | 15:4892fe388435 | 141 | break; |

| bogdanm | 15:4892fe388435 | 142 | } |

| bogdanm | 15:4892fe388435 | 143 | } |

| bogdanm | 15:4892fe388435 | 144 | } |