Fork of mbed-src file paths change. LPC1114FN28 use only.

Fork of mbed-src by

Information

この情報は2013/10/28時点での解決方法です。

現在はmbed-src、標準ライブラリで問題なくコンパイルが可能です。

・使う物

LPC1114FN28

mbed SDK

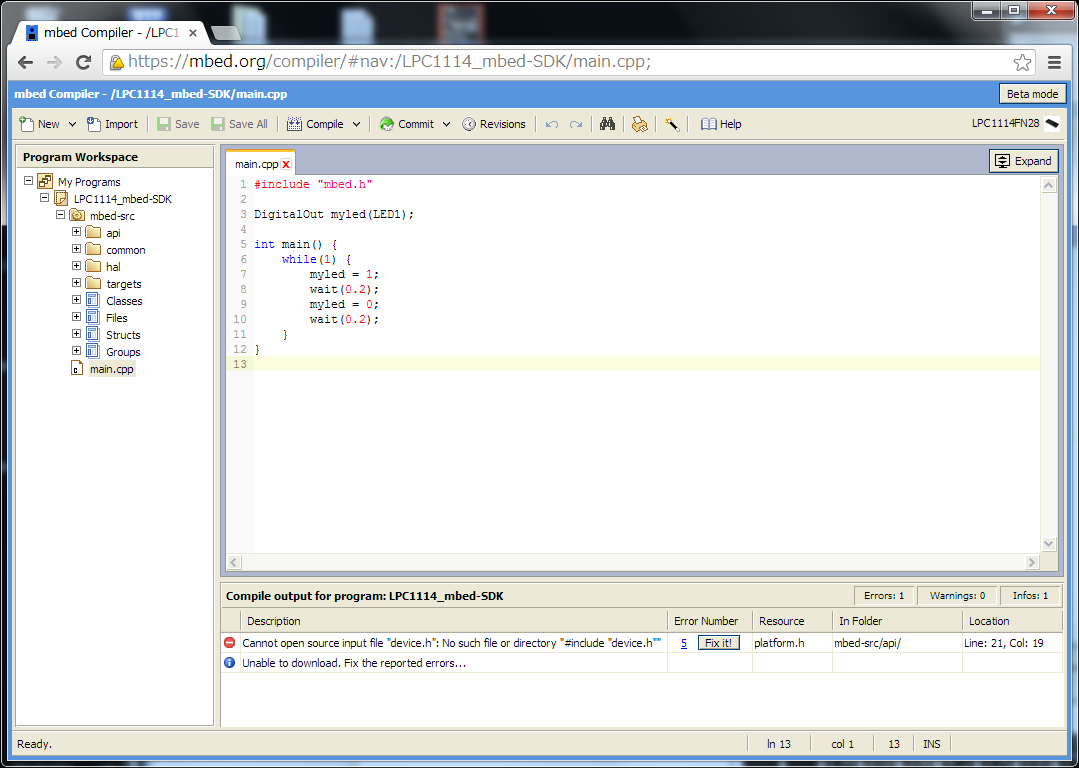

LPC1114FN28でmbed-SDKのLibraryを使うとCompile出来ない。(2013/10/28)

パスが通ってないだけのようなのでファイルを以下に移動する。

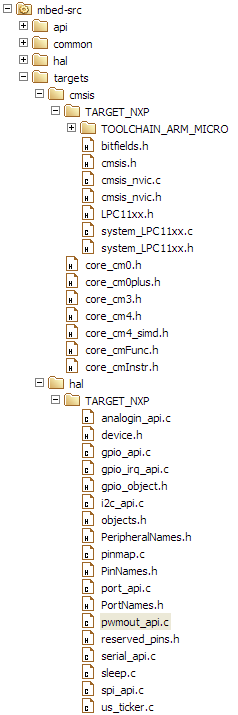

| mbed-src\targets\cmsis\TARGET_NXP\TARGET_LPC11XX_11CXX\ mbed-src\targets\cmsis\TARGET_NXP\TARGET_LPC11XX_11CXX\TARGET_LPC11XX\ |

にあるファイルをすべて

| mbed-src\targets\cmsis\TARGET_NXP\ |

へ移動

mbed-src\targets\cmsis\TARGET_NXP\TARGET_LPC11XX_11CXX\にある

| TOOLCHAIN_ARM_MICRO |

をフォルダごと

| mbed-src\targets\cmsis\TARGET_NXP\ |

へ移動

| mbed-src\targets\hal\TARGET_NXP\TARGET_LPC11XX_11CXX\ mbed-src\targets\hal\TARGET_NXP\TARGET_LPC11XX_11CXX\TARGET_LPC11XX\ |

にあるファイルをすべて

| mbed-src\targets\hal\TARGET_NXP\ |

へ移動

移動後は以下のような構成になると思います。

※不要なファイルは削除してあります。

|

ファイルの移動が面倒なので以下に本家からフォークしたライブラリを置いておきます。

Import librarymbed-src-LPC1114FN28

Fork of mbed-src file paths change. LPC1114FN28 use only.

エラーが出力される場合

"TOOLCHAIN_ARM_MICRO"が無いとエラーになる。

| Error: Undefined symbol _initial_sp (referred from entry2.o). Error: Undefined symbol _heap_base (referred from malloc.o). Error: Undefined symbol _heap_limit (referred from malloc.o). |

LPC1114FN28はMicrolibを使ってCompileされるため上記のエラーになるようです。

targets/hal/TARGET_NXP/TARGET_LPC43XX/README.txt@20:4263a77256ae, 2013-09-10 (annotated)

- Committer:

- bogdanm

- Date:

- Tue Sep 10 15:14:19 2013 +0300

- Revision:

- 20:4263a77256ae

Sync with git revision 171dda705c947bf910926a0b73d6a4797802554d

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| bogdanm | 20:4263a77256ae | 1 | mbed port to NXP LPC43xx |

| bogdanm | 20:4263a77256ae | 2 | ======================== |

| bogdanm | 20:4263a77256ae | 3 | Updated: 06/24/13 |

| bogdanm | 20:4263a77256ae | 4 | |

| bogdanm | 20:4263a77256ae | 5 | The NXP LPC43xx microcontrollers are the first to include multiple Cortex-M |

| bogdanm | 20:4263a77256ae | 6 | cores in a single microcontroller package. This port allows mbed developers |

| bogdanm | 20:4263a77256ae | 7 | to take advantage of the LPC43xx in their application using APIs that they |

| bogdanm | 20:4263a77256ae | 8 | are familiar with. Some of the key features of the LPC43xx include: |

| bogdanm | 20:4263a77256ae | 9 | |

| bogdanm | 20:4263a77256ae | 10 | * Dual core ARM Cortex-M4/M0 both capable of up to 204 MHz |

| bogdanm | 20:4263a77256ae | 11 | * Up to 264 KB SRAM, 1 MB internal flash |

| bogdanm | 20:4263a77256ae | 12 | * Two High-speed USB 2.0 interfaces |

| bogdanm | 20:4263a77256ae | 13 | * Ethernet MAC |

| bogdanm | 20:4263a77256ae | 14 | * LCD interface |

| bogdanm | 20:4263a77256ae | 15 | * Quad-SPI Flash Interface (SPIFI) |

| bogdanm | 20:4263a77256ae | 16 | * State Configurable Timer (SCT) |

| bogdanm | 20:4263a77256ae | 17 | * Serial GPIO (SGPIO) |

| bogdanm | 20:4263a77256ae | 18 | * Up to 164 GPIO |

| bogdanm | 20:4263a77256ae | 19 | |

| bogdanm | 20:4263a77256ae | 20 | The NXP LPC18xx is a single core Cortex-M3 implementation that is compatible |

| bogdanm | 20:4263a77256ae | 21 | with the LPC43XX for cost-sensitive applications not requiring multiple cores. |

| bogdanm | 20:4263a77256ae | 22 | |

| bogdanm | 20:4263a77256ae | 23 | mbed port to the LPC43XX - Micromint USA <support@micromint.com> |

| bogdanm | 20:4263a77256ae | 24 | |

| bogdanm | 20:4263a77256ae | 25 | Compatibility |

| bogdanm | 20:4263a77256ae | 26 | ------------- |

| bogdanm | 20:4263a77256ae | 27 | * This port has been tested with the following boards: |

| bogdanm | 20:4263a77256ae | 28 | Board MCU RAM/Flash |

| bogdanm | 20:4263a77256ae | 29 | Micromint Bambino 200 LPC4330 264K SRAM/4 MB SPIFI flash |

| bogdanm | 20:4263a77256ae | 30 | |

| bogdanm | 20:4263a77256ae | 31 | * Ethernet, USB and microSD filesystem drivers will be available when the |

| bogdanm | 20:4263a77256ae | 32 | Bambino 200E is released. |

| bogdanm | 20:4263a77256ae | 33 | |

| bogdanm | 20:4263a77256ae | 34 | * This port uses offline toolchains. Development and testing has been done |

| bogdanm | 20:4263a77256ae | 35 | mainly with the Keil MDK 4.70. Some testing has been done with IAR 6.5. |

| bogdanm | 20:4263a77256ae | 36 | Eventually Keil, IAR and GCC CodeRed will be supported. |

| bogdanm | 20:4263a77256ae | 37 | |

| bogdanm | 20:4263a77256ae | 38 | * CMSIS-DAP debugging is not currently implemented. To debug use a JTAG. |

| bogdanm | 20:4263a77256ae | 39 | The NXP DFU tool can be used for flash programming. |

| bogdanm | 20:4263a77256ae | 40 | |

| bogdanm | 20:4263a77256ae | 41 | * This port should support NXP LPC43XX and LPC18XX variants with a single |

| bogdanm | 20:4263a77256ae | 42 | codebase. The core declaration specifies the binaries to be built: |

| bogdanm | 20:4263a77256ae | 43 | mbed define CMSIS define MCU Target |

| bogdanm | 20:4263a77256ae | 44 | __CORTEX_M4 CORE_M4 LPC43xx Cortex-M4 |

| bogdanm | 20:4263a77256ae | 45 | __CORTEX_M0 CORE_M0 LPC43xx Cortex-M0 |

| bogdanm | 20:4263a77256ae | 46 | __CORTEX_M3 CORE_M3 LPC18xx Cortex-M3 |

| bogdanm | 20:4263a77256ae | 47 | These MCUs all share the peripheral IP, common driver code is feasible. |

| bogdanm | 20:4263a77256ae | 48 | Yet each variant can have different memory segments, peripherals, etc. |

| bogdanm | 20:4263a77256ae | 49 | Plus, each board design can integrate different external peripherals |

| bogdanm | 20:4263a77256ae | 50 | or interfaces. A future release of the mbed SDK and its build tools will |

| bogdanm | 20:4263a77256ae | 51 | support specifying the target board when building binaries. At this time |

| bogdanm | 20:4263a77256ae | 52 | building binaries for different targets requires an external project or |

| bogdanm | 20:4263a77256ae | 53 | Makefile. |

| bogdanm | 20:4263a77256ae | 54 | |

| bogdanm | 20:4263a77256ae | 55 | * No testing has been done with LPC18xx hardware. At the very least supporting |

| bogdanm | 20:4263a77256ae | 56 | the LPC18xx would require different compiler flags, additional CMSIS core_cm3 |

| bogdanm | 20:4263a77256ae | 57 | code as well as minor driver code changes. |

| bogdanm | 20:4263a77256ae | 58 | |

| bogdanm | 20:4263a77256ae | 59 | Notes |

| bogdanm | 20:4263a77256ae | 60 | ----- |

| bogdanm | 20:4263a77256ae | 61 | * On the LPC43xx the hardware pin name and the GPIO pin name are not the same, |

| bogdanm | 20:4263a77256ae | 62 | requiring different offsets for the SCU and GPIO registers. To simplify logic |

| bogdanm | 20:4263a77256ae | 63 | the pin identifier encodes the offsets. Macros are used for decoding. |

| bogdanm | 20:4263a77256ae | 64 | For example, P6_11 corresponds to GPIO3[7] and is encoded/decoded as follows: |

| bogdanm | 20:4263a77256ae | 65 | |

| bogdanm | 20:4263a77256ae | 66 | P6_11 = MBED_PIN(0x06, 11, 3, 7) = 0x032C0067 |

| bogdanm | 20:4263a77256ae | 67 | |

| bogdanm | 20:4263a77256ae | 68 | MBED_SCU_REG(P6_11) = 0x4008632C MBED_GPIO_PORT(P6_11) = 3 |

| bogdanm | 20:4263a77256ae | 69 | MBED_GPIO_REG(P6_11) = 0x400F4000 MBED_GPIO_PIN(P6_11) = 7 |

| bogdanm | 20:4263a77256ae | 70 | |

| bogdanm | 20:4263a77256ae | 71 | * The LPC43xx implements GPIO pin and group interrupts. Any pin in the 8 32-bit |

| bogdanm | 20:4263a77256ae | 72 | GPIO ports can interrupt (LPC4350 supports up to 164). On group interrupts a |

| bogdanm | 20:4263a77256ae | 73 | pin can only interrupt on the rising or falling edge, not both as required |

| bogdanm | 20:4263a77256ae | 74 | by the mbed InterruptIn class. Also, group interrupts can't be cleared |

| bogdanm | 20:4263a77256ae | 75 | individually. This implementation uses pin interrupts (8 on M4/M3, 1 on M0). |

| bogdanm | 20:4263a77256ae | 76 | A future implementation may provide group interrupt support. |