Fork of mbed-src file paths change. LPC1114FN28 use only.

Fork of mbed-src by

Information

この情報は2013/10/28時点での解決方法です。

現在はmbed-src、標準ライブラリで問題なくコンパイルが可能です。

・使う物

LPC1114FN28

mbed SDK

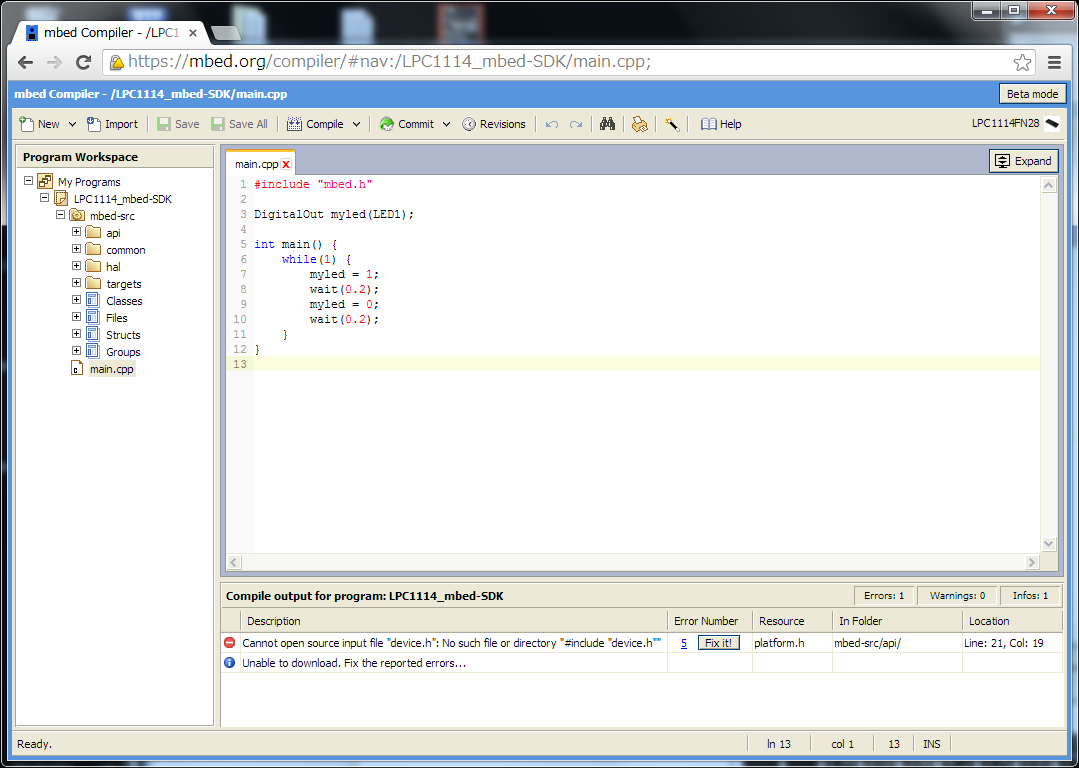

LPC1114FN28でmbed-SDKのLibraryを使うとCompile出来ない。(2013/10/28)

パスが通ってないだけのようなのでファイルを以下に移動する。

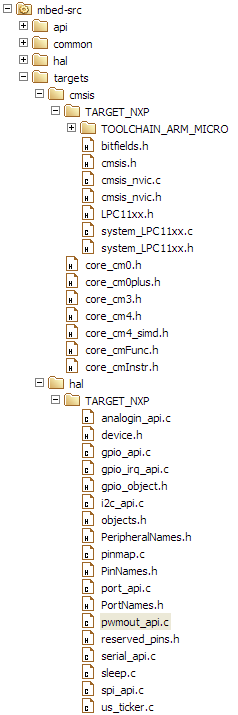

| mbed-src\targets\cmsis\TARGET_NXP\TARGET_LPC11XX_11CXX\ mbed-src\targets\cmsis\TARGET_NXP\TARGET_LPC11XX_11CXX\TARGET_LPC11XX\ |

にあるファイルをすべて

| mbed-src\targets\cmsis\TARGET_NXP\ |

へ移動

mbed-src\targets\cmsis\TARGET_NXP\TARGET_LPC11XX_11CXX\にある

| TOOLCHAIN_ARM_MICRO |

をフォルダごと

| mbed-src\targets\cmsis\TARGET_NXP\ |

へ移動

| mbed-src\targets\hal\TARGET_NXP\TARGET_LPC11XX_11CXX\ mbed-src\targets\hal\TARGET_NXP\TARGET_LPC11XX_11CXX\TARGET_LPC11XX\ |

にあるファイルをすべて

| mbed-src\targets\hal\TARGET_NXP\ |

へ移動

移動後は以下のような構成になると思います。

※不要なファイルは削除してあります。

|

ファイルの移動が面倒なので以下に本家からフォークしたライブラリを置いておきます。

Import librarymbed-src-LPC1114FN28

Fork of mbed-src file paths change. LPC1114FN28 use only.

エラーが出力される場合

"TOOLCHAIN_ARM_MICRO"が無いとエラーになる。

| Error: Undefined symbol _initial_sp (referred from entry2.o). Error: Undefined symbol _heap_base (referred from malloc.o). Error: Undefined symbol _heap_limit (referred from malloc.o). |

LPC1114FN28はMicrolibを使ってCompileされるため上記のエラーになるようです。

targets/cmsis/TARGET_NXP/TARGET_LPC176X/TOOLCHAIN_GCC_ARM/startup_LPC17xx.s@13:0645d8841f51, 2013-08-05 (annotated)

- Committer:

- bogdanm

- Date:

- Mon Aug 05 14:12:34 2013 +0300

- Revision:

- 13:0645d8841f51

- Parent:

- vendor/NXP/LPC1768/cmsis/GCC_ARM/startup_LPC17xx.s@10:3bc89ef62ce7

Update mbed sources to revision 64

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| emilmont | 10:3bc89ef62ce7 | 1 | /* File: startup_ARMCM3.s |

| emilmont | 10:3bc89ef62ce7 | 2 | * Purpose: startup file for Cortex-M3/M4 devices. Should use with |

| emilmont | 10:3bc89ef62ce7 | 3 | * GNU Tools for ARM Embedded Processors |

| emilmont | 10:3bc89ef62ce7 | 4 | * Version: V1.1 |

| emilmont | 10:3bc89ef62ce7 | 5 | * Date: 17 June 2011 |

| emilmont | 10:3bc89ef62ce7 | 6 | * |

| emilmont | 10:3bc89ef62ce7 | 7 | * Copyright (C) 2011 ARM Limited. All rights reserved. |

| emilmont | 10:3bc89ef62ce7 | 8 | * ARM Limited (ARM) is supplying this software for use with Cortex-M3/M4 |

| emilmont | 10:3bc89ef62ce7 | 9 | * processor based microcontrollers. This file can be freely distributed |

| emilmont | 10:3bc89ef62ce7 | 10 | * within development tools that are supporting such ARM based processors. |

| emilmont | 10:3bc89ef62ce7 | 11 | * |

| emilmont | 10:3bc89ef62ce7 | 12 | * THIS SOFTWARE IS PROVIDED "AS IS". NO WARRANTIES, WHETHER EXPRESS, IMPLIED |

| emilmont | 10:3bc89ef62ce7 | 13 | * OR STATUTORY, INCLUDING, BUT NOT LIMITED TO, IMPLIED WARRANTIES OF |

| emilmont | 10:3bc89ef62ce7 | 14 | * MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE APPLY TO THIS SOFTWARE. |

| emilmont | 10:3bc89ef62ce7 | 15 | * ARM SHALL NOT, IN ANY CIRCUMSTANCES, BE LIABLE FOR SPECIAL, INCIDENTAL, OR |

| emilmont | 10:3bc89ef62ce7 | 16 | * CONSEQUENTIAL DAMAGES, FOR ANY REASON WHATSOEVER. |

| emilmont | 10:3bc89ef62ce7 | 17 | */ |

| emilmont | 10:3bc89ef62ce7 | 18 | .syntax unified |

| emilmont | 10:3bc89ef62ce7 | 19 | .arch armv7-m |

| emilmont | 10:3bc89ef62ce7 | 20 | |

| emilmont | 10:3bc89ef62ce7 | 21 | /* Memory Model |

| emilmont | 10:3bc89ef62ce7 | 22 | The HEAP starts at the end of the DATA section and grows upward. |

| emilmont | 10:3bc89ef62ce7 | 23 | |

| emilmont | 10:3bc89ef62ce7 | 24 | The STACK starts at the end of the RAM and grows downward. |

| emilmont | 10:3bc89ef62ce7 | 25 | |

| emilmont | 10:3bc89ef62ce7 | 26 | The HEAP and stack STACK are only checked at compile time: |

| emilmont | 10:3bc89ef62ce7 | 27 | (DATA_SIZE + HEAP_SIZE + STACK_SIZE) < RAM_SIZE |

| emilmont | 10:3bc89ef62ce7 | 28 | |

| emilmont | 10:3bc89ef62ce7 | 29 | This is just a check for the bare minimum for the Heap+Stack area before |

| emilmont | 10:3bc89ef62ce7 | 30 | aborting compilation, it is not the run time limit: |

| emilmont | 10:3bc89ef62ce7 | 31 | Heap_Size + Stack_Size = 0x80 + 0x80 = 0x100 |

| emilmont | 10:3bc89ef62ce7 | 32 | */ |

| emilmont | 10:3bc89ef62ce7 | 33 | .section .stack |

| emilmont | 10:3bc89ef62ce7 | 34 | .align 3 |

| emilmont | 10:3bc89ef62ce7 | 35 | #ifdef __STACK_SIZE |

| emilmont | 10:3bc89ef62ce7 | 36 | .equ Stack_Size, __STACK_SIZE |

| emilmont | 10:3bc89ef62ce7 | 37 | #else |

| emilmont | 10:3bc89ef62ce7 | 38 | .equ Stack_Size, 0xc00 |

| emilmont | 10:3bc89ef62ce7 | 39 | #endif |

| emilmont | 10:3bc89ef62ce7 | 40 | .globl __StackTop |

| emilmont | 10:3bc89ef62ce7 | 41 | .globl __StackLimit |

| emilmont | 10:3bc89ef62ce7 | 42 | __StackLimit: |

| emilmont | 10:3bc89ef62ce7 | 43 | .space Stack_Size |

| emilmont | 10:3bc89ef62ce7 | 44 | .size __StackLimit, . - __StackLimit |

| emilmont | 10:3bc89ef62ce7 | 45 | __StackTop: |

| emilmont | 10:3bc89ef62ce7 | 46 | .size __StackTop, . - __StackTop |

| emilmont | 10:3bc89ef62ce7 | 47 | |

| emilmont | 10:3bc89ef62ce7 | 48 | .section .heap |

| emilmont | 10:3bc89ef62ce7 | 49 | .align 3 |

| emilmont | 10:3bc89ef62ce7 | 50 | #ifdef __HEAP_SIZE |

| emilmont | 10:3bc89ef62ce7 | 51 | .equ Heap_Size, __HEAP_SIZE |

| emilmont | 10:3bc89ef62ce7 | 52 | #else |

| emilmont | 10:3bc89ef62ce7 | 53 | .equ Heap_Size, 0x800 |

| emilmont | 10:3bc89ef62ce7 | 54 | #endif |

| emilmont | 10:3bc89ef62ce7 | 55 | .globl __HeapBase |

| emilmont | 10:3bc89ef62ce7 | 56 | .globl __HeapLimit |

| emilmont | 10:3bc89ef62ce7 | 57 | __HeapBase: |

| emilmont | 10:3bc89ef62ce7 | 58 | .space Heap_Size |

| emilmont | 10:3bc89ef62ce7 | 59 | .size __HeapBase, . - __HeapBase |

| emilmont | 10:3bc89ef62ce7 | 60 | __HeapLimit: |

| emilmont | 10:3bc89ef62ce7 | 61 | .size __HeapLimit, . - __HeapLimit |

| emilmont | 10:3bc89ef62ce7 | 62 | |

| emilmont | 10:3bc89ef62ce7 | 63 | .section .isr_vector |

| emilmont | 10:3bc89ef62ce7 | 64 | .align 2 |

| emilmont | 10:3bc89ef62ce7 | 65 | .globl __isr_vector |

| emilmont | 10:3bc89ef62ce7 | 66 | __isr_vector: |

| emilmont | 10:3bc89ef62ce7 | 67 | .long __StackTop /* Top of Stack */ |

| emilmont | 10:3bc89ef62ce7 | 68 | .long Reset_Handler /* Reset Handler */ |

| emilmont | 10:3bc89ef62ce7 | 69 | .long NMI_Handler /* NMI Handler */ |

| emilmont | 10:3bc89ef62ce7 | 70 | .long HardFault_Handler /* Hard Fault Handler */ |

| emilmont | 10:3bc89ef62ce7 | 71 | .long MemManage_Handler /* MPU Fault Handler */ |

| emilmont | 10:3bc89ef62ce7 | 72 | .long BusFault_Handler /* Bus Fault Handler */ |

| emilmont | 10:3bc89ef62ce7 | 73 | .long UsageFault_Handler /* Usage Fault Handler */ |

| emilmont | 10:3bc89ef62ce7 | 74 | .long 0 /* Reserved */ |

| emilmont | 10:3bc89ef62ce7 | 75 | .long 0 /* Reserved */ |

| emilmont | 10:3bc89ef62ce7 | 76 | .long 0 /* Reserved */ |

| emilmont | 10:3bc89ef62ce7 | 77 | .long 0 /* Reserved */ |

| emilmont | 10:3bc89ef62ce7 | 78 | .long SVC_Handler /* SVCall Handler */ |

| emilmont | 10:3bc89ef62ce7 | 79 | .long DebugMon_Handler /* Debug Monitor Handler */ |

| emilmont | 10:3bc89ef62ce7 | 80 | .long 0 /* Reserved */ |

| emilmont | 10:3bc89ef62ce7 | 81 | .long PendSV_Handler /* PendSV Handler */ |

| emilmont | 10:3bc89ef62ce7 | 82 | .long SysTick_Handler /* SysTick Handler */ |

| emilmont | 10:3bc89ef62ce7 | 83 | |

| emilmont | 10:3bc89ef62ce7 | 84 | /* External interrupts */ |

| emilmont | 10:3bc89ef62ce7 | 85 | .long WDT_IRQHandler /* 16: Watchdog Timer */ |

| emilmont | 10:3bc89ef62ce7 | 86 | .long TIMER0_IRQHandler /* 17: Timer0 */ |

| emilmont | 10:3bc89ef62ce7 | 87 | .long TIMER1_IRQHandler /* 18: Timer1 */ |

| emilmont | 10:3bc89ef62ce7 | 88 | .long TIMER2_IRQHandler /* 19: Timer2 */ |

| emilmont | 10:3bc89ef62ce7 | 89 | .long TIMER3_IRQHandler /* 20: Timer3 */ |

| emilmont | 10:3bc89ef62ce7 | 90 | .long UART0_IRQHandler /* 21: UART0 */ |

| emilmont | 10:3bc89ef62ce7 | 91 | .long UART1_IRQHandler /* 22: UART1 */ |

| emilmont | 10:3bc89ef62ce7 | 92 | .long UART2_IRQHandler /* 23: UART2 */ |

| emilmont | 10:3bc89ef62ce7 | 93 | .long UART3_IRQHandler /* 24: UART3 */ |

| emilmont | 10:3bc89ef62ce7 | 94 | .long PWM1_IRQHandler /* 25: PWM1 */ |

| emilmont | 10:3bc89ef62ce7 | 95 | .long I2C0_IRQHandler /* 26: I2C0 */ |

| emilmont | 10:3bc89ef62ce7 | 96 | .long I2C1_IRQHandler /* 27: I2C1 */ |

| emilmont | 10:3bc89ef62ce7 | 97 | .long I2C2_IRQHandler /* 28: I2C2 */ |

| emilmont | 10:3bc89ef62ce7 | 98 | .long SPI_IRQHandler /* 29: SPI */ |

| emilmont | 10:3bc89ef62ce7 | 99 | .long SSP0_IRQHandler /* 30: SSP0 */ |

| emilmont | 10:3bc89ef62ce7 | 100 | .long SSP1_IRQHandler /* 31: SSP1 */ |

| emilmont | 10:3bc89ef62ce7 | 101 | .long PLL0_IRQHandler /* 32: PLL0 Lock (Main PLL) */ |

| emilmont | 10:3bc89ef62ce7 | 102 | .long RTC_IRQHandler /* 33: Real Time Clock */ |

| emilmont | 10:3bc89ef62ce7 | 103 | .long EINT0_IRQHandler /* 34: External Interrupt 0 */ |

| emilmont | 10:3bc89ef62ce7 | 104 | .long EINT1_IRQHandler /* 35: External Interrupt 1 */ |

| emilmont | 10:3bc89ef62ce7 | 105 | .long EINT2_IRQHandler /* 36: External Interrupt 2 */ |

| emilmont | 10:3bc89ef62ce7 | 106 | .long EINT3_IRQHandler /* 37: External Interrupt 3 */ |

| emilmont | 10:3bc89ef62ce7 | 107 | .long ADC_IRQHandler /* 38: A/D Converter */ |

| emilmont | 10:3bc89ef62ce7 | 108 | .long BOD_IRQHandler /* 39: Brown-Out Detect */ |

| emilmont | 10:3bc89ef62ce7 | 109 | .long USB_IRQHandler /* 40: USB */ |

| emilmont | 10:3bc89ef62ce7 | 110 | .long CAN_IRQHandler /* 41: CAN */ |

| emilmont | 10:3bc89ef62ce7 | 111 | .long DMA_IRQHandler /* 42: General Purpose DMA */ |

| emilmont | 10:3bc89ef62ce7 | 112 | .long I2S_IRQHandler /* 43: I2S */ |

| emilmont | 10:3bc89ef62ce7 | 113 | .long ENET_IRQHandler /* 44: Ethernet */ |

| emilmont | 10:3bc89ef62ce7 | 114 | .long RIT_IRQHandler /* 45: Repetitive Interrupt Timer */ |

| emilmont | 10:3bc89ef62ce7 | 115 | .long MCPWM_IRQHandler /* 46: Motor Control PWM */ |

| emilmont | 10:3bc89ef62ce7 | 116 | .long QEI_IRQHandler /* 47: Quadrature Encoder Interface */ |

| emilmont | 10:3bc89ef62ce7 | 117 | .long PLL1_IRQHandler /* 48: PLL1 Lock (USB PLL) */ |

| emilmont | 10:3bc89ef62ce7 | 118 | .long USBActivity_IRQHandler /* 49: USB Activity */ |

| emilmont | 10:3bc89ef62ce7 | 119 | .long CANActivity_IRQHandler /* 50: CAN Activity */ |

| emilmont | 10:3bc89ef62ce7 | 120 | |

| emilmont | 10:3bc89ef62ce7 | 121 | .size __isr_vector, . - __isr_vector |

| emilmont | 10:3bc89ef62ce7 | 122 | |

| emilmont | 10:3bc89ef62ce7 | 123 | .text |

| emilmont | 10:3bc89ef62ce7 | 124 | .thumb |

| emilmont | 10:3bc89ef62ce7 | 125 | .thumb_func |

| emilmont | 10:3bc89ef62ce7 | 126 | .align 2 |

| emilmont | 10:3bc89ef62ce7 | 127 | .globl Reset_Handler |

| emilmont | 10:3bc89ef62ce7 | 128 | .type Reset_Handler, %function |

| emilmont | 10:3bc89ef62ce7 | 129 | Reset_Handler: |

| emilmont | 10:3bc89ef62ce7 | 130 | /* Loop to copy data from read only memory to RAM. The ranges |

| emilmont | 10:3bc89ef62ce7 | 131 | * of copy from/to are specified by following symbols evaluated in |

| emilmont | 10:3bc89ef62ce7 | 132 | * linker script. |

| emilmont | 10:3bc89ef62ce7 | 133 | * _etext: End of code section, i.e., begin of data sections to copy from. |

| emilmont | 10:3bc89ef62ce7 | 134 | * __data_start__/__data_end__: RAM address range that data should be |

| emilmont | 10:3bc89ef62ce7 | 135 | * copied to. Both must be aligned to 4 bytes boundary. */ |

| emilmont | 10:3bc89ef62ce7 | 136 | |

| emilmont | 10:3bc89ef62ce7 | 137 | ldr r1, =__etext |

| emilmont | 10:3bc89ef62ce7 | 138 | ldr r2, =__data_start__ |

| emilmont | 10:3bc89ef62ce7 | 139 | ldr r3, =__data_end__ |

| emilmont | 10:3bc89ef62ce7 | 140 | |

| emilmont | 10:3bc89ef62ce7 | 141 | .flash_to_ram_loop: |

| emilmont | 10:3bc89ef62ce7 | 142 | cmp r2, r3 |

| emilmont | 10:3bc89ef62ce7 | 143 | ittt lt |

| emilmont | 10:3bc89ef62ce7 | 144 | ldrlt r0, [r1], #4 |

| emilmont | 10:3bc89ef62ce7 | 145 | strlt r0, [r2], #4 |

| emilmont | 10:3bc89ef62ce7 | 146 | blt .flash_to_ram_loop |

| emilmont | 10:3bc89ef62ce7 | 147 | |

| emilmont | 10:3bc89ef62ce7 | 148 | ldr r0, =SystemInit |

| emilmont | 10:3bc89ef62ce7 | 149 | blx r0 |

| emilmont | 10:3bc89ef62ce7 | 150 | ldr r0, =_start |

| emilmont | 10:3bc89ef62ce7 | 151 | bx r0 |

| emilmont | 10:3bc89ef62ce7 | 152 | .pool |

| emilmont | 10:3bc89ef62ce7 | 153 | .size Reset_Handler, . - Reset_Handler |

| emilmont | 10:3bc89ef62ce7 | 154 | |

| emilmont | 10:3bc89ef62ce7 | 155 | /* Macro to define default handlers. Default handler |

| emilmont | 10:3bc89ef62ce7 | 156 | * will be weak symbol and just dead loops. They can be |

| emilmont | 10:3bc89ef62ce7 | 157 | * overwritten by other handlers */ |

| emilmont | 10:3bc89ef62ce7 | 158 | .macro def_default_handler handler_name |

| emilmont | 10:3bc89ef62ce7 | 159 | .align 1 |

| emilmont | 10:3bc89ef62ce7 | 160 | .thumb_func |

| emilmont | 10:3bc89ef62ce7 | 161 | .weak \handler_name |

| emilmont | 10:3bc89ef62ce7 | 162 | .type \handler_name, %function |

| emilmont | 10:3bc89ef62ce7 | 163 | \handler_name : |

| emilmont | 10:3bc89ef62ce7 | 164 | b . |

| emilmont | 10:3bc89ef62ce7 | 165 | .size \handler_name, . - \handler_name |

| emilmont | 10:3bc89ef62ce7 | 166 | .endm |

| emilmont | 10:3bc89ef62ce7 | 167 | |

| emilmont | 10:3bc89ef62ce7 | 168 | def_default_handler NMI_Handler |

| emilmont | 10:3bc89ef62ce7 | 169 | def_default_handler HardFault_Handler |

| emilmont | 10:3bc89ef62ce7 | 170 | def_default_handler MemManage_Handler |

| emilmont | 10:3bc89ef62ce7 | 171 | def_default_handler BusFault_Handler |

| emilmont | 10:3bc89ef62ce7 | 172 | def_default_handler UsageFault_Handler |

| emilmont | 10:3bc89ef62ce7 | 173 | def_default_handler SVC_Handler |

| emilmont | 10:3bc89ef62ce7 | 174 | def_default_handler DebugMon_Handler |

| emilmont | 10:3bc89ef62ce7 | 175 | def_default_handler PendSV_Handler |

| emilmont | 10:3bc89ef62ce7 | 176 | def_default_handler SysTick_Handler |

| emilmont | 10:3bc89ef62ce7 | 177 | def_default_handler Default_Handler |

| emilmont | 10:3bc89ef62ce7 | 178 | |

| emilmont | 10:3bc89ef62ce7 | 179 | def_default_handler WDT_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 180 | def_default_handler TIMER0_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 181 | def_default_handler TIMER1_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 182 | def_default_handler TIMER2_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 183 | def_default_handler TIMER3_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 184 | def_default_handler UART0_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 185 | def_default_handler UART1_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 186 | def_default_handler UART2_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 187 | def_default_handler UART3_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 188 | def_default_handler PWM1_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 189 | def_default_handler I2C0_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 190 | def_default_handler I2C1_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 191 | def_default_handler I2C2_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 192 | def_default_handler SPI_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 193 | def_default_handler SSP0_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 194 | def_default_handler SSP1_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 195 | def_default_handler PLL0_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 196 | def_default_handler RTC_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 197 | def_default_handler EINT0_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 198 | def_default_handler EINT1_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 199 | def_default_handler EINT2_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 200 | def_default_handler EINT3_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 201 | def_default_handler ADC_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 202 | def_default_handler BOD_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 203 | def_default_handler USB_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 204 | def_default_handler CAN_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 205 | def_default_handler DMA_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 206 | def_default_handler I2S_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 207 | def_default_handler ENET_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 208 | def_default_handler RIT_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 209 | def_default_handler MCPWM_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 210 | def_default_handler QEI_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 211 | def_default_handler PLL1_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 212 | def_default_handler USBActivity_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 213 | def_default_handler CANActivity_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 214 | |

| emilmont | 10:3bc89ef62ce7 | 215 | .weak DEF_IRQHandler |

| emilmont | 10:3bc89ef62ce7 | 216 | .set DEF_IRQHandler, Default_Handler |

| emilmont | 10:3bc89ef62ce7 | 217 | |

| emilmont | 10:3bc89ef62ce7 | 218 | .end |

| emilmont | 10:3bc89ef62ce7 | 219 |