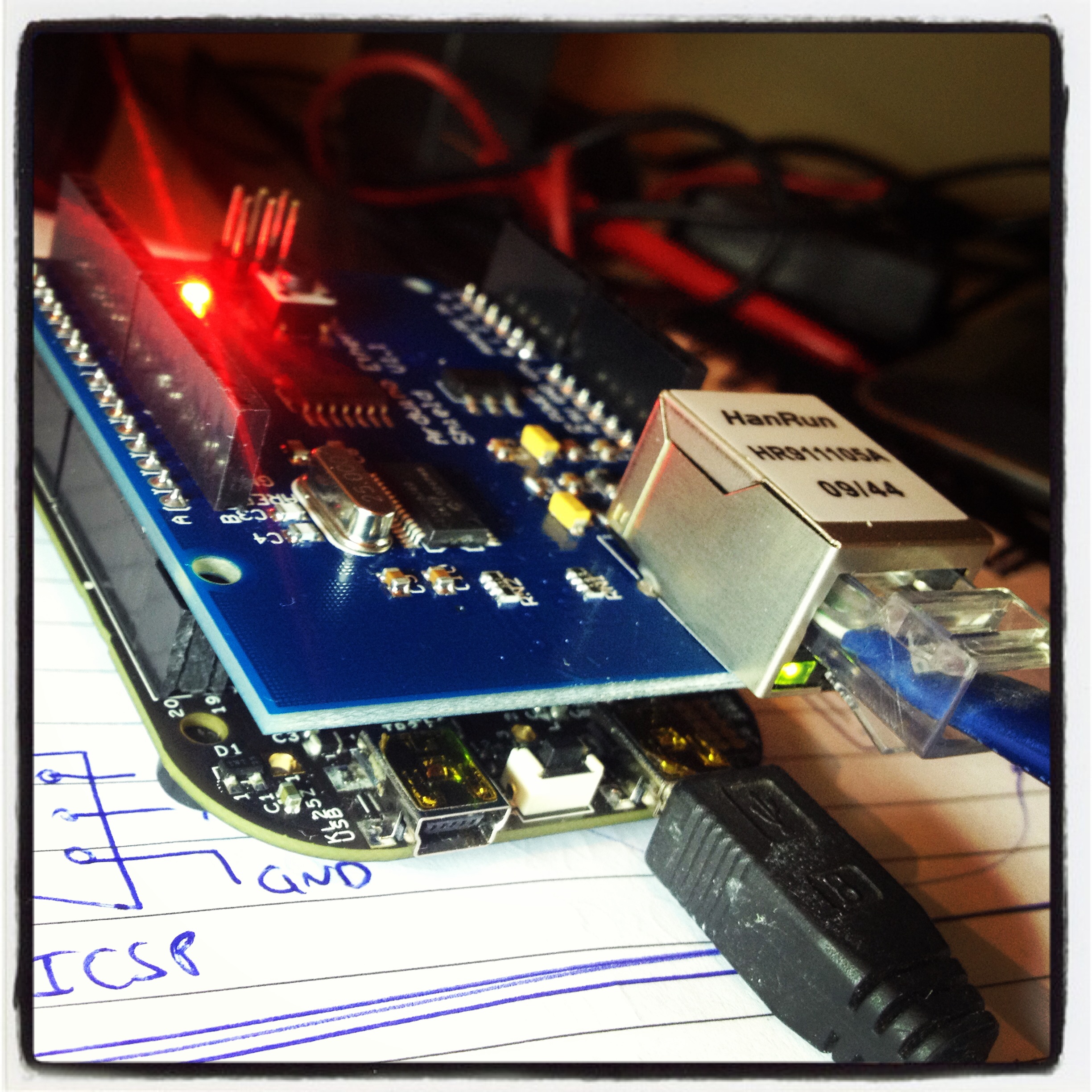

Ethernet support based on arduino shield for FRDM KL25Z.

This project is an initial support for ethernet in FRDM KL25Z. It is based on commercial arduino shield and its driver.

The TCP/IP stack is not included yet but it is possible to send and receive ethernet frames at this moment.

Original code is GPL2. My modified code is under the very restrictive license Beerware.

main.cpp@1:49a4de80f92f, 2013-09-20 (annotated)

- Committer:

- marcelobarrosalmeida

- Date:

- Fri Sep 20 21:43:46 2013 +0000

- Revision:

- 1:49a4de80f92f

- Parent:

- 0:5ae4b6e22715

Adding mac comment

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| marcelobarrosalmeida | 0:5ae4b6e22715 | 1 | #include "mbed.h" |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 2 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 3 | // Microchip ENC28J60 Ethernet Interface Driver |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 4 | // Author: Guido Socher |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 5 | // Copyright: GPL V2 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 6 | // |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 7 | // Based on the enc28j60.c file from the AVRlib library by Pascal Stang. |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 8 | // For AVRlib See http://www.procyonengineering.com/ |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 9 | // Used with explicit permission of Pascal Stang. |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 10 | // |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 11 | // 2010-05-20 <jc@wippler.nl> |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 12 | // 2013-09-20 Modified for mbed by Marcelo Barros de Almeida <marcelobarrosalmeida@gmail.com> |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 13 | // http://shiningbits.com/blog/ |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 14 | // http://br.linkedin.com/in/marcelobarrosalmeida/ |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 15 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 16 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 17 | // ENC28J60 Control Registers |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 18 | // Control register definitions are a combination of address, |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 19 | // bank number, and Ethernet/MAC/PHY indicator bits. |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 20 | // - Register address (bits 0-4) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 21 | // - Bank number (bits 5-6) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 22 | // - MAC/PHY indicator (bit 7) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 23 | #define ADDR_MASK 0x1F |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 24 | #define BANK_MASK 0x60 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 25 | #define SPRD_MASK 0x80 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 26 | // All-bank registers |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 27 | #define EIE 0x1B |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 28 | #define EIR 0x1C |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 29 | #define ESTAT 0x1D |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 30 | #define ECON2 0x1E |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 31 | #define ECON1 0x1F |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 32 | // Bank 0 registers |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 33 | #define ERDPT (0x00|0x00) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 34 | #define EWRPT (0x02|0x00) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 35 | #define ETXST (0x04|0x00) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 36 | #define ETXND (0x06|0x00) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 37 | #define ERXST (0x08|0x00) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 38 | #define ERXND (0x0A|0x00) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 39 | #define ERXRDPT (0x0C|0x00) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 40 | // #define ERXWRPT (0x0E|0x00) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 41 | #define EDMAST (0x10|0x00) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 42 | #define EDMAND (0x12|0x00) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 43 | // #define EDMADST (0x14|0x00) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 44 | #define EDMACS (0x16|0x00) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 45 | // Bank 1 registers |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 46 | #define EHT0 (0x00|0x20) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 47 | #define EHT1 (0x01|0x20) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 48 | #define EHT2 (0x02|0x20) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 49 | #define EHT3 (0x03|0x20) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 50 | #define EHT4 (0x04|0x20) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 51 | #define EHT5 (0x05|0x20) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 52 | #define EHT6 (0x06|0x20) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 53 | #define EHT7 (0x07|0x20) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 54 | #define EPMM0 (0x08|0x20) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 55 | #define EPMM1 (0x09|0x20) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 56 | #define EPMM2 (0x0A|0x20) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 57 | #define EPMM3 (0x0B|0x20) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 58 | #define EPMM4 (0x0C|0x20) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 59 | #define EPMM5 (0x0D|0x20) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 60 | #define EPMM6 (0x0E|0x20) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 61 | #define EPMM7 (0x0F|0x20) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 62 | #define EPMCS (0x10|0x20) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 63 | // #define EPMO (0x14|0x20) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 64 | #define EWOLIE (0x16|0x20) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 65 | #define EWOLIR (0x17|0x20) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 66 | #define ERXFCON (0x18|0x20) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 67 | #define EPKTCNT (0x19|0x20) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 68 | // Bank 2 registers |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 69 | #define MACON1 (0x00|0x40|0x80) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 70 | #define MACON2 (0x01|0x40|0x80) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 71 | #define MACON3 (0x02|0x40|0x80) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 72 | #define MACON4 (0x03|0x40|0x80) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 73 | #define MABBIPG (0x04|0x40|0x80) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 74 | #define MAIPG (0x06|0x40|0x80) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 75 | #define MACLCON1 (0x08|0x40|0x80) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 76 | #define MACLCON2 (0x09|0x40|0x80) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 77 | #define MAMXFL (0x0A|0x40|0x80) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 78 | #define MAPHSUP (0x0D|0x40|0x80) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 79 | #define MICON (0x11|0x40|0x80) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 80 | #define MICMD (0x12|0x40|0x80) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 81 | #define MIREGADR (0x14|0x40|0x80) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 82 | #define MIWR (0x16|0x40|0x80) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 83 | #define MIRD (0x18|0x40|0x80) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 84 | // Bank 3 registers |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 85 | #define MAADR1 (0x00|0x60|0x80) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 86 | #define MAADR0 (0x01|0x60|0x80) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 87 | #define MAADR3 (0x02|0x60|0x80) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 88 | #define MAADR2 (0x03|0x60|0x80) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 89 | #define MAADR5 (0x04|0x60|0x80) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 90 | #define MAADR4 (0x05|0x60|0x80) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 91 | #define EBSTSD (0x06|0x60) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 92 | #define EBSTCON (0x07|0x60) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 93 | #define EBSTCS (0x08|0x60) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 94 | #define MISTAT (0x0A|0x60|0x80) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 95 | #define EREVID (0x12|0x60) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 96 | #define ECOCON (0x15|0x60) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 97 | #define EFLOCON (0x17|0x60) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 98 | #define EPAUS (0x18|0x60) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 99 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 100 | // ENC28J60 ERXFCON Register Bit Definitions |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 101 | #define ERXFCON_UCEN 0x80 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 102 | #define ERXFCON_ANDOR 0x40 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 103 | #define ERXFCON_CRCEN 0x20 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 104 | #define ERXFCON_PMEN 0x10 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 105 | #define ERXFCON_MPEN 0x08 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 106 | #define ERXFCON_HTEN 0x04 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 107 | #define ERXFCON_MCEN 0x02 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 108 | #define ERXFCON_BCEN 0x01 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 109 | // ENC28J60 EIE Register Bit Definitions |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 110 | #define EIE_INTIE 0x80 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 111 | #define EIE_PKTIE 0x40 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 112 | #define EIE_DMAIE 0x20 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 113 | #define EIE_LINKIE 0x10 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 114 | #define EIE_TXIE 0x08 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 115 | #define EIE_WOLIE 0x04 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 116 | #define EIE_TXERIE 0x02 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 117 | #define EIE_RXERIE 0x01 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 118 | // ENC28J60 EIR Register Bit Definitions |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 119 | #define EIR_PKTIF 0x40 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 120 | #define EIR_DMAIF 0x20 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 121 | #define EIR_LINKIF 0x10 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 122 | #define EIR_TXIF 0x08 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 123 | #define EIR_WOLIF 0x04 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 124 | #define EIR_TXERIF 0x02 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 125 | #define EIR_RXERIF 0x01 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 126 | // ENC28J60 ESTAT Register Bit Definitions |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 127 | #define ESTAT_INT 0x80 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 128 | #define ESTAT_LATECOL 0x10 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 129 | #define ESTAT_RXBUSY 0x04 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 130 | #define ESTAT_TXABRT 0x02 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 131 | #define ESTAT_CLKRDY 0x01 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 132 | // ENC28J60 ECON2 Register Bit Definitions |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 133 | #define ECON2_AUTOINC 0x80 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 134 | #define ECON2_PKTDEC 0x40 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 135 | #define ECON2_PWRSV 0x20 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 136 | #define ECON2_VRPS 0x08 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 137 | // ENC28J60 ECON1 Register Bit Definitions |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 138 | #define ECON1_TXRST 0x80 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 139 | #define ECON1_RXRST 0x40 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 140 | #define ECON1_DMAST 0x20 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 141 | #define ECON1_CSUMEN 0x10 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 142 | #define ECON1_TXRTS 0x08 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 143 | #define ECON1_RXEN 0x04 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 144 | #define ECON1_BSEL1 0x02 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 145 | #define ECON1_BSEL0 0x01 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 146 | // ENC28J60 MACON1 Register Bit Definitions |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 147 | #define MACON1_LOOPBK 0x10 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 148 | #define MACON1_TXPAUS 0x08 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 149 | #define MACON1_RXPAUS 0x04 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 150 | #define MACON1_PASSALL 0x02 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 151 | #define MACON1_MARXEN 0x01 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 152 | // ENC28J60 MACON2 Register Bit Definitions |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 153 | #define MACON2_MARST 0x80 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 154 | #define MACON2_RNDRST 0x40 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 155 | #define MACON2_MARXRST 0x08 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 156 | #define MACON2_RFUNRST 0x04 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 157 | #define MACON2_MATXRST 0x02 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 158 | #define MACON2_TFUNRST 0x01 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 159 | // ENC28J60 MACON3 Register Bit Definitions |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 160 | #define MACON3_PADCFG2 0x80 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 161 | #define MACON3_PADCFG1 0x40 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 162 | #define MACON3_PADCFG0 0x20 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 163 | #define MACON3_TXCRCEN 0x10 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 164 | #define MACON3_PHDRLEN 0x08 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 165 | #define MACON3_HFRMLEN 0x04 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 166 | #define MACON3_FRMLNEN 0x02 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 167 | #define MACON3_FULDPX 0x01 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 168 | // ENC28J60 MICMD Register Bit Definitions |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 169 | #define MICMD_MIISCAN 0x02 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 170 | #define MICMD_MIIRD 0x01 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 171 | // ENC28J60 MISTAT Register Bit Definitions |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 172 | #define MISTAT_NVALID 0x04 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 173 | #define MISTAT_SCAN 0x02 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 174 | #define MISTAT_BUSY 0x01 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 175 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 176 | // ENC28J60 EBSTCON Register Bit Definitions |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 177 | #define EBSTCON_PSV2 0x80 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 178 | #define EBSTCON_PSV1 0x40 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 179 | #define EBSTCON_PSV0 0x20 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 180 | #define EBSTCON_PSEL 0x10 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 181 | #define EBSTCON_TMSEL1 0x08 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 182 | #define EBSTCON_TMSEL0 0x04 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 183 | #define EBSTCON_TME 0x02 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 184 | #define EBSTCON_BISTST 0x01 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 185 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 186 | // PHY registers |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 187 | #define PHCON1 0x00 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 188 | #define PHSTAT1 0x01 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 189 | #define PHHID1 0x02 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 190 | #define PHHID2 0x03 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 191 | #define PHCON2 0x10 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 192 | #define PHSTAT2 0x11 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 193 | #define PHIE 0x12 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 194 | #define PHIR 0x13 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 195 | #define PHLCON 0x14 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 196 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 197 | // ENC28J60 PHY PHCON1 Register Bit Definitions |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 198 | #define PHCON1_PRST 0x8000 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 199 | #define PHCON1_PLOOPBK 0x4000 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 200 | #define PHCON1_PPWRSV 0x0800 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 201 | #define PHCON1_PDPXMD 0x0100 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 202 | // ENC28J60 PHY PHSTAT1 Register Bit Definitions |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 203 | #define PHSTAT1_PFDPX 0x1000 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 204 | #define PHSTAT1_PHDPX 0x0800 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 205 | #define PHSTAT1_LLSTAT 0x0004 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 206 | #define PHSTAT1_JBSTAT 0x0002 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 207 | // ENC28J60 PHY PHCON2 Register Bit Definitions |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 208 | #define PHCON2_FRCLINK 0x4000 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 209 | #define PHCON2_TXDIS 0x2000 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 210 | #define PHCON2_JABBER 0x0400 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 211 | #define PHCON2_HDLDIS 0x0100 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 212 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 213 | // ENC28J60 Packet Control Byte Bit Definitions |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 214 | #define PKTCTRL_PHUGEEN 0x08 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 215 | #define PKTCTRL_PPADEN 0x04 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 216 | #define PKTCTRL_PCRCEN 0x02 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 217 | #define PKTCTRL_POVERRIDE 0x01 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 218 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 219 | // SPI operation codes |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 220 | #define ENC28J60_READ_CTRL_REG 0x00 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 221 | #define ENC28J60_READ_BUF_MEM 0x3A |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 222 | #define ENC28J60_WRITE_CTRL_REG 0x40 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 223 | #define ENC28J60_WRITE_BUF_MEM 0x7A |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 224 | #define ENC28J60_BIT_FIELD_SET 0x80 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 225 | #define ENC28J60_BIT_FIELD_CLR 0xA0 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 226 | #define ENC28J60_SOFT_RESET 0xFF |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 227 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 228 | // The RXSTART_INIT must be zero. See Rev. B4 Silicon Errata point 5. |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 229 | // Buffer boundaries applied to internal 8K ram |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 230 | // the entire available packet buffer space is allocated |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 231 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 232 | #define RXSTART_INIT 0x0000 // start of RX buffer, room for 2 packets |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 233 | #define RXSTOP_INIT 0x0BFF // end of RX buffer |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 234 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 235 | #define TXSTART_INIT 0x0C00 // start of TX buffer, room for 1 packet |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 236 | #define TXSTOP_INIT 0x11FF // end of TX buffer |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 237 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 238 | #define SCRATCH_START 0x1200 // start of scratch area |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 239 | #define SCRATCH_LIMIT 0x2000 // past end of area, i.e. 3.5 Kb |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 240 | #define SCRATCH_PAGE_SHIFT 6 // addressing is in pages of 64 bytes |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 241 | #define SCRATCH_PAGE_SIZE (1 << SCRATCH_PAGE_SHIFT) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 242 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 243 | // max frame length which the conroller will accept: |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 244 | // (note: maximum ethernet frame length would be 1518) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 245 | #define MAX_FRAMELEN 1500 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 246 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 247 | #define FULL_SPEED 1 // switch to full-speed SPI for bulk transfers |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 248 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 249 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 250 | SPI spi(PTD2,PTD3,PTD1); // mosi, miso, sclk |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 251 | DigitalOut cs(PTD0); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 252 | DigitalIn ethInt(PTD4); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 253 | Serial pc(USBTX, USBRX); // tx, rx |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 254 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 255 | static uint8_t Enc28j60Bank; |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 256 | static int gNextPacketPtr; |

| marcelobarrosalmeida | 1:49a4de80f92f | 257 | uint8_t macaddr[] = {0x00, 0xFF, 0x7A, 0xA5, 0x06, 0xDD}; // fake mac, please change it |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 258 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 259 | static void enableChip(void) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 260 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 261 | cs = 0; |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 262 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 263 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 264 | static void disableChip(void) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 265 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 266 | cs = 1; |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 267 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 268 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 269 | static uint8_t readOp(uint8_t op, uint8_t address) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 270 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 271 | uint8_t result; |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 272 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 273 | //pc.printf("readOp %02X %02X\r\n",op,address); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 274 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 275 | enableChip(); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 276 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 277 | spi.write(op | (address & ADDR_MASK)); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 278 | result = spi.write(0x00); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 279 | if (address & 0x80) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 280 | result = spi.write(0x00); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 281 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 282 | disableChip(); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 283 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 284 | //pc.printf("readOp result %02X\r\n",result); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 285 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 286 | return result; |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 287 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 288 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 289 | static void writeOp(uint8_t op, uint8_t address, uint8_t data) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 290 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 291 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 292 | //pc.printf("writeOp %02X %02X %02X\r\n",op,address,data); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 293 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 294 | enableChip(); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 295 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 296 | spi.write(op | (address & ADDR_MASK)); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 297 | spi.write(data); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 298 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 299 | disableChip(); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 300 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 301 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 302 | static void SetBank (uint8_t address) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 303 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 304 | if ((address & BANK_MASK) != Enc28j60Bank) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 305 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 306 | writeOp(ENC28J60_BIT_FIELD_CLR, ECON1, ECON1_BSEL1|ECON1_BSEL0); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 307 | Enc28j60Bank = address & BANK_MASK; |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 308 | writeOp(ENC28J60_BIT_FIELD_SET, ECON1, Enc28j60Bank>>5); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 309 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 310 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 311 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 312 | static uint8_t readRegByte (uint8_t address) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 313 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 314 | SetBank(address); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 315 | return readOp(ENC28J60_READ_CTRL_REG, address); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 316 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 317 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 318 | static uint16_t readReg(uint8_t address) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 319 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 320 | return readRegByte(address) + (readRegByte(address+1) << 8); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 321 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 322 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 323 | static void writeRegByte (uint8_t address, uint8_t data) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 324 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 325 | SetBank(address); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 326 | writeOp(ENC28J60_WRITE_CTRL_REG, address, data); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 327 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 328 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 329 | static void writeReg(uint8_t address, uint16_t data) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 330 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 331 | writeRegByte(address, data); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 332 | writeRegByte(address + 1, data >> 8); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 333 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 334 | void enableBroadcast () |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 335 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 336 | writeRegByte(ERXFCON, ERXFCON_UCEN|ERXFCON_CRCEN|ERXFCON_PMEN|ERXFCON_BCEN); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 337 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 338 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 339 | void disableBroadcast () |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 340 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 341 | writeRegByte(ERXFCON, ERXFCON_UCEN|ERXFCON_CRCEN|ERXFCON_PMEN); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 342 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 343 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 344 | void disableMulticast () |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 345 | { // disable multicast filter , enable multicast reception |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 346 | writeRegByte(ERXFCON, ERXFCON_CRCEN); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 347 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 348 | static uint16_t readPhyByte(uint8_t address) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 349 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 350 | writeRegByte(MIREGADR, address); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 351 | writeRegByte(MICMD, MICMD_MIIRD); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 352 | while (readRegByte(MISTAT) & MISTAT_BUSY); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 353 | writeRegByte(MICMD, 0x00); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 354 | return readRegByte(MIRD+1); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 355 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 356 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 357 | static void writePhy(uint8_t address, uint16_t data) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 358 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 359 | writeRegByte(MIREGADR, address); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 360 | writeReg(MIWR, data); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 361 | while (readRegByte(MISTAT) & MISTAT_BUSY) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 362 | ; |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 363 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 364 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 365 | static void writeBuf(const uint8_t* data, uint16_t len) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 366 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 367 | enableChip(); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 368 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 369 | spi.write(ENC28J60_WRITE_BUF_MEM); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 370 | while (len--) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 371 | spi.write(*data++); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 372 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 373 | disableChip(); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 374 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 375 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 376 | static void readBuf(uint8_t* data, uint16_t len) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 377 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 378 | enableChip(); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 379 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 380 | spi.write(ENC28J60_READ_BUF_MEM); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 381 | while (len--) { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 382 | *data++ = spi.write(0x00); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 383 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 384 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 385 | disableChip(); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 386 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 387 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 388 | uint8_t isLinkUp(void) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 389 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 390 | return (readPhyByte(PHSTAT2) >> 2) & 1; |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 391 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 392 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 393 | void packetSend(uint8_t *buffer, uint16_t len) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 394 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 395 | pc.printf("packetSend %d bytes ...\r\n",len); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 396 | while (readOp(ENC28J60_READ_CTRL_REG, ECON1) & ECON1_TXRTS) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 397 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 398 | if (readRegByte(EIR) & EIR_TXERIF) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 399 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 400 | writeOp(ENC28J60_BIT_FIELD_SET, ECON1, ECON1_TXRST); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 401 | writeOp(ENC28J60_BIT_FIELD_CLR, ECON1, ECON1_TXRST); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 402 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 403 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 404 | writeReg(EWRPT, TXSTART_INIT); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 405 | writeReg(ETXND, TXSTART_INIT+len); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 406 | writeOp(ENC28J60_WRITE_BUF_MEM, 0, 0x00); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 407 | writeBuf(buffer,len); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 408 | writeOp(ENC28J60_BIT_FIELD_SET, ECON1, ECON1_TXRTS); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 409 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 410 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 411 | uint16_t packetReceive(uint8_t *buffer, uint16_t bufferSize) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 412 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 413 | uint16_t len = 0; |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 414 | if (readRegByte(EPKTCNT) > 0) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 415 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 416 | writeReg(ERDPT, gNextPacketPtr); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 417 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 418 | struct { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 419 | uint16_t nextPacket; |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 420 | uint16_t byteCount; |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 421 | uint16_t status; |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 422 | } header; |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 423 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 424 | readBuf((uint8_t*) &header, sizeof header); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 425 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 426 | gNextPacketPtr = header.nextPacket; |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 427 | len = header.byteCount - 4; //remove the CRC count |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 428 | if (len>bufferSize-1) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 429 | len=bufferSize-1; |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 430 | if ((header.status & 0x80)==0) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 431 | len = 0; |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 432 | else |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 433 | readBuf(buffer,len); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 434 | buffer[len] = 0; |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 435 | if (gNextPacketPtr - 1 > RXSTOP_INIT) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 436 | writeReg(ERXRDPT, RXSTOP_INIT); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 437 | else |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 438 | writeReg(ERXRDPT, gNextPacketPtr - 1); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 439 | writeOp(ENC28J60_BIT_FIELD_SET, ECON2, ECON2_PKTDEC); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 440 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 441 | return len; |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 442 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 443 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 444 | // Contributed by Alex M. Based on code from: http://blog.derouineau.fr |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 445 | // /2011/07/putting-enc28j60-ethernet-controler-in-sleep-mode/ |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 446 | void powerDown() |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 447 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 448 | writeOp(ENC28J60_BIT_FIELD_CLR, ECON1, ECON1_RXEN); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 449 | while(readRegByte(ESTAT) & ESTAT_RXBUSY); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 450 | while(readRegByte(ECON1) & ECON1_TXRTS); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 451 | writeOp(ENC28J60_BIT_FIELD_SET, ECON2, ECON2_VRPS); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 452 | writeOp(ENC28J60_BIT_FIELD_SET, ECON2, ECON2_PWRSV); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 453 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 454 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 455 | void powerUp() |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 456 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 457 | writeOp(ENC28J60_BIT_FIELD_CLR, ECON2, ECON2_PWRSV); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 458 | while(!readRegByte(ESTAT) & ESTAT_CLKRDY); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 459 | writeOp(ENC28J60_BIT_FIELD_SET, ECON1, ECON1_RXEN); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 460 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 461 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 462 | static int initialize(void) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 463 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 464 | uint8_t rev; |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 465 | writeOp(ENC28J60_SOFT_RESET, 0, ENC28J60_SOFT_RESET); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 466 | wait(2); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 467 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 468 | while(!readOp(ENC28J60_READ_CTRL_REG, ESTAT) & ESTAT_CLKRDY); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 469 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 470 | gNextPacketPtr = RXSTART_INIT; |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 471 | writeReg(ERXST, RXSTART_INIT); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 472 | writeReg(ERXRDPT, RXSTART_INIT); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 473 | writeReg(ERXND, RXSTOP_INIT); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 474 | writeReg(ETXST, TXSTART_INIT); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 475 | writeReg(ETXND, TXSTOP_INIT); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 476 | enableBroadcast(); // change to add ERXFCON_BCEN recommended by epam |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 477 | writeReg(EPMM0, 0x303f); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 478 | writeReg(EPMCS, 0xf7f9); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 479 | writeRegByte(MACON1, MACON1_MARXEN|MACON1_TXPAUS|MACON1_RXPAUS); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 480 | writeRegByte(MACON2, 0x00); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 481 | writeOp(ENC28J60_BIT_FIELD_SET, MACON3, |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 482 | MACON3_PADCFG0|MACON3_TXCRCEN|MACON3_FRMLNEN); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 483 | writeReg(MAIPG, 0x0C12); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 484 | writeRegByte(MABBIPG, 0x12); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 485 | writeReg(MAMXFL, MAX_FRAMELEN); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 486 | writeRegByte(MAADR5, macaddr[0]); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 487 | writeRegByte(MAADR4, macaddr[1]); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 488 | writeRegByte(MAADR3, macaddr[2]); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 489 | writeRegByte(MAADR2, macaddr[3]); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 490 | writeRegByte(MAADR1, macaddr[4]); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 491 | writeRegByte(MAADR0, macaddr[5]); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 492 | writePhy(PHCON2, PHCON2_HDLDIS); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 493 | SetBank(ECON1); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 494 | writeOp(ENC28J60_BIT_FIELD_SET, EIE, EIE_INTIE|EIE_PKTIE); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 495 | writeOp(ENC28J60_BIT_FIELD_SET, ECON1, ECON1_RXEN); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 496 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 497 | rev = readRegByte(EREVID); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 498 | // microchip forgot to step the number on the silcon when they |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 499 | // released the revision B7. 6 is now rev B7. We still have |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 500 | // to see what they do when they release B8. At the moment |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 501 | // there is no B8 out yet |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 502 | if (rev > 5) ++rev; |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 503 | return rev; |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 504 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 505 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 506 | static void setupSPI(void) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 507 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 508 | spi.format(8,0); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 509 | spi.frequency(8000000); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 510 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 511 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 512 | int main(void) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 513 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 514 | uint8_t rev; |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 515 | static uint8_t tx_frame[] = |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 516 | { 0xff, 0xff, 0xff, 0xff, 0xff, 0xff, |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 517 | macaddr[0], macaddr[1], macaddr[2], macaddr[3], macaddr[4], macaddr[5], |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 518 | 0x80, 0x00, |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 519 | 0x53, 0x68, 0x69, 0x6E, 0x69, 0x6E, 0x67, 0x20, 0x42, 0x69, |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 520 | 0x74, 0x73, 0x2C, 0x20, 0x65, 0x6D, 0x62, 0x65, 0x64, 0x64, |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 521 | 0x65, 0x64, 0x20, 0x69, 0x6E, 0x74, 0x65, 0x6C, 0x6C, 0x69, |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 522 | 0x67, 0x65, 0x6E, 0x63, 0x65, 0x20, 0x21 |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 523 | }; // dummy frame |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 524 | static uint8_t rx_frame[1560]; |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 525 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 526 | pc.printf("Setup SPI ...\r\n"); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 527 | setupSPI(); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 528 | pc.printf("Setup ethernet ...\r\n"); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 529 | rev = initialize(); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 530 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 531 | pc.printf("REV = %d\r\n",rev); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 532 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 533 | while(1) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 534 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 535 | uint8_t link = isLinkUp(); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 536 | pc.printf("LINK = %d\r\n",isLinkUp()); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 537 | if(link) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 538 | break; |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 539 | wait(1); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 540 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 541 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 542 | while(1) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 543 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 544 | uint8_t reg = readRegByte(EIR); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 545 | if(reg & EIR_PKTIF) |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 546 | { |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 547 | uint16_t len; |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 548 | pc.printf("INTERRUPT = %2X\r\n",reg); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 549 | len = packetReceive(rx_frame,1560); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 550 | pc.printf("RX %d bytes\r\n",len); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 551 | writeOp(ENC28J60_BIT_FIELD_CLR, EIR, EIR_PKTIF); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 552 | |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 553 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 554 | packetSend(tx_frame,51); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 555 | wait(1); |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 556 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 557 | } |

| marcelobarrosalmeida | 0:5ae4b6e22715 | 558 |