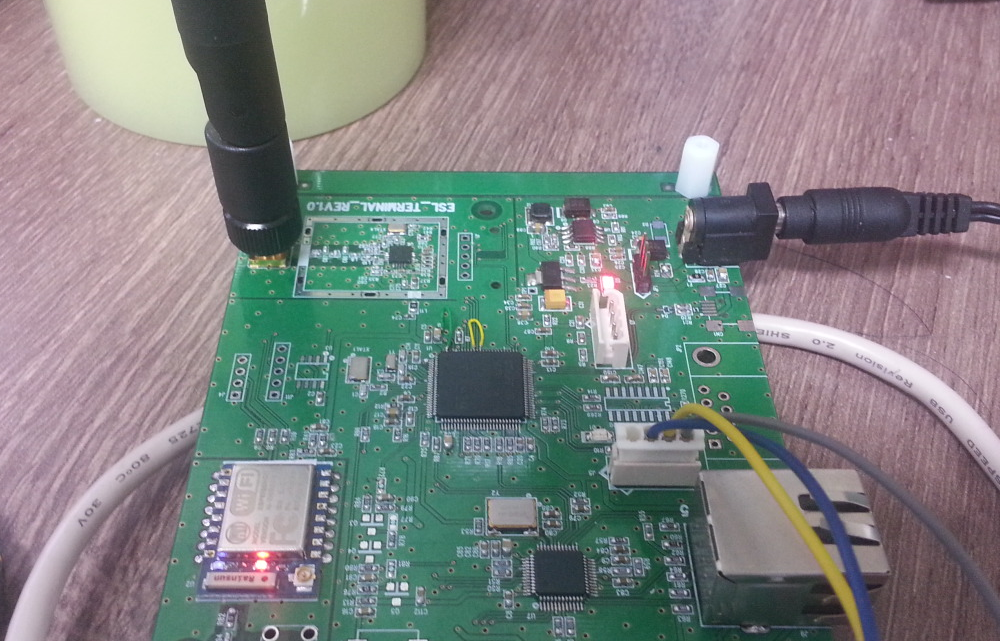

This is modified program from original CC1101_Transceiver. CC1101 Test succeeded STM32-F407 platform. Feature are improved little bit.

Dependencies: mbed

TI CC1101 chip is embedded along with STM32-F407 MCU.

CC1101.cpp@2:54c832c68208, 2015-03-31 (annotated)

- Committer:

- hillkim7

- Date:

- Tue Mar 31 08:48:00 2015 +0000

- Revision:

- 2:54c832c68208

- Parent:

- 1:e96096a7b90b

Fix misspelled word.

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| tmav123 | 0:9df942ea84f4 | 1 | |

| tmav123 | 0:9df942ea84f4 | 2 | #include "CC1101.h" |

| tmav123 | 0:9df942ea84f4 | 3 | |

| tmav123 | 0:9df942ea84f4 | 4 | #define RF_0db |

| tmav123 | 0:9df942ea84f4 | 5 | //#define RF_10db |

| tmav123 | 0:9df942ea84f4 | 6 | /////////////////////////////////////////////////////////////////////////////////////// |

| hillkim7 | 2:54c832c68208 | 7 | CC1101::CC1101(PinName mosi, PinName miso, PinName clk, PinName csn, PinName RDmiso, PinName gdo0, PinName gdo2): |

| hillkim7 | 2:54c832c68208 | 8 | _spi(mosi, miso, clk), _csn(csn), _RDmiso(RDmiso), _gdo0(gdo0), _gdo2(gdo2) |

| tmav123 | 0:9df942ea84f4 | 9 | { |

| tmav123 | 0:9df942ea84f4 | 10 | _csn = 1; |

| tmav123 | 0:9df942ea84f4 | 11 | |

| tmav123 | 0:9df942ea84f4 | 12 | // Setup the spi for 8 bit data, high steady state clock, |

| tmav123 | 0:9df942ea84f4 | 13 | // second edge capture, with a 1MHz clock rate |

| tmav123 | 0:9df942ea84f4 | 14 | _spi.format(8,0); |

| tmav123 | 0:9df942ea84f4 | 15 | _spi.frequency(1000000); |

| tmav123 | 0:9df942ea84f4 | 16 | |

| tmav123 | 0:9df942ea84f4 | 17 | POWER_UP_RESET_CCxxx0(); |

| tmav123 | 0:9df942ea84f4 | 18 | Strobe(CCxxx0_SRX); |

| tmav123 | 0:9df942ea84f4 | 19 | } |

| tmav123 | 0:9df942ea84f4 | 20 | /////////////////////////////////////////////////////////////////////////////////////// |

| hillkim7 | 1:e96096a7b90b | 21 | RF_SETTINGS rfSettings = { // 433Mhz, 9600Bauds |

| tmav123 | 0:9df942ea84f4 | 22 | 0x06, // FSCTRL1 Frequency Synthesizer Control - IF:152.343Khz |

| tmav123 | 0:9df942ea84f4 | 23 | 0x07, // IOCFG0 GDO0 Output Pin Configuration - Packet received and CRC OK |

| tmav123 | 0:9df942ea84f4 | 24 | 0x00, // FSCTRL0 Frequency Synthesizer Control - Freq offset |

| tmav123 | 0:9df942ea84f4 | 25 | 0x10, // FREQ2 Frequency Control Word, High Byte - 433.999 Mhz |

| tmav123 | 0:9df942ea84f4 | 26 | 0xB1, // FREQ1 Frequency Control Word, Middle Byte |

| tmav123 | 0:9df942ea84f4 | 27 | 0x3B, // FREQ0 Frequency Control Word, Low Byte |

| tmav123 | 0:9df942ea84f4 | 28 | 0xF8, // MDMCFG4 Modem Configuration - BW: 58.035Khz |

| tmav123 | 0:9df942ea84f4 | 29 | 0x83, // MDMCFG3 Modem Configuration - 9595 Baud |

| tmav123 | 0:9df942ea84f4 | 30 | 0x13, // MDMCFG2 Modem Configuration - 30/32 sync word bits - Manchester disable - GFSK - Digital DC filter enable |

| tmav123 | 0:9df942ea84f4 | 31 | 0x22, // MDMCFG1 Modem Configuration - num of preamble bytes:4 - FEC disable |

| tmav123 | 0:9df942ea84f4 | 32 | 0xF8, // MDMCFG0 Modem Configuration - Channel spacing: 199.951Khz |

| tmav123 | 0:9df942ea84f4 | 33 | 0x00, // CHANNR Channel Number |

| tmav123 | 0:9df942ea84f4 | 34 | 0x15, // DEVIATN Modem Deviation Setting - 5.157Khz |

| hillkim7 | 1:e96096a7b90b | 35 | 0x56, // FREND1 Front End RX Configuration |

| tmav123 | 0:9df942ea84f4 | 36 | 0x10, // FREND0 Front End TX Configuration |

| tmav123 | 0:9df942ea84f4 | 37 | 0x18, // MCSM0 Main Radio Control State Machine Configuration - PO timeout: 64(149-155us) - Auto calibrate from idle to rx/tx |

| tmav123 | 0:9df942ea84f4 | 38 | 0x16, // FOCCFG Frequency Offset Compensation Configuration |

| tmav123 | 0:9df942ea84f4 | 39 | 0x6C, // BSCFG Bit Synchronization Configuration |

| tmav123 | 0:9df942ea84f4 | 40 | 0x03, // AGCCTRL2 AGC Control - target amplitude: 33dB - Maximum possible LNA + LNA 2 gain - All gain settings can be used |

| tmav123 | 0:9df942ea84f4 | 41 | 0x40, // AGCCTRL1 AGC Control - LNA gain decreased first |

| hillkim7 | 1:e96096a7b90b | 42 | 0x91, // AGCCTRL0 AGC Control - Medium hysterisis - Filter Samples: 16 - Normal AGC operation |

| tmav123 | 0:9df942ea84f4 | 43 | 0xE9, // FSCAL3 Frequency Synthesizer Calibration |

| tmav123 | 0:9df942ea84f4 | 44 | 0x2A, // FSCAL2 Frequency Synthesizer Calibration |

| tmav123 | 0:9df942ea84f4 | 45 | 0x00, // FSCAL1 Frequency Synthesizer Calibration |

| tmav123 | 0:9df942ea84f4 | 46 | 0x1F, // FSCAL0 Frequency Synthesizer Calibration |

| tmav123 | 0:9df942ea84f4 | 47 | 0x59, // FSTEST Frequency Synthesizer Calibration Control |

| tmav123 | 0:9df942ea84f4 | 48 | 0x88, // TEST2 Various Test Settings |

| tmav123 | 0:9df942ea84f4 | 49 | 0x31, // TEST1 Various Test Settings |

| tmav123 | 0:9df942ea84f4 | 50 | 0x09, // TEST0 Various Test Settings |

| tmav123 | 0:9df942ea84f4 | 51 | 0x07, // FIFOTHR RX FIFO and TX FIFO Thresholds - Bytes in TX FIFO:33 - Bytes in RX FIFO:32 |

| tmav123 | 0:9df942ea84f4 | 52 | 0x06, // IOCFG2 GDO2 Output Pin Configuration - Sync word received/sent - end of packet |

| tmav123 | 0:9df942ea84f4 | 53 | 0x04, // PKTCTRL1 Packet Automation Control - No address check - Automatic flush of RX FIFO is disable - sync word is always accepted |

| tmav123 | 0:9df942ea84f4 | 54 | 0x05, // PKTCTRL0 Packet Automation Control - whitening is off - RX/TX data normal mode - CRC calculation in TX and CRC check in RX - Variable packet length |

| hillkim7 | 1:e96096a7b90b | 55 | 0x00, // ADDR Device Address |

| tmav123 | 0:9df942ea84f4 | 56 | 0xFF, // PKTLEN Packet Length |

| tmav123 | 0:9df942ea84f4 | 57 | 0x3F, // MCSM1 Main Radio Control State Machine Configuration |

| tmav123 | 0:9df942ea84f4 | 58 | }; |

| tmav123 | 0:9df942ea84f4 | 59 | #ifdef RF_0db |

| tmav123 | 0:9df942ea84f4 | 60 | // PATABLE (0 dBm output power) |

| tmav123 | 0:9df942ea84f4 | 61 | char paTable[] = {0x60, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00}; |

| tmav123 | 0:9df942ea84f4 | 62 | #endif |

| tmav123 | 0:9df942ea84f4 | 63 | #ifdef RF_10db |

| tmav123 | 0:9df942ea84f4 | 64 | // PATABLE (10 dBm output power) |

| tmav123 | 0:9df942ea84f4 | 65 | char paTable[] = {0xC0, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00}; |

| tmav123 | 0:9df942ea84f4 | 66 | #endif |

| tmav123 | 0:9df942ea84f4 | 67 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 68 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 69 | // Macro to reset the CCxxx0 and wait for it to be ready |

| tmav123 | 0:9df942ea84f4 | 70 | void CC1101::RESET_CCxxx0(void) |

| tmav123 | 0:9df942ea84f4 | 71 | { |

| tmav123 | 0:9df942ea84f4 | 72 | // while (_RDmiso); |

| hillkim7 | 1:e96096a7b90b | 73 | _csn = 0; |

| tmav123 | 0:9df942ea84f4 | 74 | wait(0.000002); |

| hillkim7 | 1:e96096a7b90b | 75 | while (_RDmiso); |

| hillkim7 | 1:e96096a7b90b | 76 | _spi.write(CCxxx0_SRES); |

| tmav123 | 0:9df942ea84f4 | 77 | wait(0.000002); |

| hillkim7 | 1:e96096a7b90b | 78 | _csn = 1; |

| tmav123 | 0:9df942ea84f4 | 79 | } |

| tmav123 | 0:9df942ea84f4 | 80 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 81 | // Macro to reset the CCxxx0 after power_on and wait for it to be ready |

| tmav123 | 0:9df942ea84f4 | 82 | // IMPORTANT NOTICE: |

| tmav123 | 0:9df942ea84f4 | 83 | // The file Wait.c must be included if this macro shall be used |

| tmav123 | 0:9df942ea84f4 | 84 | // The file is located under: ..\Lib\Chipcon\Hal\CCxx00 |

| tmav123 | 0:9df942ea84f4 | 85 | // |

| tmav123 | 0:9df942ea84f4 | 86 | // min 40 us |

| tmav123 | 0:9df942ea84f4 | 87 | // <-----------------------> |

| tmav123 | 0:9df942ea84f4 | 88 | // CSn |--| |--------------------| |----------- |

| tmav123 | 0:9df942ea84f4 | 89 | // | | | | | |

| tmav123 | 0:9df942ea84f4 | 90 | // -- ---------- |

| tmav123 | 0:9df942ea84f4 | 91 | // |

| tmav123 | 0:9df942ea84f4 | 92 | // MISO |--------------- |

| tmav123 | 0:9df942ea84f4 | 93 | // - - - - - - - - - - - - - - - -| | |

| tmav123 | 0:9df942ea84f4 | 94 | // -- |

| tmav123 | 0:9df942ea84f4 | 95 | // Unknown / don't care |

| tmav123 | 0:9df942ea84f4 | 96 | // |

| tmav123 | 0:9df942ea84f4 | 97 | // MOSI - - - - - - - - - - - - - - - ---------- - - - - - |

| tmav123 | 0:9df942ea84f4 | 98 | // | SRES | |

| tmav123 | 0:9df942ea84f4 | 99 | // - - - - - - - - - - - - - - - ---------- - - - - - |

| tmav123 | 0:9df942ea84f4 | 100 | // |

| tmav123 | 0:9df942ea84f4 | 101 | void CC1101::POWER_UP_RESET_CCxxx0(void) |

| tmav123 | 0:9df942ea84f4 | 102 | { |

| hillkim7 | 1:e96096a7b90b | 103 | _csn = 1; |

| hillkim7 | 1:e96096a7b90b | 104 | wait(1e-6); |

| hillkim7 | 1:e96096a7b90b | 105 | _csn = 0; |

| hillkim7 | 1:e96096a7b90b | 106 | wait(1e-6); |

| hillkim7 | 1:e96096a7b90b | 107 | _csn = 1; |

| hillkim7 | 1:e96096a7b90b | 108 | wait(41e-6); |

| hillkim7 | 1:e96096a7b90b | 109 | RESET_CCxxx0(); |

| tmav123 | 0:9df942ea84f4 | 110 | } |

| tmav123 | 0:9df942ea84f4 | 111 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 112 | // void Strobe(unsigned char strobe) |

| tmav123 | 0:9df942ea84f4 | 113 | // |

| tmav123 | 0:9df942ea84f4 | 114 | // DESCRIPTION: |

| tmav123 | 0:9df942ea84f4 | 115 | // Function for writing a strobe command to the CCxxx0 |

| tmav123 | 0:9df942ea84f4 | 116 | // |

| tmav123 | 0:9df942ea84f4 | 117 | // ARGUMENTS: |

| tmav123 | 0:9df942ea84f4 | 118 | // unsigned char strobe |

| tmav123 | 0:9df942ea84f4 | 119 | // Strobe command |

| tmav123 | 0:9df942ea84f4 | 120 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 121 | unsigned char CC1101::Strobe(unsigned char strobe) |

| tmav123 | 0:9df942ea84f4 | 122 | { |

| tmav123 | 0:9df942ea84f4 | 123 | unsigned char x; |

| tmav123 | 0:9df942ea84f4 | 124 | wait(0.000005); |

| tmav123 | 0:9df942ea84f4 | 125 | _csn = 0; |

| tmav123 | 0:9df942ea84f4 | 126 | wait(0.000002); |

| tmav123 | 0:9df942ea84f4 | 127 | while (_RDmiso); |

| tmav123 | 0:9df942ea84f4 | 128 | x = _spi.write(strobe); |

| tmav123 | 0:9df942ea84f4 | 129 | wait(0.000002); |

| tmav123 | 0:9df942ea84f4 | 130 | _csn = 1; |

| tmav123 | 0:9df942ea84f4 | 131 | return x; |

| tmav123 | 0:9df942ea84f4 | 132 | }// Strobe |

| tmav123 | 0:9df942ea84f4 | 133 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 134 | // unsigned char ReadStatus(unsigned char addr) |

| tmav123 | 0:9df942ea84f4 | 135 | // |

| tmav123 | 0:9df942ea84f4 | 136 | // DESCRIPTION: |

| tmav123 | 0:9df942ea84f4 | 137 | // This function reads a CCxxx0 status register. |

| tmav123 | 0:9df942ea84f4 | 138 | // |

| tmav123 | 0:9df942ea84f4 | 139 | // ARGUMENTS: |

| tmav123 | 0:9df942ea84f4 | 140 | // unsigned char addr |

| tmav123 | 0:9df942ea84f4 | 141 | // Address of the CCxxx0 status register to be accessed. |

| tmav123 | 0:9df942ea84f4 | 142 | // |

| tmav123 | 0:9df942ea84f4 | 143 | // RETURN VALUE: |

| tmav123 | 0:9df942ea84f4 | 144 | // unsigned char |

| tmav123 | 0:9df942ea84f4 | 145 | // Value of the accessed CCxxx0 status register. |

| tmav123 | 0:9df942ea84f4 | 146 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 147 | unsigned char CC1101::ReadStatus(unsigned char addr) |

| tmav123 | 0:9df942ea84f4 | 148 | { |

| tmav123 | 0:9df942ea84f4 | 149 | unsigned char x; |

| tmav123 | 0:9df942ea84f4 | 150 | wait(0.000005); |

| tmav123 | 0:9df942ea84f4 | 151 | _csn = 0; |

| tmav123 | 0:9df942ea84f4 | 152 | wait(0.000002); |

| tmav123 | 0:9df942ea84f4 | 153 | while (_RDmiso); |

| tmav123 | 0:9df942ea84f4 | 154 | _spi.write(addr | READ_BURST); |

| tmav123 | 0:9df942ea84f4 | 155 | x = _spi.write(0); |

| tmav123 | 0:9df942ea84f4 | 156 | wait(0.000002); |

| tmav123 | 0:9df942ea84f4 | 157 | _csn = 1; |

| tmav123 | 0:9df942ea84f4 | 158 | return x; |

| tmav123 | 0:9df942ea84f4 | 159 | }// ReadStatus |

| tmav123 | 0:9df942ea84f4 | 160 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 161 | // void WriteRfSettings(RF_SETTINGS *pRfSettings) |

| tmav123 | 0:9df942ea84f4 | 162 | // |

| tmav123 | 0:9df942ea84f4 | 163 | // DESCRIPTION: |

| tmav123 | 0:9df942ea84f4 | 164 | // This function is used to configure the CCxxx0 based on a given rf setting |

| tmav123 | 0:9df942ea84f4 | 165 | // |

| tmav123 | 0:9df942ea84f4 | 166 | // ARGUMENTS: |

| tmav123 | 0:9df942ea84f4 | 167 | // RF_SETTINGS *pRfSettings |

| tmav123 | 0:9df942ea84f4 | 168 | // Pointer to a struct containing rf register settings |

| tmav123 | 0:9df942ea84f4 | 169 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 170 | void CC1101::WriteRfSettings(RF_SETTINGS *pRfSettings) |

| tmav123 | 0:9df942ea84f4 | 171 | { |

| tmav123 | 0:9df942ea84f4 | 172 | // Write register settings |

| tmav123 | 0:9df942ea84f4 | 173 | WriteReg(CCxxx0_FSCTRL1, pRfSettings->FSCTRL1); |

| tmav123 | 0:9df942ea84f4 | 174 | WriteReg(CCxxx0_FSCTRL0, pRfSettings->FSCTRL0); |

| tmav123 | 0:9df942ea84f4 | 175 | WriteReg(CCxxx0_FREQ2, pRfSettings->FREQ2); |

| tmav123 | 0:9df942ea84f4 | 176 | WriteReg(CCxxx0_FREQ1, pRfSettings->FREQ1); |

| tmav123 | 0:9df942ea84f4 | 177 | WriteReg(CCxxx0_FREQ0, pRfSettings->FREQ0); |

| tmav123 | 0:9df942ea84f4 | 178 | WriteReg(CCxxx0_MDMCFG4, pRfSettings->MDMCFG4); |

| tmav123 | 0:9df942ea84f4 | 179 | WriteReg(CCxxx0_MDMCFG3, pRfSettings->MDMCFG3); |

| tmav123 | 0:9df942ea84f4 | 180 | WriteReg(CCxxx0_MDMCFG2, pRfSettings->MDMCFG2); |

| tmav123 | 0:9df942ea84f4 | 181 | WriteReg(CCxxx0_MDMCFG1, pRfSettings->MDMCFG1); |

| tmav123 | 0:9df942ea84f4 | 182 | WriteReg(CCxxx0_MDMCFG0, pRfSettings->MDMCFG0); |

| tmav123 | 0:9df942ea84f4 | 183 | WriteReg(CCxxx0_CHANNR, pRfSettings->CHANNR); |

| tmav123 | 0:9df942ea84f4 | 184 | WriteReg(CCxxx0_DEVIATN, pRfSettings->DEVIATN); |

| tmav123 | 0:9df942ea84f4 | 185 | WriteReg(CCxxx0_FREND1, pRfSettings->FREND1); |

| tmav123 | 0:9df942ea84f4 | 186 | WriteReg(CCxxx0_FREND0, pRfSettings->FREND0); |

| tmav123 | 0:9df942ea84f4 | 187 | WriteReg(CCxxx0_MCSM0 , pRfSettings->MCSM0 ); |

| tmav123 | 0:9df942ea84f4 | 188 | WriteReg(CCxxx0_FOCCFG, pRfSettings->FOCCFG); |

| tmav123 | 0:9df942ea84f4 | 189 | WriteReg(CCxxx0_BSCFG, pRfSettings->BSCFG); |

| tmav123 | 0:9df942ea84f4 | 190 | WriteReg(CCxxx0_AGCCTRL2, pRfSettings->AGCCTRL2); |

| tmav123 | 0:9df942ea84f4 | 191 | WriteReg(CCxxx0_AGCCTRL1, pRfSettings->AGCCTRL1); |

| tmav123 | 0:9df942ea84f4 | 192 | WriteReg(CCxxx0_AGCCTRL0, pRfSettings->AGCCTRL0); |

| tmav123 | 0:9df942ea84f4 | 193 | WriteReg(CCxxx0_FSCAL3, pRfSettings->FSCAL3); |

| tmav123 | 0:9df942ea84f4 | 194 | WriteReg(CCxxx0_FSCAL2, pRfSettings->FSCAL2); |

| tmav123 | 0:9df942ea84f4 | 195 | WriteReg(CCxxx0_FSCAL1, pRfSettings->FSCAL1); |

| tmav123 | 0:9df942ea84f4 | 196 | WriteReg(CCxxx0_FSCAL0, pRfSettings->FSCAL0); |

| tmav123 | 0:9df942ea84f4 | 197 | WriteReg(CCxxx0_FSTEST, pRfSettings->FSTEST); |

| tmav123 | 0:9df942ea84f4 | 198 | WriteReg(CCxxx0_TEST2, pRfSettings->TEST2); |

| tmav123 | 0:9df942ea84f4 | 199 | WriteReg(CCxxx0_TEST1, pRfSettings->TEST1); |

| tmav123 | 0:9df942ea84f4 | 200 | WriteReg(CCxxx0_TEST0, pRfSettings->TEST0); |

| tmav123 | 0:9df942ea84f4 | 201 | WriteReg(CCxxx0_FIFOTHR, pRfSettings->FIFOTHR); |

| tmav123 | 0:9df942ea84f4 | 202 | WriteReg(CCxxx0_IOCFG2, pRfSettings->IOCFG2); |

| tmav123 | 0:9df942ea84f4 | 203 | WriteReg(CCxxx0_IOCFG0, pRfSettings->IOCFG0); |

| tmav123 | 0:9df942ea84f4 | 204 | WriteReg(CCxxx0_PKTCTRL1, pRfSettings->PKTCTRL1); |

| tmav123 | 0:9df942ea84f4 | 205 | WriteReg(CCxxx0_PKTCTRL0, pRfSettings->PKTCTRL0); |

| tmav123 | 0:9df942ea84f4 | 206 | WriteReg(CCxxx0_ADDR, pRfSettings->ADDR); |

| tmav123 | 0:9df942ea84f4 | 207 | WriteReg(CCxxx0_PKTLEN, pRfSettings->PKTLEN); |

| tmav123 | 0:9df942ea84f4 | 208 | WriteReg(CCxxx0_MCSM1 , pRfSettings->MCSM1 ); |

| tmav123 | 0:9df942ea84f4 | 209 | RXMode(); |

| tmav123 | 0:9df942ea84f4 | 210 | |

| tmav123 | 0:9df942ea84f4 | 211 | }// WriteRfSettings |

| tmav123 | 0:9df942ea84f4 | 212 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 213 | void CC1101::init(void) |

| tmav123 | 0:9df942ea84f4 | 214 | { |

| tmav123 | 0:9df942ea84f4 | 215 | WriteRfSettings(&rfSettings); |

| tmav123 | 0:9df942ea84f4 | 216 | WriteReg(CCxxx0_PATABLE, paTable[0]); |

| tmav123 | 0:9df942ea84f4 | 217 | } |

| tmav123 | 0:9df942ea84f4 | 218 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 219 | // unsigned char ReadReg(unsigned char addr) |

| tmav123 | 0:9df942ea84f4 | 220 | // |

| tmav123 | 0:9df942ea84f4 | 221 | // DESCRIPTION: |

| tmav123 | 0:9df942ea84f4 | 222 | // This function gets the value of a single specified CCxxx0 register. |

| tmav123 | 0:9df942ea84f4 | 223 | // |

| tmav123 | 0:9df942ea84f4 | 224 | // ARGUMENTS: |

| tmav123 | 0:9df942ea84f4 | 225 | // unsigned char addr |

| tmav123 | 0:9df942ea84f4 | 226 | // Address of the CCxxx0 register to be accessed. |

| tmav123 | 0:9df942ea84f4 | 227 | // |

| tmav123 | 0:9df942ea84f4 | 228 | // RETURN VALUE: |

| tmav123 | 0:9df942ea84f4 | 229 | // unsigned char |

| tmav123 | 0:9df942ea84f4 | 230 | // Value of the accessed CCxxx0 register. |

| tmav123 | 0:9df942ea84f4 | 231 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 232 | unsigned char CC1101::ReadReg(unsigned char addr) |

| tmav123 | 0:9df942ea84f4 | 233 | { |

| tmav123 | 0:9df942ea84f4 | 234 | unsigned char x; |

| tmav123 | 0:9df942ea84f4 | 235 | wait(0.000005); |

| tmav123 | 0:9df942ea84f4 | 236 | _csn = 0; |

| tmav123 | 0:9df942ea84f4 | 237 | wait(0.000002); |

| tmav123 | 0:9df942ea84f4 | 238 | while (_RDmiso); |

| tmav123 | 0:9df942ea84f4 | 239 | _spi.write(addr | READ_SINGLE); |

| tmav123 | 0:9df942ea84f4 | 240 | x = _spi.write(0); |

| tmav123 | 0:9df942ea84f4 | 241 | wait(0.000002); |

| tmav123 | 0:9df942ea84f4 | 242 | _csn = 1; |

| tmav123 | 0:9df942ea84f4 | 243 | return x; |

| tmav123 | 0:9df942ea84f4 | 244 | }// ReadReg |

| tmav123 | 0:9df942ea84f4 | 245 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 246 | // void ReadBurstReg(unsigned char addr, unsigned char *buffer, unsigned char count) |

| tmav123 | 0:9df942ea84f4 | 247 | // |

| tmav123 | 0:9df942ea84f4 | 248 | // DESCRIPTION: |

| tmav123 | 0:9df942ea84f4 | 249 | // This function reads multiple CCxxx0 register, using SPI burst access. |

| tmav123 | 0:9df942ea84f4 | 250 | // |

| tmav123 | 0:9df942ea84f4 | 251 | // ARGUMENTS: |

| tmav123 | 0:9df942ea84f4 | 252 | // unsigned char addr |

| tmav123 | 0:9df942ea84f4 | 253 | // Address of the first CCxxx0 register to be accessed. |

| tmav123 | 0:9df942ea84f4 | 254 | // unsigned char *buffer |

| tmav123 | 0:9df942ea84f4 | 255 | // Pointer to a byte array which stores the values read from a |

| tmav123 | 0:9df942ea84f4 | 256 | // corresponding range of CCxxx0 registers. |

| tmav123 | 0:9df942ea84f4 | 257 | // unsigned char count |

| tmav123 | 0:9df942ea84f4 | 258 | // Number of bytes to be read from the subsequent CCxxx0 registers. |

| tmav123 | 0:9df942ea84f4 | 259 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 260 | void CC1101::ReadBurstReg(unsigned char addr, unsigned char *buffer, unsigned char count) |

| tmav123 | 0:9df942ea84f4 | 261 | { |

| tmav123 | 0:9df942ea84f4 | 262 | unsigned char i; |

| tmav123 | 0:9df942ea84f4 | 263 | wait(0.000005); |

| tmav123 | 0:9df942ea84f4 | 264 | _csn = 0; |

| tmav123 | 0:9df942ea84f4 | 265 | wait(0.000002); |

| tmav123 | 0:9df942ea84f4 | 266 | while (_RDmiso); |

| tmav123 | 0:9df942ea84f4 | 267 | _spi.write(addr | READ_BURST); |

| hillkim7 | 1:e96096a7b90b | 268 | for (i = 0; i < count; i++) { |

| tmav123 | 0:9df942ea84f4 | 269 | buffer[i] = _spi.write(0); |

| tmav123 | 0:9df942ea84f4 | 270 | } |

| tmav123 | 0:9df942ea84f4 | 271 | wait(0.000002); |

| tmav123 | 0:9df942ea84f4 | 272 | _csn = 1; |

| tmav123 | 0:9df942ea84f4 | 273 | }// ReadBurstReg |

| tmav123 | 0:9df942ea84f4 | 274 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 275 | // void WriteReg(unsigned char addr, unsigned char value) |

| tmav123 | 0:9df942ea84f4 | 276 | // |

| tmav123 | 0:9df942ea84f4 | 277 | // DESCRIPTION: |

| tmav123 | 0:9df942ea84f4 | 278 | // Function for writing to a single CCxxx0 register |

| tmav123 | 0:9df942ea84f4 | 279 | // |

| tmav123 | 0:9df942ea84f4 | 280 | // ARGUMENTS: |

| tmav123 | 0:9df942ea84f4 | 281 | // unsigned char addr |

| tmav123 | 0:9df942ea84f4 | 282 | // Address of a specific CCxxx0 register to accessed. |

| tmav123 | 0:9df942ea84f4 | 283 | // unsigned char value |

| tmav123 | 0:9df942ea84f4 | 284 | // Value to be written to the specified CCxxx0 register. |

| tmav123 | 0:9df942ea84f4 | 285 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 286 | void CC1101::WriteReg(unsigned char addr, unsigned char value) |

| tmav123 | 0:9df942ea84f4 | 287 | { |

| tmav123 | 0:9df942ea84f4 | 288 | wait(0.000005); |

| tmav123 | 0:9df942ea84f4 | 289 | _csn = 0; |

| tmav123 | 0:9df942ea84f4 | 290 | wait(0.000002); |

| tmav123 | 0:9df942ea84f4 | 291 | while (_RDmiso); |

| tmav123 | 0:9df942ea84f4 | 292 | _spi.write(addr); |

| tmav123 | 0:9df942ea84f4 | 293 | _spi.write(value); |

| tmav123 | 0:9df942ea84f4 | 294 | wait(0.000002); |

| tmav123 | 0:9df942ea84f4 | 295 | _csn = 1; |

| tmav123 | 0:9df942ea84f4 | 296 | }// WriteReg |

| tmav123 | 0:9df942ea84f4 | 297 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 298 | // void WriteBurstReg(unsigned char addr, unsigned char *buffer, unsigned char count) |

| tmav123 | 0:9df942ea84f4 | 299 | // |

| tmav123 | 0:9df942ea84f4 | 300 | // DESCRIPTION: |

| tmav123 | 0:9df942ea84f4 | 301 | // This function writes to multiple CCxxx0 register, using SPI burst access. |

| tmav123 | 0:9df942ea84f4 | 302 | // |

| tmav123 | 0:9df942ea84f4 | 303 | // ARGUMENTS: |

| tmav123 | 0:9df942ea84f4 | 304 | // unsigned char addr |

| tmav123 | 0:9df942ea84f4 | 305 | // Address of the first CCxxx0 register to be accessed. |

| tmav123 | 0:9df942ea84f4 | 306 | // unsigned char *buffer |

| tmav123 | 0:9df942ea84f4 | 307 | // Array of bytes to be written into a corresponding range of |

| tmav123 | 0:9df942ea84f4 | 308 | // CCxx00 registers, starting by the address specified in _addr_. |

| tmav123 | 0:9df942ea84f4 | 309 | // unsigned char count |

| tmav123 | 0:9df942ea84f4 | 310 | // Number of bytes to be written to the subsequent CCxxx0 registers. |

| tmav123 | 0:9df942ea84f4 | 311 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 312 | void CC1101::WriteBurstReg(unsigned char addr, unsigned char *buffer, unsigned char count) |

| tmav123 | 0:9df942ea84f4 | 313 | { |

| tmav123 | 0:9df942ea84f4 | 314 | unsigned char i; |

| tmav123 | 0:9df942ea84f4 | 315 | wait(0.000005); |

| tmav123 | 0:9df942ea84f4 | 316 | _csn = 0; |

| tmav123 | 0:9df942ea84f4 | 317 | wait(0.000002); |

| tmav123 | 0:9df942ea84f4 | 318 | while (_RDmiso); |

| tmav123 | 0:9df942ea84f4 | 319 | _spi.write(addr | WRITE_BURST); |

| hillkim7 | 1:e96096a7b90b | 320 | for (i = 0; i < count; i++) { |

| tmav123 | 0:9df942ea84f4 | 321 | _spi.write(buffer[i]); |

| tmav123 | 0:9df942ea84f4 | 322 | } |

| tmav123 | 0:9df942ea84f4 | 323 | wait(0.000002); |

| tmav123 | 0:9df942ea84f4 | 324 | _csn = 1; |

| tmav123 | 0:9df942ea84f4 | 325 | }// WriteBurstReg |

| tmav123 | 0:9df942ea84f4 | 326 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 327 | unsigned char CC1101::RdRSSI(void) |

| tmav123 | 0:9df942ea84f4 | 328 | { |

| tmav123 | 0:9df942ea84f4 | 329 | unsigned char crssi; |

| hillkim7 | 1:e96096a7b90b | 330 | |

| hillkim7 | 1:e96096a7b90b | 331 | |

| hillkim7 | 1:e96096a7b90b | 332 | if (rssi >= 128) { |

| tmav123 | 0:9df942ea84f4 | 333 | crssi = 255 - rssi; |

| tmav123 | 0:9df942ea84f4 | 334 | crssi /= 2; |

| tmav123 | 0:9df942ea84f4 | 335 | crssi += 74; |

| hillkim7 | 1:e96096a7b90b | 336 | } else { |

| tmav123 | 0:9df942ea84f4 | 337 | crssi = rssi/2; |

| tmav123 | 0:9df942ea84f4 | 338 | crssi += 74; |

| tmav123 | 0:9df942ea84f4 | 339 | } |

| tmav123 | 0:9df942ea84f4 | 340 | return crssi; |

| tmav123 | 0:9df942ea84f4 | 341 | } |

| tmav123 | 0:9df942ea84f4 | 342 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 343 | unsigned char CC1101::RdLQI(void) |

| tmav123 | 0:9df942ea84f4 | 344 | { |

| tmav123 | 0:9df942ea84f4 | 345 | unsigned char clqi; |

| tmav123 | 0:9df942ea84f4 | 346 | clqi = 0x3F - (lqi & 0x3F); |

| hillkim7 | 1:e96096a7b90b | 347 | |

| tmav123 | 0:9df942ea84f4 | 348 | return clqi; |

| tmav123 | 0:9df942ea84f4 | 349 | } |

| tmav123 | 0:9df942ea84f4 | 350 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 351 | unsigned char CC1101::RxFifoEmpty(void) |

| tmav123 | 0:9df942ea84f4 | 352 | { |

| tmav123 | 0:9df942ea84f4 | 353 | unsigned char RxFifoStatus; |

| tmav123 | 0:9df942ea84f4 | 354 | |

| tmav123 | 0:9df942ea84f4 | 355 | Strobe(CCxxx0_SRX); |

| tmav123 | 0:9df942ea84f4 | 356 | RxFifoStatus = ReadStatus(CCxxx0_RXBYTES); |

| hillkim7 | 1:e96096a7b90b | 357 | |

| hillkim7 | 1:e96096a7b90b | 358 | if (RxFifoStatus & 0x80) { // check for RXFIFO overflow |

| tmav123 | 0:9df942ea84f4 | 359 | // Make sure that the radio is in IDLE state before flushing the FIFO |

| tmav123 | 0:9df942ea84f4 | 360 | // (Unless RXOFF_MODE has been changed, the radio should be in IDLE state at this point) |

| tmav123 | 0:9df942ea84f4 | 361 | Strobe(CCxxx0_SIDLE); |

| tmav123 | 0:9df942ea84f4 | 362 | |

| tmav123 | 0:9df942ea84f4 | 363 | // Flush RX FIFO |

| tmav123 | 0:9df942ea84f4 | 364 | Strobe(CCxxx0_SFRX); |

| tmav123 | 0:9df942ea84f4 | 365 | } |

| hillkim7 | 1:e96096a7b90b | 366 | if (RxFifoStatus & ~0x80) { |

| tmav123 | 0:9df942ea84f4 | 367 | return 0; |

| hillkim7 | 1:e96096a7b90b | 368 | } else |

| tmav123 | 0:9df942ea84f4 | 369 | return 1; |

| tmav123 | 0:9df942ea84f4 | 370 | } |

| tmav123 | 0:9df942ea84f4 | 371 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 372 | //------------------------------------------------------------------------------------------------------- |

| tmav123 | 0:9df942ea84f4 | 373 | // BOOL ReceivePacket(unsigned char *rxBuffer, unsigned char *length) |

| tmav123 | 0:9df942ea84f4 | 374 | // |

| tmav123 | 0:9df942ea84f4 | 375 | // DESCRIPTION: |

| tmav123 | 0:9df942ea84f4 | 376 | // This function can be used to receive a packet of variable packet length (first byte in the packet |

| tmav123 | 0:9df942ea84f4 | 377 | // must be the length byte). The packet length should not exceed the RX FIFO size. |

| tmav123 | 0:9df942ea84f4 | 378 | // |

| tmav123 | 0:9df942ea84f4 | 379 | // ARGUMENTS: |

| tmav123 | 0:9df942ea84f4 | 380 | // unsigned char *rxBuffer |

| tmav123 | 0:9df942ea84f4 | 381 | // Pointer to the buffer where the incoming data should be stored |

| tmav123 | 0:9df942ea84f4 | 382 | // unsigned char *length |

| tmav123 | 0:9df942ea84f4 | 383 | // Pointer to a variable containing the size of the buffer where the incoming data should be |

| tmav123 | 0:9df942ea84f4 | 384 | // stored. After this function returns, that variable holds the packet length. |

| tmav123 | 0:9df942ea84f4 | 385 | // |

| tmav123 | 0:9df942ea84f4 | 386 | // RETURN VALUE: |

| tmav123 | 0:9df942ea84f4 | 387 | // BOOL |

| tmav123 | 0:9df942ea84f4 | 388 | // 1: CRC OK |

| tmav123 | 0:9df942ea84f4 | 389 | // 0: CRC NOT OK (or no packet was put in the RX FIFO due to filtering) |

| tmav123 | 0:9df942ea84f4 | 390 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 391 | |

| tmav123 | 0:9df942ea84f4 | 392 | int CC1101::ReceivePacket(unsigned char *rxBuffer, unsigned char *length) |

| tmav123 | 0:9df942ea84f4 | 393 | { |

| hillkim7 | 1:e96096a7b90b | 394 | unsigned char status[2]; |

| hillkim7 | 1:e96096a7b90b | 395 | unsigned char packetLength, bytes; |

| tmav123 | 0:9df942ea84f4 | 396 | |

| hillkim7 | 1:e96096a7b90b | 397 | bytes = packetLength = ReadStatus(CCxxx0_RXBYTES); |

| hillkim7 | 1:e96096a7b90b | 398 | if (packetLength & BYTES_IN_RXFIFO) { |

| tmav123 | 0:9df942ea84f4 | 399 | // Read length byte |

| tmav123 | 0:9df942ea84f4 | 400 | packetLength = ReadReg(CCxxx0_RXFIFO); |

| tmav123 | 0:9df942ea84f4 | 401 | |

| tmav123 | 0:9df942ea84f4 | 402 | // Read data from RX FIFO and store in rxBuffer |

| hillkim7 | 1:e96096a7b90b | 403 | if (packetLength <= *length) { |

| tmav123 | 0:9df942ea84f4 | 404 | ReadBurstReg(CCxxx0_RXFIFO, rxBuffer, packetLength); |

| tmav123 | 0:9df942ea84f4 | 405 | *length = packetLength; |

| hillkim7 | 1:e96096a7b90b | 406 | |

| tmav123 | 0:9df942ea84f4 | 407 | // Read the 2 appended status bytes (status[0] = RSSI, status[1] = LQI) |

| tmav123 | 0:9df942ea84f4 | 408 | ReadBurstReg(CCxxx0_RXFIFO, status, 2); |

| tmav123 | 0:9df942ea84f4 | 409 | |

| tmav123 | 0:9df942ea84f4 | 410 | rssi = status[RSSI]; |

| tmav123 | 0:9df942ea84f4 | 411 | lqi = status[LQI]; |

| tmav123 | 0:9df942ea84f4 | 412 | // MSB of LQI is the CRC_OK bit |

| tmav123 | 0:9df942ea84f4 | 413 | // return (status[LQI] & CRC_OK); |

| hillkim7 | 1:e96096a7b90b | 414 | if(status[LQI] & CRC_OK) { |

| hillkim7 | 1:e96096a7b90b | 415 | return 1; |

| tmav123 | 0:9df942ea84f4 | 416 | } |

| hillkim7 | 1:e96096a7b90b | 417 | } else { |

| hillkim7 | 1:e96096a7b90b | 418 | printf("too big packet length=%u/%u RXBYTES=%u\r\n", packetLength, *length, bytes); |

| tmav123 | 0:9df942ea84f4 | 419 | *length = packetLength; |

| tmav123 | 0:9df942ea84f4 | 420 | |

| tmav123 | 0:9df942ea84f4 | 421 | // Make sure that the radio is in IDLE state before flushing the FIFO |

| tmav123 | 0:9df942ea84f4 | 422 | // (Unless RXOFF_MODE has been changed, the radio should be in IDLE state at this point) |

| tmav123 | 0:9df942ea84f4 | 423 | Strobe(CCxxx0_SIDLE); |

| tmav123 | 0:9df942ea84f4 | 424 | |

| tmav123 | 0:9df942ea84f4 | 425 | // Flush RX FIFO |

| tmav123 | 0:9df942ea84f4 | 426 | Strobe(CCxxx0_SFRX); |

| tmav123 | 0:9df942ea84f4 | 427 | return 0; |

| tmav123 | 0:9df942ea84f4 | 428 | } |

| tmav123 | 0:9df942ea84f4 | 429 | } else |

| tmav123 | 0:9df942ea84f4 | 430 | return 0; |

| hillkim7 | 1:e96096a7b90b | 431 | return 0; |

| tmav123 | 0:9df942ea84f4 | 432 | }// halRfReceivePacket |

| tmav123 | 0:9df942ea84f4 | 433 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 434 | unsigned char CC1101::TxFifoEmpty(void) |

| tmav123 | 0:9df942ea84f4 | 435 | { |

| tmav123 | 0:9df942ea84f4 | 436 | unsigned char TxFifoStatus; |

| tmav123 | 0:9df942ea84f4 | 437 | |

| tmav123 | 0:9df942ea84f4 | 438 | Strobe(CCxxx0_STX); |

| tmav123 | 0:9df942ea84f4 | 439 | TxFifoStatus = ReadStatus(CCxxx0_TXBYTES); |

| hillkim7 | 1:e96096a7b90b | 440 | |

| hillkim7 | 1:e96096a7b90b | 441 | if (TxFifoStatus & 0x80) { // check for TXFIFO underflow |

| tmav123 | 0:9df942ea84f4 | 442 | // Make sure that the radio is in IDLE state before flushing the FIFO |

| hillkim7 | 1:e96096a7b90b | 443 | Strobe(CCxxx0_SIDLE); |

| tmav123 | 0:9df942ea84f4 | 444 | |

| tmav123 | 0:9df942ea84f4 | 445 | // Flush TX FIFO |

| tmav123 | 0:9df942ea84f4 | 446 | Strobe(CCxxx0_SFTX); |

| tmav123 | 0:9df942ea84f4 | 447 | } |

| hillkim7 | 1:e96096a7b90b | 448 | if (TxFifoStatus & ~0x80) { |

| tmav123 | 0:9df942ea84f4 | 449 | return 0; |

| hillkim7 | 1:e96096a7b90b | 450 | } else |

| tmav123 | 0:9df942ea84f4 | 451 | return 1; |

| tmav123 | 0:9df942ea84f4 | 452 | } |

| tmav123 | 0:9df942ea84f4 | 453 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 454 | // void halRfSendPacket(unsigned char *txBuffer, unsigned char size) |

| tmav123 | 0:9df942ea84f4 | 455 | // |

| tmav123 | 0:9df942ea84f4 | 456 | // DESCRIPTION: |

| tmav123 | 0:9df942ea84f4 | 457 | // This function can be used to transmit a packet with packet length up to 63 bytes. |

| tmav123 | 0:9df942ea84f4 | 458 | // |

| tmav123 | 0:9df942ea84f4 | 459 | // ARGUMENTS: |

| tmav123 | 0:9df942ea84f4 | 460 | // unsigned char *txBuffer |

| tmav123 | 0:9df942ea84f4 | 461 | // Pointer to a buffer containing the data that are going to be transmitted |

| tmav123 | 0:9df942ea84f4 | 462 | // |

| tmav123 | 0:9df942ea84f4 | 463 | // unsigned char size |

| tmav123 | 0:9df942ea84f4 | 464 | // The size of the txBuffer |

| tmav123 | 0:9df942ea84f4 | 465 | /////////////////////////////////////////////////////////////////////////////////////// |

| hillkim7 | 1:e96096a7b90b | 466 | void CC1101::SendPacket(const unsigned char *txBuffer, unsigned char size) |

| tmav123 | 0:9df942ea84f4 | 467 | { |

| tmav123 | 0:9df942ea84f4 | 468 | unsigned char i; |

| hillkim7 | 1:e96096a7b90b | 469 | unsigned char buf[64]; |

| tmav123 | 0:9df942ea84f4 | 470 | |

| hillkim7 | 1:e96096a7b90b | 471 | buf[0] = size; |

| hillkim7 | 1:e96096a7b90b | 472 | for (i = 0; i < size; i++) |

| hillkim7 | 1:e96096a7b90b | 473 | buf[i+1] = txBuffer[i]; |

| tmav123 | 0:9df942ea84f4 | 474 | |

| hillkim7 | 1:e96096a7b90b | 475 | WriteBurstReg(CCxxx0_TXFIFO, buf, size+1); |

| tmav123 | 0:9df942ea84f4 | 476 | Strobe(CCxxx0_SIDLE); |

| tmav123 | 0:9df942ea84f4 | 477 | Strobe(CCxxx0_STX); |

| hillkim7 | 1:e96096a7b90b | 478 | |

| hillkim7 | 1:e96096a7b90b | 479 | ////////////////////////////////////////////////////////////////////////////////////////////// |

| hillkim7 | 1:e96096a7b90b | 480 | // To send subsequent packet we should ensure packet is sent before return this function |

| hillkim7 | 1:e96096a7b90b | 481 | ////////////////////////////////////////////////////////////////////////////////////////////// |

| hillkim7 | 1:e96096a7b90b | 482 | // Following check routine is valid when IOCFG2=0x06 is set. |

| hillkim7 | 1:e96096a7b90b | 483 | unsigned t; |

| hillkim7 | 1:e96096a7b90b | 484 | const unsigned safe_check_count = 1000000; |

| hillkim7 | 1:e96096a7b90b | 485 | |

| hillkim7 | 1:e96096a7b90b | 486 | t = 0; |

| hillkim7 | 2:54c832c68208 | 487 | // Wait for GDO2 to be set -> sync transmitted |

| hillkim7 | 2:54c832c68208 | 488 | while (!_gdo2 && t++ < safe_check_count); |

| hillkim7 | 1:e96096a7b90b | 489 | if (t == safe_check_count) { |

| hillkim7 | 1:e96096a7b90b | 490 | printf("check timeout 1\r\n"); |

| hillkim7 | 1:e96096a7b90b | 491 | } |

| hillkim7 | 1:e96096a7b90b | 492 | |

| hillkim7 | 2:54c832c68208 | 493 | // Wait for GDO2 to be cleared -> end of packet |

| hillkim7 | 1:e96096a7b90b | 494 | t = 0; |

| hillkim7 | 2:54c832c68208 | 495 | while (_gdo2 && t++ < safe_check_count); |

| hillkim7 | 1:e96096a7b90b | 496 | |

| hillkim7 | 1:e96096a7b90b | 497 | if (t == safe_check_count) { |

| hillkim7 | 1:e96096a7b90b | 498 | printf("check timeout 2\r\n"); |

| hillkim7 | 1:e96096a7b90b | 499 | } |

| hillkim7 | 1:e96096a7b90b | 500 | |

| tmav123 | 0:9df942ea84f4 | 501 | }// halRfSendPacket |

| hillkim7 | 1:e96096a7b90b | 502 | |

| tmav123 | 0:9df942ea84f4 | 503 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 504 | unsigned char CC1101::ReadChipStatusTX(void) |

| tmav123 | 0:9df942ea84f4 | 505 | { |

| tmav123 | 0:9df942ea84f4 | 506 | unsigned char x; |

| tmav123 | 0:9df942ea84f4 | 507 | |

| tmav123 | 0:9df942ea84f4 | 508 | x = Strobe(CCxxx0_SNOP); |

| tmav123 | 0:9df942ea84f4 | 509 | return x; |

| tmav123 | 0:9df942ea84f4 | 510 | } |

| tmav123 | 0:9df942ea84f4 | 511 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 512 | unsigned char CC1101::ReadChipStatusRX(void) |

| tmav123 | 0:9df942ea84f4 | 513 | { |

| tmav123 | 0:9df942ea84f4 | 514 | unsigned char x; |

| tmav123 | 0:9df942ea84f4 | 515 | wait(0.000005); |

| tmav123 | 0:9df942ea84f4 | 516 | _csn = 0; |

| tmav123 | 0:9df942ea84f4 | 517 | wait(0.000002); |

| tmav123 | 0:9df942ea84f4 | 518 | while (_RDmiso); |

| tmav123 | 0:9df942ea84f4 | 519 | x = _spi.write(CCxxx0_PARTNUM | READ_BURST); |

| tmav123 | 0:9df942ea84f4 | 520 | wait(0.000002); |

| tmav123 | 0:9df942ea84f4 | 521 | _csn = 1; |

| tmav123 | 0:9df942ea84f4 | 522 | return x; |

| tmav123 | 0:9df942ea84f4 | 523 | } |

| tmav123 | 0:9df942ea84f4 | 524 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 525 | void CC1101::FlushRX(void) |

| tmav123 | 0:9df942ea84f4 | 526 | { |

| tmav123 | 0:9df942ea84f4 | 527 | // Make sure that the radio is in IDLE state before flushing the FIFO |

| tmav123 | 0:9df942ea84f4 | 528 | Strobe(CCxxx0_SIDLE); |

| tmav123 | 0:9df942ea84f4 | 529 | |

| tmav123 | 0:9df942ea84f4 | 530 | // Flush RX FIFO |

| tmav123 | 0:9df942ea84f4 | 531 | Strobe(CCxxx0_SFRX); |

| tmav123 | 0:9df942ea84f4 | 532 | } |

| tmav123 | 0:9df942ea84f4 | 533 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 534 | void CC1101::FlushTX(void) |

| tmav123 | 0:9df942ea84f4 | 535 | { |

| tmav123 | 0:9df942ea84f4 | 536 | // Make sure that the radio is in IDLE state before flushing the FIFO |

| tmav123 | 0:9df942ea84f4 | 537 | Strobe(CCxxx0_SIDLE); |

| tmav123 | 0:9df942ea84f4 | 538 | |

| tmav123 | 0:9df942ea84f4 | 539 | // Flush TX FIFO |

| tmav123 | 0:9df942ea84f4 | 540 | Strobe(CCxxx0_SFTX); |

| tmav123 | 0:9df942ea84f4 | 541 | } |

| tmav123 | 0:9df942ea84f4 | 542 | /////////////////////////////////////////////////////////////////////////////////////// |

| tmav123 | 0:9df942ea84f4 | 543 | void CC1101::RXMode(void) |

| tmav123 | 0:9df942ea84f4 | 544 | { |

| tmav123 | 0:9df942ea84f4 | 545 | Strobe(CCxxx0_SIDLE); |

| tmav123 | 0:9df942ea84f4 | 546 | Strobe(CCxxx0_SRX); |

| tmav123 | 0:9df942ea84f4 | 547 | } |

| tmav123 | 0:9df942ea84f4 | 548 | /////////////////////////////////////////////////////////////////////////////////////// |

| hillkim7 | 1:e96096a7b90b | 549 | int CC1101::GetGDO0(void) |

| hillkim7 | 1:e96096a7b90b | 550 | { |

| hillkim7 | 1:e96096a7b90b | 551 | return _gdo0; |

| hillkim7 | 1:e96096a7b90b | 552 | } |

| hillkim7 | 1:e96096a7b90b | 553 | /////////////////////////////////////////////////////////////////////////////////////// |

| hillkim7 | 2:54c832c68208 | 554 | int CC1101::GetGDO2(void) |

| hillkim7 | 1:e96096a7b90b | 555 | { |

| hillkim7 | 2:54c832c68208 | 556 | return _gdo2; |

| hillkim7 | 1:e96096a7b90b | 557 | } |

| hillkim7 | 1:e96096a7b90b | 558 | /////////////////////////////////////////////////////////////////////////////////////// |

| hillkim7 | 1:e96096a7b90b | 559 | |

| hillkim7 | 1:e96096a7b90b | 560 |