Important changes to forums and questions

All forums and questions are now archived. To start a new conversation or read the latest updates go to forums.mbed.com.

6 years, 9 months ago.

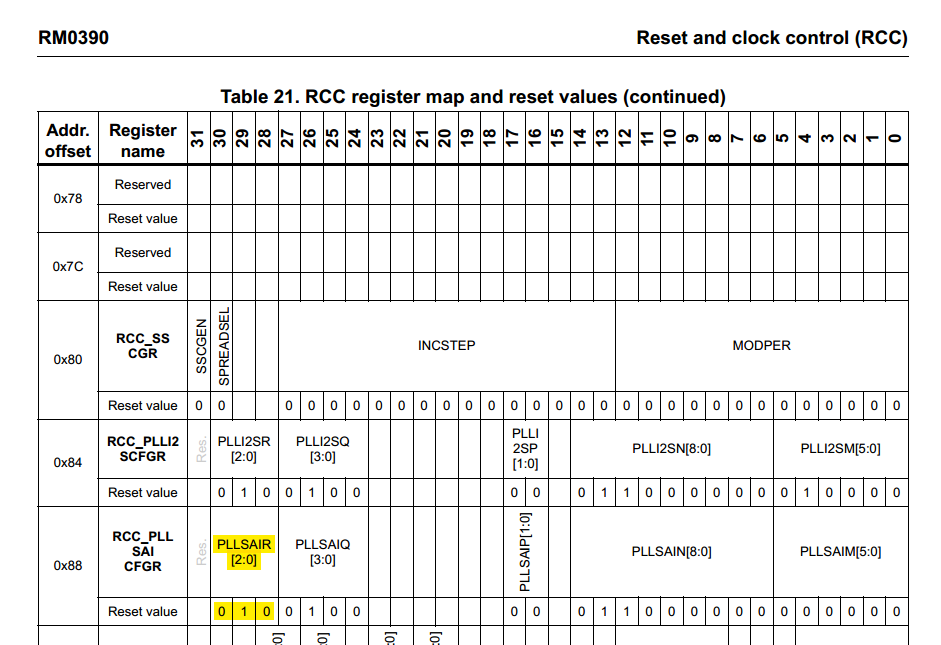

Reset and clock control (RCC) register 0x40023888, the division factor for SAI clock.

At link: https://os.mbed.com/users/mbed_official/code/mbed/file/ba1f97679dad/TARGET_MTS_DRAGONFLY_F411RE/stm32f4xx_hal_rcc_ex.h/ in code, line 223-225 read as uint32_t PLLSAIR; /*!< specifies the division factor for LTDC clock This parameter must be a number between Min_Data = 2 and Max_Data = 7. This parameter will be used only when PLLSAI is selected as Clock Source LTDC */

Reading RCC address 0x40023888 of virgin NUCLEO-F446RE board result value is 0x04003010 0b00000100000000000011000000010000 that is not at reset value for PLLSAIR, but is unadmitted zero value for division factor. In RM0390 Reference manual STM32F446xx advanced Arm®-based 32-bit MCUs, revision 4, page 166 Bits 31:28 are descripted as reserved:is that an error?

In table at page 175 of same document is indicated PLLSAIR reset value correctly.

For that implemented ARM® Cortex® M4 architecture, what is the correct and verbose description for configuration (data meaning, as for similar PLLI2SR[2:0]: PLLI2S division factor for I2S clocks at page 164, that contain caution note)?