NUCLEO-WB15CC

Affordable and flexible platform to ease prototyping using a STM32WB15CC microcontroller.

Overview¶

The NUCLEO-WB15CC STM32WB Nucleo-64 boards are Bluetooth® Low Energy (BLE) wireless and ultra-low-power devices embedding a powerful and ultra-low-power radio compliant with the Bluetooth® Low Energy (BLE) SIG specification v5.2.

Microcontroller features¶

https://www.st.com/en/microcontrollers-microprocessors/stm32wb15cc.html

- Includes ST state-of-the-art patented technology

- Radio

- 2.4 GHz

- RF transceiver supporting Bluetooth® 5.2 specification

- RX sensitivity: -95.5 dBm (Bluetooth® Low Energy at 1 Mbps)

- Programmable output power up to +5.5 dBm with 1 dB steps

- Integrated balun to reduce BOM

- Support for 2 Mbps

- Dedicated Arm® 32-bit Cortex® M0+ CPU for real-time Radio layer

- Accurate RSSI to enable power control

- Suitable for systems requiring compliance with radio frequency regulations ETSI EN 300 328, EN 300 440, FCC CFR47 Part 15 and ARIB STD-T66

- Support for external PA

- Available integrated passive device (IPD) companion chip for optimized matching solution (MLPF-WB-01E3)

- Ultra-low-power platform

- 1.71 to 3.6 V power supply

- – 40 °C to 85 / 105 °C temperature ranges

- 12 nA shutdown mode

- 610 nA Standby mode + RTC + 48 KB RAM

- Active-mode MCU: 33 µA / MHz when RF and SMPS on

- Radio: Rx 4.5 mA / Tx at 0 dBm 5.2 mA

- Core: Arm® 32-bit Cortex®-M4 CPU with FPU, adaptive real-time accelerator (ART Accelerator) allowing 0-wait-state execution from Flash memory, frequency up to 64 MHz, MPU, 80 DMIPS and DSP instructions

- Performance benchmark

- 1.25 DMIPS/MHz (Drystone 2.1)

- Supply and reset management

- High efficiency embedded SMPS step-down converter with intelligent bypass mode

- Ultra-safe, low-power BOR (brownout reset) with five selectable thresholds

- Ultra-low-power POR/PDR

- Programmable voltage detector (PVD)

- VBAT mode with RTC and backup registers

- Clock sources

- 32 MHz crystal oscillator with integrated trimming capacitors (Radio and CPU clock)

- 32 kHz crystal oscillator for RTC (LSE)

- Internal low-power 32 kHz RC (LSI1)

- Internal low-drift 32 kHz RC (LSI2)

- Internal multispeed 100 kHz to 48 MHz oscillator, factory-trimmed

- High speed internal 16 MHz factory trimmed RC

- 1x PLL for system clock and ADC

- Memories

- 320 KB Flash memory with sector protection (PCROP) against R/W operations, enabling radio stack and application

- 48 KB SRAM, including 36 KB with hardware parity check

- 20x32-bit backup register

- Boot loader supporting USART, SPI, I2C interfaces

- 1 Kbyte (128 double words) OTP

- Rich analog peripherals (down to 1.62 V)

- 12-bit ADC 2.5 Msps, 190 µA/Msps

- 1x ultra-low-power comparator

- System peripherals

- Inter processor communication controller (IPCC) for communication with Bluetooth® Low Energy

- HW semaphores for resources sharing between CPUs

- 1x DMA controller (7x channels) supporting ADC, SPI, I2C, USART, AES, timers

- 1x USART (ISO 7816, IrDA, SPI Master, Modbus and Smartcard mode)

- 1x LPUART (low power)

- 1x SPI 32 Mbit/s

- 1x I2C (SMBus/PMBus)

- Touch sensing controller, up to eight sensors

- 1x 16-bit, four channels advanced timer

- 1x 32-bit, four channels timer

- 2x 16-bit ultra-low-power timer

- 1x independent Systick

- 1x independent watchdog

- 1x window watchdog

- Security and ID

- Secure firmware installation (SFI) for Bluetooth® Low Energy SW stack

- 2x hardware encryption AES maximum 256-bit for the application and the Bluetooth® Low Energy

- HW public key authority (PKA)

- Cryptographic algorithms: RSA, Diffie-Helman, ECC over GF(p)

- True random number generator (RNG)

- Sector protection against R/W operation (PCROP)

- CRC calculation unit

- Die information: 96-bit unique ID

- IEEE 64-bit unique ID. Possibility to derive Bluetooth® Low Energy 48-bit EUI

- Up to 37 fast I/Os, 35 of them 5 V-tolerant

Nucleo features¶

Nucleo pinout¶

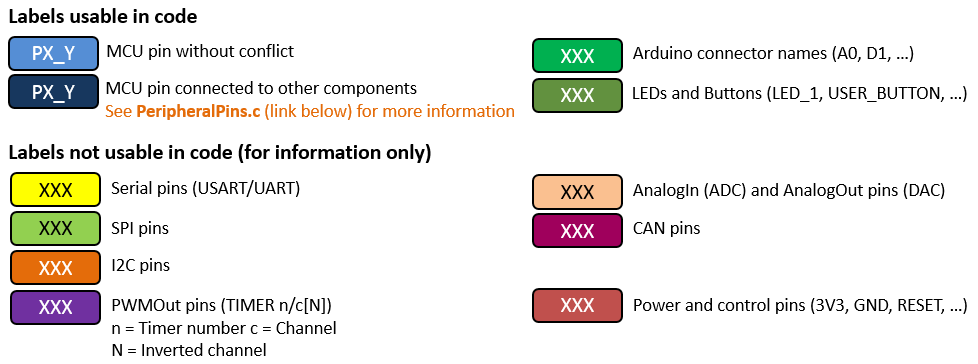

Pins Legend¶

You can find more details on the available pins and labels in the PeripheralPins.c and PinNames.h files.

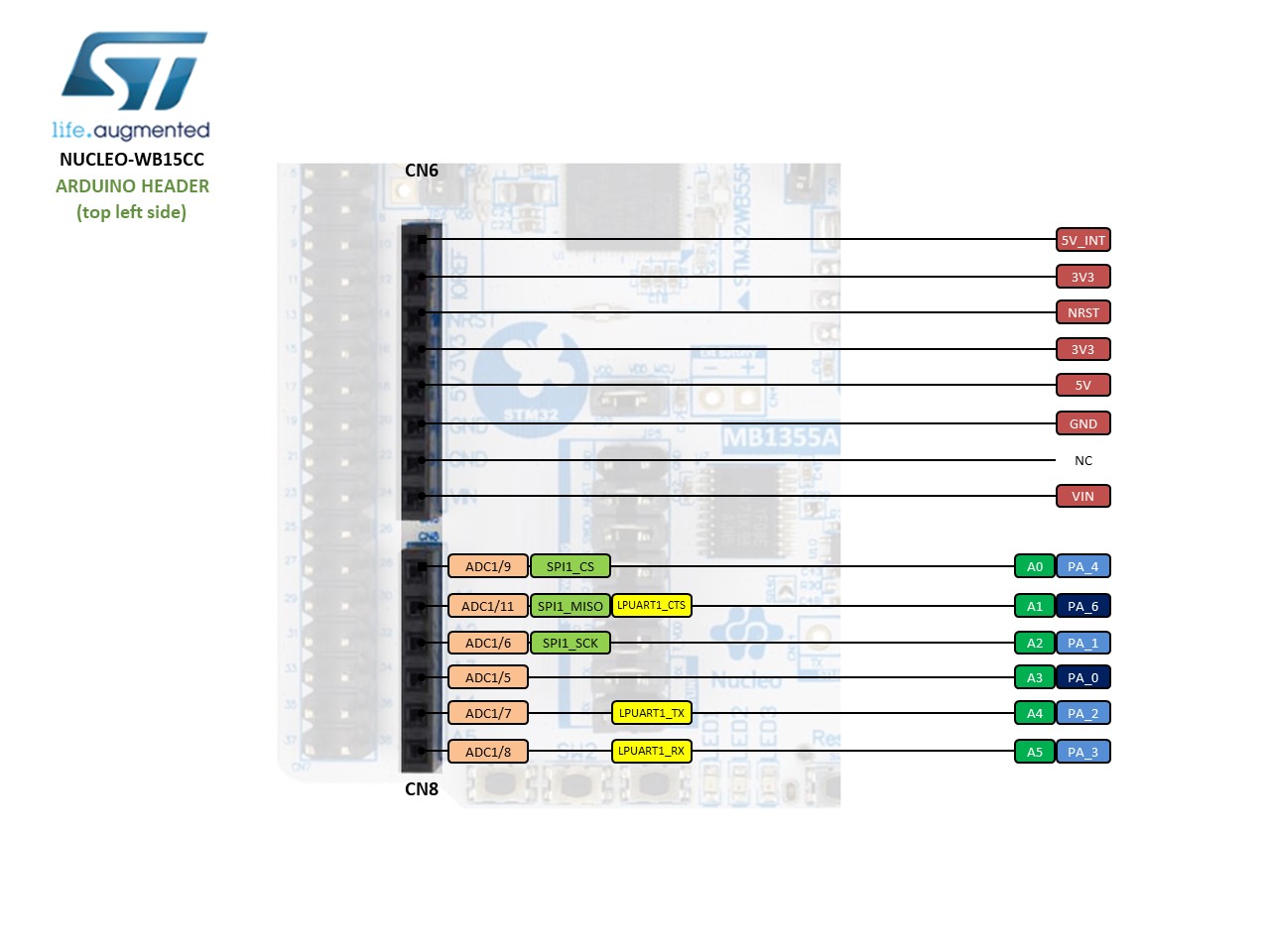

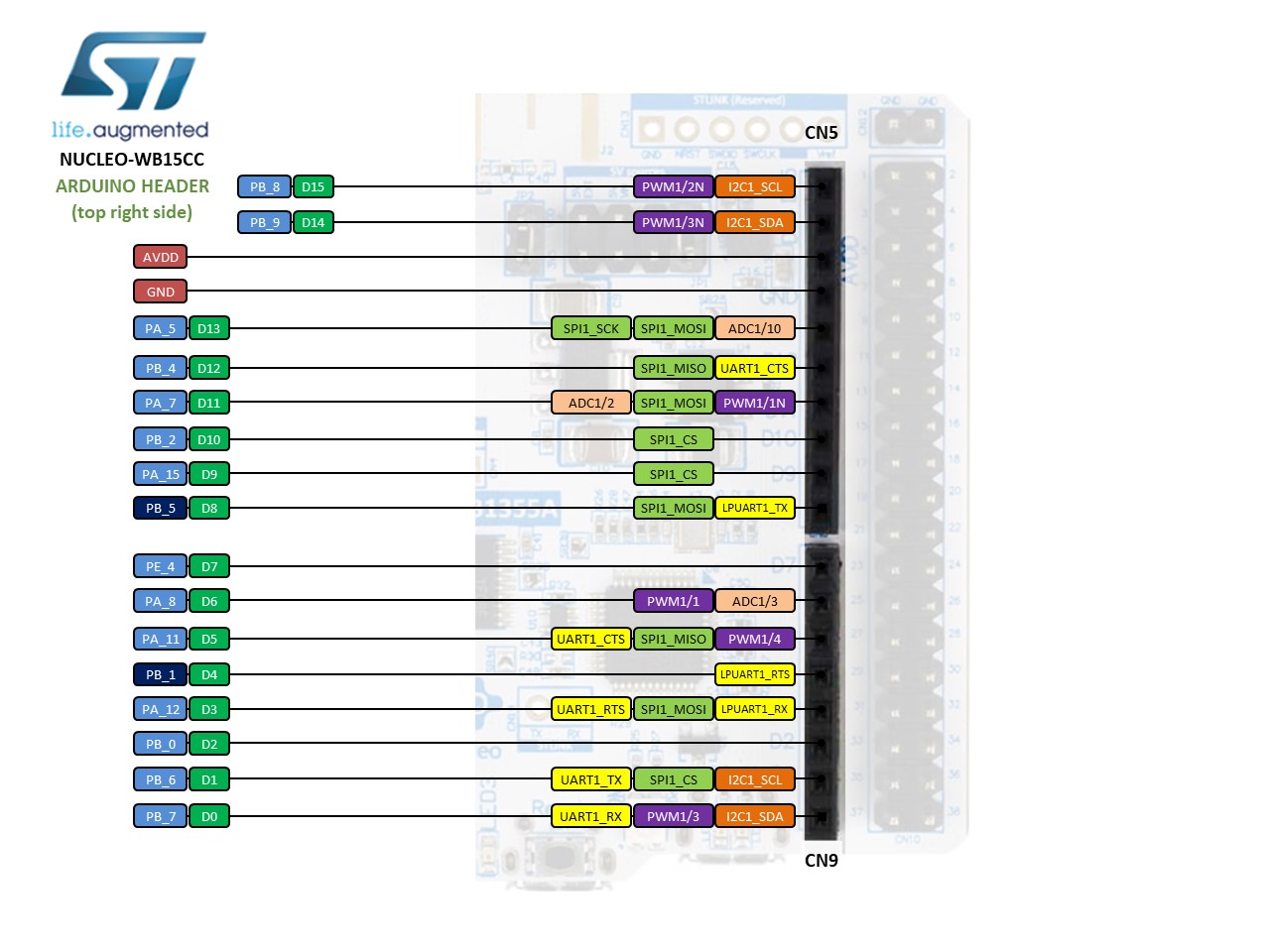

Arduino-compatible headers¶

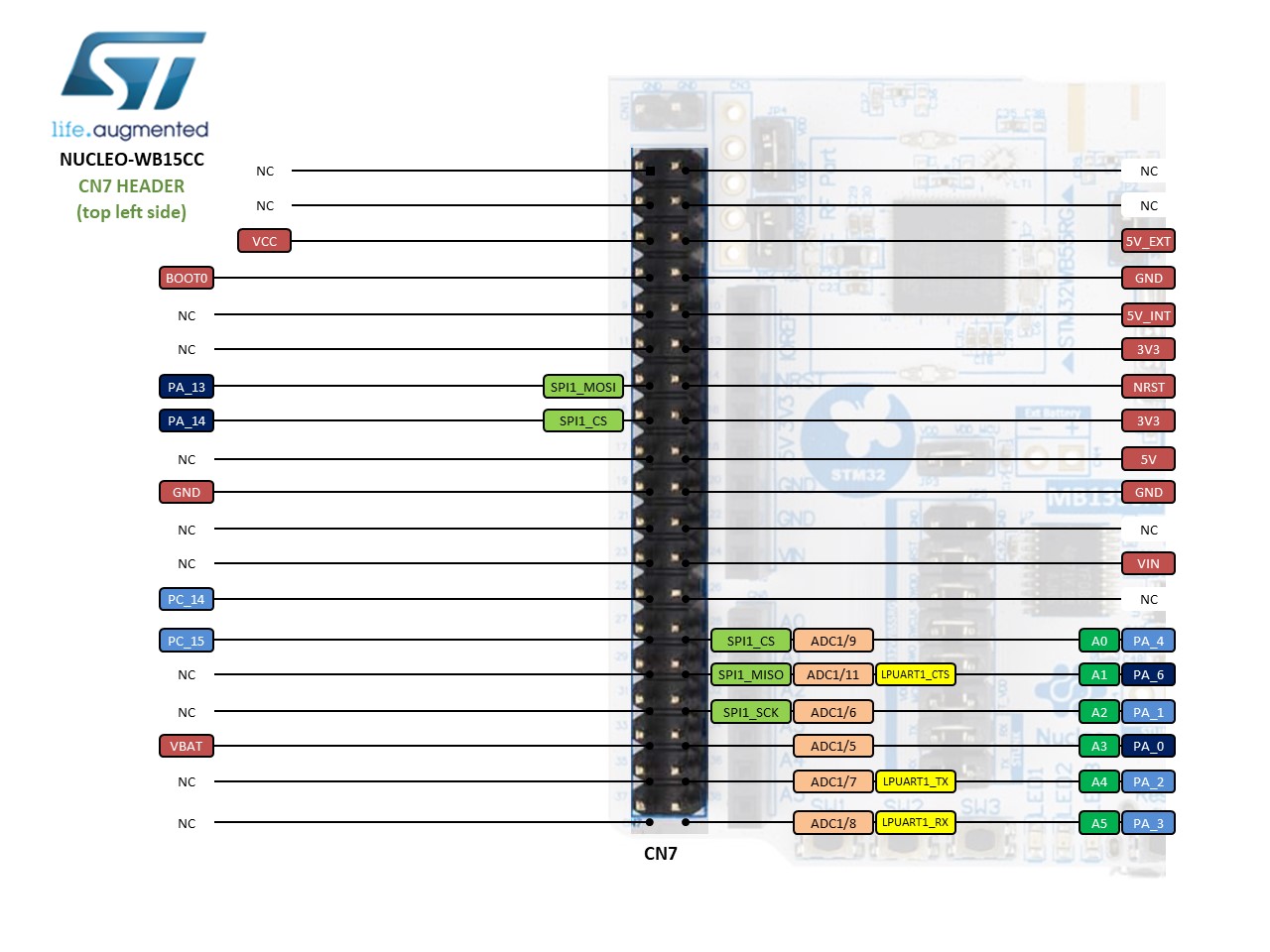

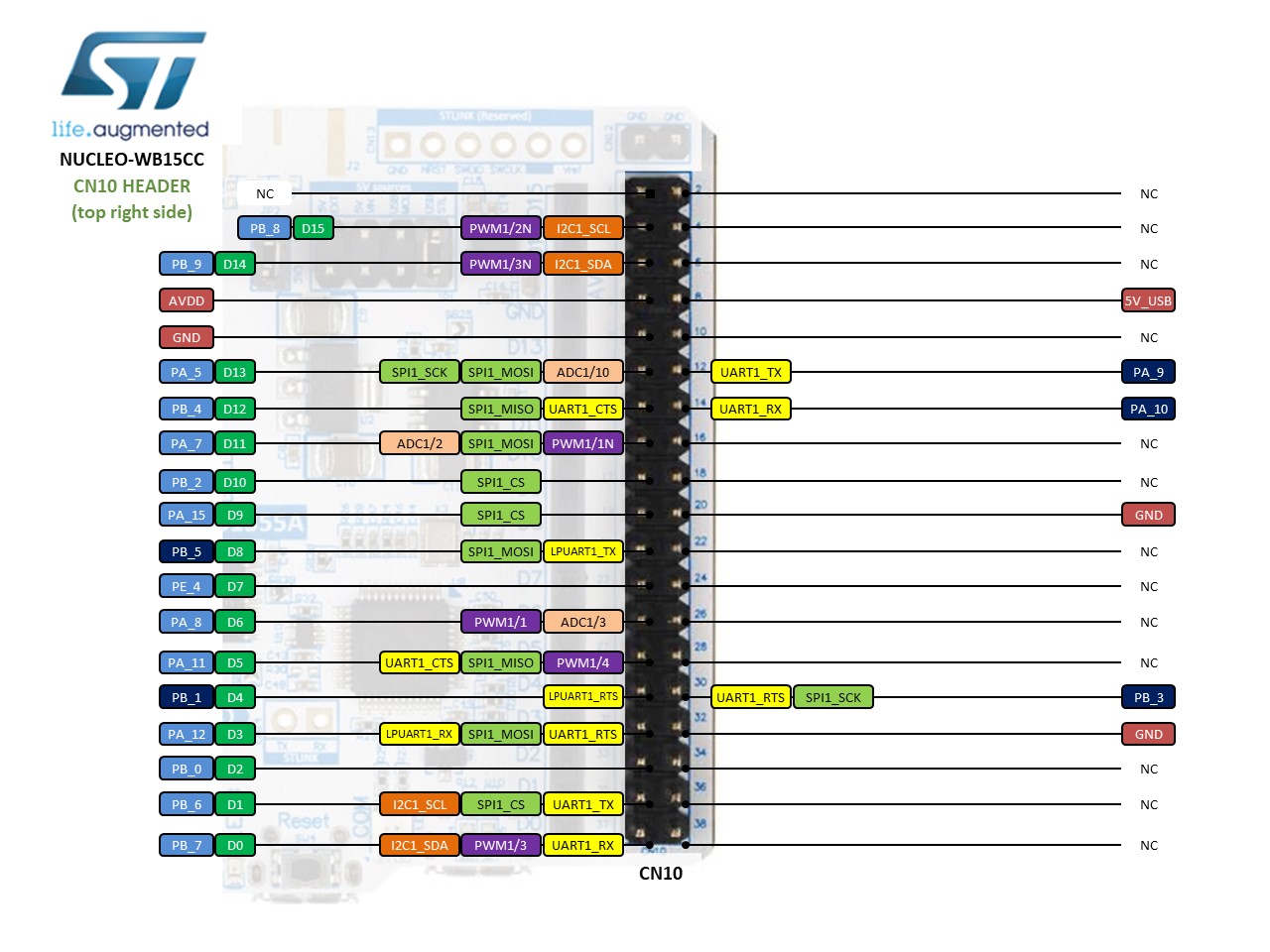

Morpho headers¶

These headers give access to all STM32 pins.

BLE FW update¶

Warning

Default BLE FW in NUCLEO boards is not compatible with Mbed OS. Read the following guide to update the firmware: https://github.com/ARMmbed/mbed-os/blob/master/targets/TARGET_STM/TARGET_STM32WB/README.md#stm32wb1x

Complete information: https://github.com/ARMmbed/mbed-os/blob/master/targets/TARGET_STM/TARGET_STM32WB/README.md

Tips and Tricks¶

https://github.com/ARMmbed/mbed-os/blob/master/targets/TARGET_STM/README.md

https://github.com/ARMmbed/mbed-os/blob/master/targets/TARGET_STM/TARGET_STM32WB/README.md

Find more information in ST WIKI pages.

Technical references¶

Board : https://www.st.com/en/evaluation-tools/nucleo-wb15cc.html

STM32WB15CC : https://www.st.com/en/microcontrollers-microprocessors/stm32wb15cc.html

Examples¶

Known limitations¶

The following section describes known limitations of the platform. Note that general issues are tracked into the mbed-os repository available on GitHub.

Warning

ARDUINO pins D0 and D1 can not be used as UART when UART console is used as they are using the same UART instance.

Warning

This board is not currently supported in Mbed Studio for debugging.

You need to log in to post a discussion