CoreLink SSE-100 (IOT Subsystem for Cortex-M)

The ARM® CoreLink SSE-100 allows design teams to create IoT endpoints faster and with lower risk. ARM simplifies IoT with its hardware and software, power efficiency and wide ecosystem support. The ARM IoT subsystem for ARM Cortex-M processors is optimized for use with ARM’s most efficient processor, mbed™OS, radio technologies and physical IP.

Subsystem Information

The CoreLink SSE-100 Subsystem has been implemented using an example design to connect to the peripherals of the Cortex-M Prototyping System+, this adds extra perhiperals to those included in the CoreLink SSE-100. This provides an easy to use platform for software development for the IoT subsystem.

If you have a licence for the CoreLink SSE-100 you can extend the design and make your own variant. CoreLink SSE-100 provides RTL and a range of deliverables including integration scripts, example integration, and other information to describe how best to configure ARM’s various IP components to target specific IoT devices.

Target Implementation

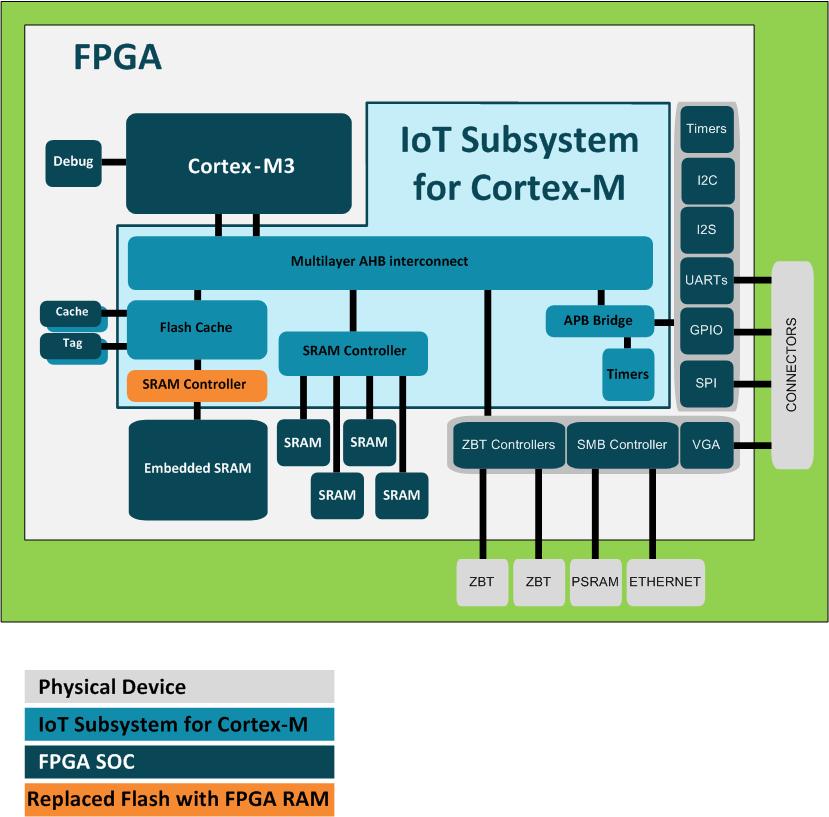

Application Note outlining IoT subsystem implemination in FPGA is avialable here AN491

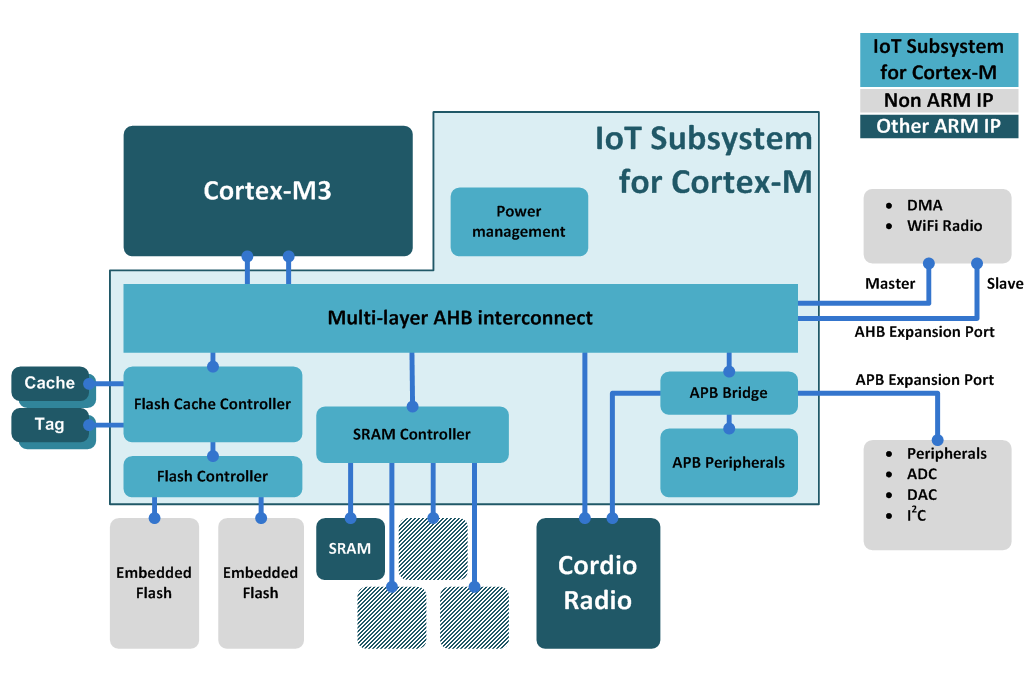

Diagram of IoT subsystem for Cortex-M

Further information is available here IoT Subsystems for Cortex-M

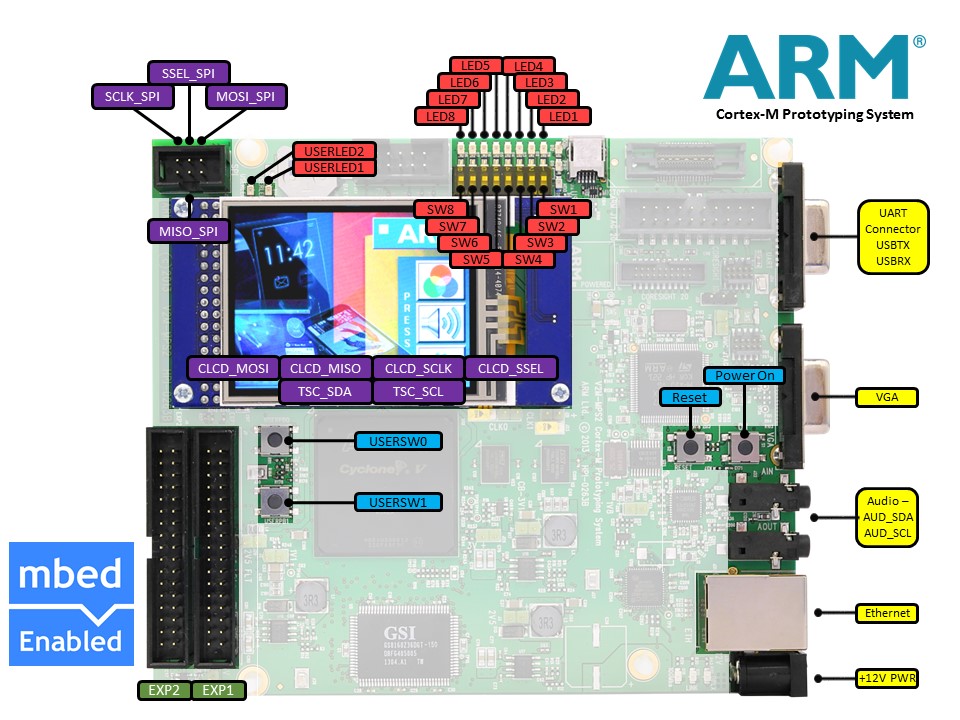

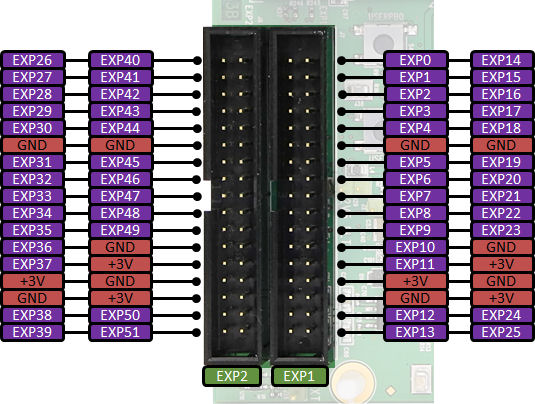

Cortex-M Prototypying System Pinout

Target Features

- List Form factor: 140x120cm

- SRAM: 8MB single cycle SRAM, 16MB PSRAM

- Video: QSVGA touch screen panel, 4bit RGB VGA connector

- Audio: Audio Codec

- Debug: ◦ARM JTAG20 connector

- ARM parallel trace connector (MICTOR38)

- 20 pin Cortex debug connector

- 10 pin Cortex debug connector

- ILA connector for FPGA debug

- Expansion

- GPIO

- SPI

More information on the platform available here MPS2+ product page

You need to log in to post a discussion