DigitalOutクラスを介さずに直接アクセスしてみたらどうだろうと思いやってみましたが、あんまり速くないですね。

GPIO

#include "mbed.h"

int main()

{

//init GPIO - DIO0:P2_15

GPIOPIBC2 = GPIOPIBC2 & 0x7fff;

GPIOPBDC2 = GPIOPBDC2 & 0x7fff;

GPIOPM2 = GPIOPM2 | 0x8000;

GPIOPMC2 = GPIOPMC2 & 0x7fff;

GPIOPIPC2 = GPIOPIPC2 & 0x7fff;

GPIOPIBC2 = GPIOPIBC2 & 0x7fff;

GPIOPM2 = GPIOPM2 & 0x7fff;

while(true) {

GPIOP2 = GPIOP2 | 0x8000;

GPIOP2 = GPIOP2 & 0x7fff;

}

}

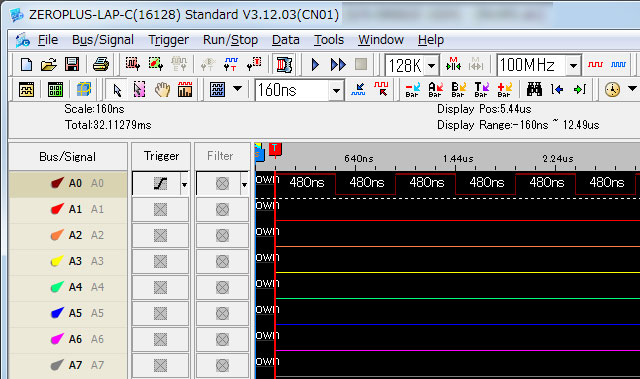

1回480nsなので、約1MHzといったところでしょうか。

Cortex-Aのアーキテクチャの詳細は把握してないのですが、ハードウェアマニュアル(Rev.1.00)のP.5-3の表によるとGPIOは周辺バス2に接続され、バス周波数はP0(33.33MHz)ということになっています。

Cortex-AはGPIOを全力でぶん回すような使い方をするものではないと思うので、こんなもんなんでしょうか。

それから、GR-PEACHのプログラムメモリは外付けSPIフラッシュから直接実行する仕様だと思います(ブートモード3)。

キャッシュに載るくらいの大きさならば問題無いのだろうと思いますが、ROMに置いたデータの読み込みは遅いのかなと。

試しに、1MBほどのデータをROMに置き、それを読み込むプログラムを作ってみましたが、32bitずつ読み出して24MB/s程度でした。

RAMからだと238MB/s程度だったので、10倍ほど差があるようです(CPUが遊んでしまいますね)。

400MHzのCortex-Mではないと認識して向き合う必要があるのだと感じています。

昨日、Lチカで負論理駆動の件に関して、質問させていただきました。

http://developer.mbed.org/questions/5446/1417268131/

今日、手元にあったいくつかのmbedでLチカの処理スピードを計測してみました。

使用したプログラムは、下記のものです。

Import programGR-PEACH_performance_check_0

Performance check program for LED blinky

Last commit 30 Nov 2014 by Kenji Arai

Kenji Arai

結果は下記のようになりました。

CPU性能と一対一で対応していないように見えるのは、やはりハードウェアレイヤーの隠ぺいの仕方に各ベンダーの個性が出ているからでしょうか?

昨日もQ&Aの中で、ADC処理スピードに関する質問がありましたが、GR-PEACHの実力に見合った結果が出るように期待します。

別にLチカが早い遅いと一喜一憂するつもりはありませんが、ほかのファンクション開発にも影響を与える基本的な部分ではないかと思い議論の口火を切りたいと思います。