Public Types |

Public Member Functions | |

| void | set_control_pins_auto () |

| Enable automatic selection and update of control pins. More... | |

| void | set_control_pins_manual (PinName clk, PinName mosi, PinName miso, PinName aux) |

| Set the control pins to use for communication. More... | |

| bool | firmware_dump (mbed::FileHandle *dest, mbed::Callback< void(uint8_t)> progress=mbed::Callback< void(uint8_t)>()) |

| Read FPGA CI Test Shield firmware. More... | |

| bool | firmware_dump_all (mbed::FileHandle *dest, mbed::Callback< void(uint8_t)> progress=mbed::Callback< void(uint8_t)>()) |

| Read FPGA CI Test Shield flash. More... | |

| bool | firmware_update (mbed::FileHandle *src, mbed::Callback< void(uint8_t)> progress=mbed::Callback< void(uint8_t)>()) |

| Program new FPGA CI Test Shield firmware. More... | |

| void | pin_map_set (PinName physical, LogicalPin logical) |

| Map a physical pin to the given logical pin. More... | |

| void | pin_map_reset () |

| Reset all pin mappings. More... | |

| void | peripherals_reset () |

| Reset all peripherals. More... | |

| void | reset () |

| Reset everything. More... | |

| void | reprogram () |

| Reprogram the FPGA. More... | |

| uint32_t | version () |

| Get the running FPGA firmware version. More... | |

| void | select_peripheral (Peripheral peripheral) |

| Select the currently active peripheral. More... | |

| int | gpio_read (LogicalPin gpio) |

| Read a gpio pin. More... | |

| void | gpio_write (LogicalPin gpio, int value, bool drive) |

| Set value and drive of a gpio pin. More... | |

| void | io_metrics_start () |

| Start recording metrics on all logical pins. More... | |

| void | io_metrics_stop () |

| Stop recording metrics on all logical pins. More... | |

| void | io_metrics_continue () |

| Continue recording metrics on all logical pins. More... | |

| uint32_t | io_metrics_min_pulse_low (LogicalPin pin) |

| Get the shortest low pulse recorded. More... | |

| uint32_t | io_metrics_min_pulse_high (LogicalPin pin) |

| Get the shortest high pulse recorded. More... | |

| uint32_t | io_metrics_max_pulse_low (LogicalPin pin) |

| Get the longest low pulse recorded. More... | |

| uint32_t | io_metrics_max_pulse_high (LogicalPin pin) |

| Get the longest high pulse recorded. More... | |

| uint32_t | io_metrics_rising_edges (LogicalPin pin) |

| Get the number of rising edges. More... | |

| uint32_t | io_metrics_falling_edges (LogicalPin pin) |

| Get the number of falling edges. More... | |

| void | pin_pull_reset_all () |

| Reset the IO expander modules. More... | |

| int | pin_set_pull (PinName pin, PullMode mode) |

| Configure an Mbed pin for a pulldown resistor, pullup resistor, or tristate mode via PinName. More... | |

| int | pin_set_pull_index (int index, PullMode mode) |

| Configure an Mbed pin for a pulldown resistor, pullup resistor, or tristate mode via pin index. More... | |

| uint8_t | io_expander_read (PinName pin, IOExpanderReg reg_type) |

| Read a bit for a specific Mbed pin that is set in the input, output, or configuration registers inside of the IO expander via PinName. More... | |

| uint8_t | io_expander_read_index (int index, IOExpanderReg reg_type) |

| Read a bit for a specific Mbed pin that is set in the input, output, or configuration registers inside of the IO expander via pin index. More... | |

| int | pin_set_pull_bb (PinName pin, PullMode mode) |

| Configure an Mbed pin for a pulldown resistor, pullup resistor, or tristate mode (this version of the function uses io_expander_i2c_read_bb and io_expander_i2c_write_bb) More... | |

| uint8_t | io_expander_read_bb (PinName pin, IOExpanderReg reg_type) |

| Read a bit for a specific Mbed pin that is set in the input, output, or configuration registers inside of the IO expander (this version of the function uses io_expander_i2c_read_bb) More... | |

| void | set_analog_out (bool enable, float voltage) |

| Create an analog voltage via the FPGA sys pwm in order to test Mbed AnalogIn. More... | |

| void | set_sample_adc (bool val) |

| Turn the FPGA ADC on and off (power management data will be collected while the ADC is on) More... | |

| float | get_analog_in () |

| Get the result of the analog to digital conversion computed on the FPGA in the form of a voltage reading. More... | |

| float | get_anin_voltage (int index) |

| Similar to 'get_analog_in' but returns a voltage reading from ANIN0-3. More... | |

| bool | sys_pin_read (SystemPin pin) |

| Read from the given system pin. More... | |

| void | sys_pin_write (SystemPin pin, int value, bool drive) |

| Write to the given system pin. More... | |

| int | io_expander_i2c_read (uint8_t i2c_index, uint8_t dev_addr, uint8_t start_reg, uint8_t *data, int length) |

| I2C read on I2C system channels 0, 1, or 2. More... | |

| int | io_expander_i2c_write (uint8_t i2c_index, uint8_t dev_addr, uint8_t *data, int length) |

| I2C write on I2C system channels 0, 1, or 2. More... | |

| int | io_expander_i2c_read_bb (SystemPin sda, SystemPin scl, uint8_t dev_addr, uint8_t start_reg, uint8_t *data, int length) |

| I2C read on I2C system channels 0, 1, or 2 (bit banged version of function, bit banged over control channel) More... | |

| int | io_expander_i2c_write_bb (SystemPin sda, SystemPin scl, uint8_t dev_addr, uint8_t *data, int length) |

| I2C write on I2C system channels 0, 1, or 2 (bit banged version of function, bit banged over control channel) More... | |

| int | set_mux_addr (PinName pin) |

| Set the AnalogMuxAddr pins on the FPGA via PinName. More... | |

| int | set_mux_addr_index (int index) |

| Set the AnalogMuxAddr pins on the FPGA via pin index. More... | |

| void | set_mux_enable (bool val) |

| Turn on/off the analog muxes. More... | |

| void | set_pwm_enable (bool val) |

| Turn on/off pwm output on FPGA to test Mbed AnalogIn. More... | |

| bool | get_pwm_enable () |

| Check if FPGA pwm out is on or off. More... | |

| void | set_pwm_period_and_cycles_high (uint32_t period, uint32_t cycles_high) |

| Set the pwm output period and number of cycles high (duty cycle) on the FPGA. More... | |

| uint32_t | get_pwm_period () |

| Get the pwm output period of the FPGA. More... | |

| uint8_t | get_pwm_cycles_high () |

| Get the number of cycles that are high (duty cycle) from FPGA pwm. More... | |

| uint16_t | get_analogmuxin_measurement () |

| Get the 12-bit analog to digital conversion result from the FPGA. More... | |

| uint16_t | get_anin_measurement (int index) |

| Similar to 'get_analogmuxin_measurement' but returns the current XADC measurement for ANIN0-3. More... | |

| void | get_anin_sum_samples_cycles (int index, uint64_t *sum, uint32_t *samples, uint64_t *cycles) |

| Gets (by reference) the sum of all ANIN ADC results for any of the 4 ANIN pins specified by the index, number of ADC sample sequences that have completed since the XADC was turned on, and the number of FPGA clk cycles that have taken place since the ADC was turned on. More... | |

| void | set_snapshot () |

| Allows safe reading of FPGA ADC related values while the FPGA ADC is on If snapshot is set then the ADC values will be safely latched in the FPGA and safe to read. More... | |

| void | sys_pin_mode_disabled () |

| Set the current system pin mode to disabled. More... | |

| void | sys_pin_mode_spi_serial_flash (PhysicalIndex mosi, PhysicalIndex miso, PhysicalIndex clk, PhysicalIndex ssel) |

| Set the current system pin mode to serial flash. More... | |

| void | sys_pin_mode_i2c_io_expander (int index, PhysicalIndex sda_in, PhysicalIndex sda_val, PhysicalIndex scl_in, PhysicalIndex scl_val) |

| Set the current system pin mode to io expander I2C bus. More... | |

| void | pin_map_index (PhysicalIndex physical_index, LogicalPin logical) |

| Map a physical pin index to the given logical pin. More... | |

| void | write (uint32_t addr, const uint8_t *data, uint32_t size) |

| Write to tester memory. More... | |

| void | read (uint32_t addr, uint8_t *data, uint32_t size) |

| Read from tester memory. More... | |

| bool | self_test_all () |

| Run all self tests. More... | |

| bool | self_test_control_channels () |

| Test that all allowed control channels can be used. More... | |

| bool | self_test_control_miso () |

| Test that all allowed control miso lines can be used. More... | |

| bool | self_test_control_current () |

| Test that the current control channel works. More... | |

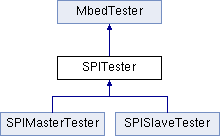

Definition at line 23 of file SPITester.h.

|

inherited |

FPGA Pullup mode.

Definition at line 404 of file MbedTester.h.

|

inherited |

Read FPGA CI Test Shield firmware.

Read the firmware on the FPGA CI Test Shield. An optional progress callback can be supplied to display progress while the firmware is being read.

| dest | File to write the firmware to. This file must have been opened as writeable |

| progress | Optional progress callback called when the percent complete changes |

|

inherited |

Read FPGA CI Test Shield flash.

Read the entire flash contents of the FPGA CI Test Shield. An optional progress callback can be supplied to display progress while the firmware is being read.

| dest | File to write the firmware to. This file must have been opened as writeable |

| progress | Optional progress callback called when the percent complete changes |

|

inherited |

Program new FPGA CI Test Shield firmware.

Program firmware from the file given. The binary bitstream must be in the correct format and contain a correct CRC or the update will fail. To correctly format a bitstream binary the post_process_bitstream.py script in the fpga-ci-test-shield repository should be used.

Note - release binaries for the FPGA CI Test Shield have already been formatted and can be loaded directly with this function

| src | File containing the new firmware to program |

| progress | Optional progress callback called when the percent complete changes |

|

inherited |

Get the result of the analog to digital conversion computed on the FPGA in the form of a voltage reading.

The FPGA ADC operates on 0V-1V, which means this function will only ever return a float ranging from 0.0-1.0.

|

inherited |

Get the 12-bit analog to digital conversion result from the FPGA.

|

inherited |

Similar to 'get_analogmuxin_measurement' but returns the current XADC measurement for ANIN0-3.

| index | ANIN pin to read (0-3) |

|

inherited |

Gets (by reference) the sum of all ANIN ADC results for any of the 4 ANIN pins specified by the index, number of ADC sample sequences that have completed since the XADC was turned on, and the number of FPGA clk cycles that have taken place since the ADC was turned on.

| index | ANIN pin of which to get sum of results (0-3) |

| sum | The sum of all specified ANIN pin's ADC results |

| samples | The number of ADC sample sequences that have completed since the XADC was turned on |

| cycles | The number of FPGA clk cycles that have taken place since the ADC was turned on |

|

inherited |

Similar to 'get_analog_in' but returns a voltage reading from ANIN0-3.

| index | ANIN pin to read (0-3) |

|

inherited |

Get the number of cycles that are high (duty cycle) from FPGA pwm.

|

inherited |

Check if FPGA pwm out is on or off.

|

inherited |

Get the pwm output period of the FPGA.

|

inherited |

Read a gpio pin.

| gpio | Logical pin to read from |

|

inherited |

Set value and drive of a gpio pin.

| gpio | Logical pin to write to |

| value | 0 to set the pin low or non-zero to set it high |

| driver | 0 to set the pin to Hi-Z or non-zero to drive the pin |

|

inherited |

I2C read on I2C system channels 0, 1, or 2.

| i2c_index | The number corresponding to the system i2c bus being used (0, 1, or 2) |

| dev_addr | The I2C address of the device being read from |

| start_reg | The internal device address where the read will start |

| data | Data buffer for data to be read into |

| length | The number of bytes to read |

|

inherited |

I2C read on I2C system channels 0, 1, or 2 (bit banged version of function, bit banged over control channel)

| sda | System pin used for sda |

| scl | System pin used for scl |

| dev_addr | The I2C address of the device being read from |

| start_reg | The internal device address where the read will start |

| data | Data buffer for data to be read into |

| length | The number of bytes to read |

|

inherited |

I2C write on I2C system channels 0, 1, or 2.

| i2c_index | The number corresponding to the system i2c bus being used (0, 1, or 2) |

| dev_addr | The I2C address of the device being written to |

| data | The data to be written |

| length | The number of bytes to be written |

|

inherited |

I2C write on I2C system channels 0, 1, or 2 (bit banged version of function, bit banged over control channel)

| sda | System pin used for sda |

| scl | System pin used for scl |

| dev_addr | The I2C address of the device being written to |

| data | The data to be written |

| length | The number of bytes to be written |

|

inherited |

Read a bit for a specific Mbed pin that is set in the input, output, or configuration registers inside of the IO expander via PinName.

| pin | Mbed pin whose register bit is being read |

| reg_type | Pin register to access, options are: MbedTester::RegInput, MbedTester::RegOutput, or MbedTester::RegConfig |

|

inherited |

Read a bit for a specific Mbed pin that is set in the input, output, or configuration registers inside of the IO expander (this version of the function uses io_expander_i2c_read_bb)

| pin | Mbed pin whose register bit is being read |

| reg_type | Pin register to access, options are: MbedTester::RegInput, MbedTester::RegOutput, or MbedTester::RegConfig |

|

inherited |

Read a bit for a specific Mbed pin that is set in the input, output, or configuration registers inside of the IO expander via pin index.

| index | Mbed pin index whose register bit is being read |

| reg_type | Pin register to access, options are: MbedTester::RegInput, MbedTester::RegOutput, or MbedTester::RegConfig |

|

inherited |

Continue recording metrics on all logical pins.

Resume recording metrics.

|

inherited |

Get the number of falling edges.

| pin | Pin to read the metrics for |

|

inherited |

Get the longest high pulse recorded.

| pin | Pin to read the metrics for |

|

inherited |

Get the longest low pulse recorded.

| pin | Pin to read the metrics for |

|

inherited |

Get the shortest high pulse recorded.

| pin | Pin to read the metrics for |

|

inherited |

Get the shortest low pulse recorded.

| pin | Pin to read the metrics for |

|

inherited |

Get the number of rising edges.

| pin | Pin to read the metrics for |

|

inherited |

Start recording metrics on all logical pins.

This function resets all past metrics to 0. To preserve these call io_metrics_continue instead.

|

inherited |

Stop recording metrics on all logical pins.

This function should be called before any metrics are read to ensure the value does not change while they are being read.

|

inherited |

Reset all peripherals.

This does not reset the pin mappings

|

inherited |

Map a physical pin index to the given logical pin.

This function will automatically move the control channel pins to avoid interfering with the mapped pin. The physical pin index does not need to be part of the form factor.

| physical_index | Index of the physical pin on the board |

| logical | Logical pin to map to |

|

inherited |

Reset all pin mappings.

After this call all pins will be unmapped

|

inherited |

Map a physical pin to the given logical pin.

This function will automatically move the control channel pins to avoid interfering with the mapped pin.

| physical | Physical pin on the board |

| logical | Logical pin to map to |

|

inherited |

Reset the IO expander modules.

|

inherited |

Configure an Mbed pin for a pulldown resistor, pullup resistor, or tristate mode via PinName.

| pin | Mbed pin whose mode is being set |

| mode | (MbedTester::PullUp, MbedTester::PullDown, or MbedTester::PullNone) |

|

inherited |

Configure an Mbed pin for a pulldown resistor, pullup resistor, or tristate mode (this version of the function uses io_expander_i2c_read_bb and io_expander_i2c_write_bb)

| pin | Mbed pin whose mode is being set |

| mode | (MbedTester::PullUp, MbedTester::PullDown, or MbedTester::PullNone) |

|

inherited |

Configure an Mbed pin for a pulldown resistor, pullup resistor, or tristate mode via pin index.

| index | Mbed pin index whose mode is being set |

| mode | (MbedTester::PullUp, MbedTester::PullDown, or MbedTester::PullNone) |

|

inherited |

Read from tester memory.

addr Address to read from

| data | Buffer to fill with data |

| size | Number of bytes to read |

|

inherited |

Reprogram the FPGA.

This function causes the FPGA to reboot and reload RAM contents. This should be used after MbedTester::firmware_update to load the new image.

|

inherited |

Reset everything.

This function resets the state of both the FPGA CI Test Shield and the MbedTester object itself.

Reset effects on the FPGA CI Test Shield include:

Reset effects on the MbedTester object include

|

inherited |

Select the currently active peripheral.

| peripheral | Active peripheral |

|

inherited |

Run all self tests.

|

inherited |

Test that all allowed control channels can be used.

Check that all pairs of clk and mosi which aren't in the restricted list can be used.

|

inherited |

Test that the current control channel works.

|

inherited |

Test that all allowed control miso lines can be used.

Check that every pin of this form factor aside from the pins in the restricted list can be used as miso.

|

inherited |

Create an analog voltage via the FPGA sys pwm in order to test Mbed AnalogIn.

| enable | Enable the FPGA system PWM (false: of, true: on) |

| voltage | The analog voltage that will be created by the FPGA CI test shield (float: 0.0 to 1.0) |

|

inherited |

Enable automatic selection and update of control pins.

Calling this function configures MbedTester to automatically select and update the control pins. The control pins are moved if the function MbedTester::pin_map_set is called and maps a pin that is being used for control.

|

inherited |

Set the control pins to use for communication.

Manually set the control pins. Calling this function disables automatic control pin selection and updates. The function MbedTester::pin_map_set must not be used to map over control pins when in this mode.

| clk | Clock pin to use as the control channel |

| mosi | Mosi pin to use as the control channel |

| miso | Miso pin to use as the control channel |

| aux | Auxillary pin to use as the control cannel |

|

inherited |

Set the AnalogMuxAddr pins on the FPGA via PinName.

| pin | The Mbed pin that the analog signal will be routed to |

|

inherited |

Set the AnalogMuxAddr pins on the FPGA via pin index.

| index | The Mbed pin index that the analog signal will be routed to |

|

inherited |

Turn on/off the analog muxes.

| val | false: off, true: on |

|

inherited |

Turn on/off pwm output on FPGA to test Mbed AnalogIn.

| val | false: off, true: on |

|

inherited |

Set the pwm output period and number of cycles high (duty cycle) on the FPGA.

| period | In units of clk cycles |

| cycles_high | In units of clk cycles |

|

inherited |

Turn the FPGA ADC on and off (power management data will be collected while the ADC is on)

| val | FPGA ADC enable bit (false: off, true: on) |

|

inherited |

Allows safe reading of FPGA ADC related values while the FPGA ADC is on If snapshot is set then the ADC values will be safely latched in the FPGA and safe to read.

The RTL will set snapshot to 0 after 1 clk cycle.

|

inherited |

Set the current system pin mode to disabled.

This releases any pin mappings that were set by the previous pin mode.

|

inherited |

Set the current system pin mode to io expander I2C bus.

Remap physical pins to the io expander I2C bus. The IO expanders are used for setting pullups and pulldowns.

| index | The index of the I2C bus to connect to |

| sda_in | Physical pin index for the FPGA to output the state of SDA on |

| sda_val | Physical pin index for the FPGA to read SDA from. When in this mode the Mbed board must always drive this pin. Driving a 0 causes the FPGA to pull the SDA on the I2C bus low. Setting a 1 causes the FPGA to let SDA on the I2C bus float (and get pulled to 1). |

| scl_in | Physical pin index for the FPGA to output the state of SCL on |

| scl_val | Physical pin index for the FPGA to read SCL from. When in this mode the Mbed board must always drive this pin. Driving a 0 causes the FPGA to pull the SCL on the I2C bus low. Setting a 1 causes the FPGA to let SDA on the SCL bus float (and get pulled to 1). |

|

inherited |

Set the current system pin mode to serial flash.

Remap physical pins to the serial flash the FPGA boots from. This is used for firmware updates.

| mosi | The physical pin index to connect to serial flash mosi |

| miso | The physical pin index to connect to serial flash miso |

| clk | The physical pin index to connect to serial flash clk |

| ssel | The physical pin index to connect to serial flash cs |

|

inherited |

Read from the given system pin.

| pin | The pin to read from |

|

inherited |

Write to the given system pin.

| pin | The pin to write to |

| value | The value to output on the pin when driven |

| true | to drive the output, false to set the output high-z |

|

inherited |

Get the running FPGA firmware version.

|

inherited |

Write to tester memory.

addr Address to write to

| data | Data to write |

| size | Number of bytes to write |