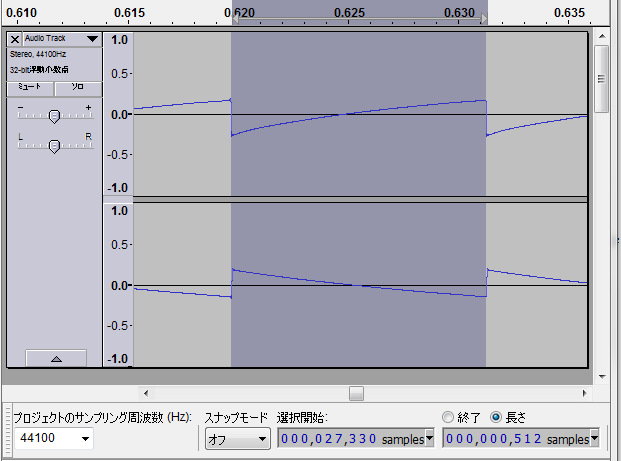

Part of MicroGen4 Music Synthesizer Program. (But not test it yet.) I2S ,DMA ,Stereo ,16Bit Dac(PCM1781) See detail: http://www.geocities.jp/micro_diys/index2

Now added generate Saw Wave to DAC function in generate();

You will hear Stereo saw wave sound now.

more info: http://www.geocities.jp/micro_diys/i2s_test_sample/i2s_test_sample.html

device.cpp@1:48f506a7b488, 2017-09-21 (annotated)

- Committer:

- p_igmon

- Date:

- Thu Sep 21 10:20:50 2017 +0000

- Revision:

- 1:48f506a7b488

- Parent:

- 0:dc88722ab141

Added Sample Saw Wave in Function Generate.

; DAC PCM1781 Can Output Saw Wave now.

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| p_igmon | 0:dc88722ab141 | 1 | /** |

| p_igmon | 0:dc88722ab141 | 2 | * COPYRIGHT(c) 2014 STMicroelectronics |

| p_igmon | 0:dc88722ab141 | 3 | * |

| p_igmon | 0:dc88722ab141 | 4 | * Redistribution and use in source and binary forms, with or without modification, |

| p_igmon | 0:dc88722ab141 | 5 | * are permitted provided that the following conditions are met: |

| p_igmon | 0:dc88722ab141 | 6 | * 1. Redistributions of source code must retain the above copyright notice, |

| p_igmon | 0:dc88722ab141 | 7 | * this list of conditions and the following disclaimer. |

| p_igmon | 0:dc88722ab141 | 8 | * 2. Redistributions in binary form must reproduce the above copyright notice, |

| p_igmon | 0:dc88722ab141 | 9 | * this list of conditions and the following disclaimer in the documentation |

| p_igmon | 0:dc88722ab141 | 10 | * and/or other materials provided with the distribution. |

| p_igmon | 0:dc88722ab141 | 11 | * 3. Neither the name of STMicroelectronics nor the names of its contributors |

| p_igmon | 0:dc88722ab141 | 12 | * may be used to endorse or promote products derived from this software |

| p_igmon | 0:dc88722ab141 | 13 | * without specific prior written permission. |

| p_igmon | 0:dc88722ab141 | 14 | * |

| p_igmon | 0:dc88722ab141 | 15 | * THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" |

| p_igmon | 0:dc88722ab141 | 16 | * AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE |

| p_igmon | 0:dc88722ab141 | 17 | * IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE |

| p_igmon | 0:dc88722ab141 | 18 | * DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE |

| p_igmon | 0:dc88722ab141 | 19 | * FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL |

| p_igmon | 0:dc88722ab141 | 20 | * DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR |

| p_igmon | 0:dc88722ab141 | 21 | * SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER |

| p_igmon | 0:dc88722ab141 | 22 | * CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, |

| p_igmon | 0:dc88722ab141 | 23 | * OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE |

| p_igmon | 0:dc88722ab141 | 24 | * OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE. |

| p_igmon | 0:dc88722ab141 | 25 | * |

| p_igmon | 0:dc88722ab141 | 26 | ****************************************************************************** |

| p_igmon | 0:dc88722ab141 | 27 | */ |

| p_igmon | 0:dc88722ab141 | 28 | |

| p_igmon | 0:dc88722ab141 | 29 | #include "synthesizer.h" |

| p_igmon | 0:dc88722ab141 | 30 | |

| p_igmon | 0:dc88722ab141 | 31 | /* Private variables ---------------------------------------------------------*/ |

| p_igmon | 0:dc88722ab141 | 32 | I2S_HandleTypeDef hi2s2; |

| p_igmon | 0:dc88722ab141 | 33 | DMA_HandleTypeDef hdma_i2s2_ext_tx; |

| p_igmon | 0:dc88722ab141 | 34 | |

| p_igmon | 0:dc88722ab141 | 35 | |

| p_igmon | 0:dc88722ab141 | 36 | /* Private function prototypes -----------------------------------------------*/ |

| p_igmon | 0:dc88722ab141 | 37 | static void SystemClock_Config(void); |

| p_igmon | 0:dc88722ab141 | 38 | static void MX_DMA_Init(void); |

| p_igmon | 0:dc88722ab141 | 39 | static void MX_I2S2_Init(void); |

| p_igmon | 0:dc88722ab141 | 40 | |

| p_igmon | 0:dc88722ab141 | 41 | |

| p_igmon | 0:dc88722ab141 | 42 | void uGen4_device_init(void) |

| p_igmon | 0:dc88722ab141 | 43 | { |

| p_igmon | 0:dc88722ab141 | 44 | /* Reset of all peripherals, Initializes the Flash interface and the Systick. */ |

| p_igmon | 0:dc88722ab141 | 45 | HAL_Init(); |

| p_igmon | 0:dc88722ab141 | 46 | |

| p_igmon | 0:dc88722ab141 | 47 | /* Configure the system clock */ |

| p_igmon | 0:dc88722ab141 | 48 | SystemClock_Config();// Set RCC I2S Clock |

| p_igmon | 0:dc88722ab141 | 49 | |

| p_igmon | 0:dc88722ab141 | 50 | /* Initialize all configured peripherals */ |

| p_igmon | 0:dc88722ab141 | 51 | MX_GPIO_Init();// GPIO CLOCK Enable |

| p_igmon | 0:dc88722ab141 | 52 | MX_DMA_Init(); |

| p_igmon | 0:dc88722ab141 | 53 | MX_I2S2_Init(); |

| p_igmon | 0:dc88722ab141 | 54 | } |

| p_igmon | 0:dc88722ab141 | 55 | |

| p_igmon | 0:dc88722ab141 | 56 | |

| p_igmon | 0:dc88722ab141 | 57 | /** System Clock Configuration |

| p_igmon | 0:dc88722ab141 | 58 | */ |

| p_igmon | 0:dc88722ab141 | 59 | static void SystemClock_Config(void) |

| p_igmon | 0:dc88722ab141 | 60 | { |

| p_igmon | 0:dc88722ab141 | 61 | |

| p_igmon | 0:dc88722ab141 | 62 | RCC_ClkInitTypeDef RCC_ClkInitStruct; |

| p_igmon | 0:dc88722ab141 | 63 | RCC_PeriphCLKInitTypeDef PeriphClkInitStruct; |

| p_igmon | 0:dc88722ab141 | 64 | RCC_OscInitTypeDef RCC_OscInitStruct; |

| p_igmon | 0:dc88722ab141 | 65 | |

| p_igmon | 0:dc88722ab141 | 66 | __PWR_CLK_ENABLE(); |

| p_igmon | 0:dc88722ab141 | 67 | |

| p_igmon | 0:dc88722ab141 | 68 | __HAL_PWR_VOLTAGESCALING_CONFIG(PWR_REGULATOR_VOLTAGE_SCALE2); |

| p_igmon | 0:dc88722ab141 | 69 | |

| p_igmon | 0:dc88722ab141 | 70 | RCC_OscInitStruct.OscillatorType = RCC_OSCILLATORTYPE_HSI; |

| p_igmon | 0:dc88722ab141 | 71 | RCC_OscInitStruct.HSIState = RCC_HSI_ON; |

| p_igmon | 0:dc88722ab141 | 72 | RCC_OscInitStruct.HSICalibrationValue = 6; |

| p_igmon | 0:dc88722ab141 | 73 | RCC_OscInitStruct.PLL.PLLState = RCC_PLL_ON; |

| p_igmon | 0:dc88722ab141 | 74 | RCC_OscInitStruct.PLL.PLLSource = RCC_PLLSOURCE_HSI; |

| p_igmon | 0:dc88722ab141 | 75 | RCC_OscInitStruct.PLL.PLLM = 16; |

| p_igmon | 0:dc88722ab141 | 76 | RCC_OscInitStruct.PLL.PLLN = 336; |

| p_igmon | 0:dc88722ab141 | 77 | RCC_OscInitStruct.PLL.PLLP = RCC_PLLP_DIV4; |

| p_igmon | 0:dc88722ab141 | 78 | RCC_OscInitStruct.PLL.PLLQ = 4; |

| p_igmon | 0:dc88722ab141 | 79 | HAL_RCC_OscConfig(&RCC_OscInitStruct); |

| p_igmon | 0:dc88722ab141 | 80 | |

| p_igmon | 0:dc88722ab141 | 81 | RCC_ClkInitStruct.ClockType = RCC_CLOCKTYPE_SYSCLK|RCC_CLOCKTYPE_PCLK1; |

| p_igmon | 0:dc88722ab141 | 82 | RCC_ClkInitStruct.SYSCLKSource = RCC_SYSCLKSOURCE_PLLCLK; |

| p_igmon | 0:dc88722ab141 | 83 | RCC_ClkInitStruct.AHBCLKDivider = RCC_SYSCLK_DIV1; |

| p_igmon | 0:dc88722ab141 | 84 | RCC_ClkInitStruct.APB1CLKDivider = RCC_HCLK_DIV2; |

| p_igmon | 0:dc88722ab141 | 85 | RCC_ClkInitStruct.APB2CLKDivider = RCC_HCLK_DIV1; |

| p_igmon | 0:dc88722ab141 | 86 | HAL_RCC_ClockConfig(&RCC_ClkInitStruct, FLASH_LATENCY_2); |

| p_igmon | 0:dc88722ab141 | 87 | |

| p_igmon | 0:dc88722ab141 | 88 | PeriphClkInitStruct.PeriphClockSelection = RCC_PERIPHCLK_I2S; |

| p_igmon | 0:dc88722ab141 | 89 | PeriphClkInitStruct.PLLI2S.PLLI2SN = 290; |

| p_igmon | 0:dc88722ab141 | 90 | PeriphClkInitStruct.PLLI2S.PLLI2SR = 2; |

| p_igmon | 0:dc88722ab141 | 91 | HAL_RCCEx_PeriphCLKConfig(&PeriphClkInitStruct); |

| p_igmon | 0:dc88722ab141 | 92 | |

| p_igmon | 0:dc88722ab141 | 93 | } |

| p_igmon | 0:dc88722ab141 | 94 | |

| p_igmon | 0:dc88722ab141 | 95 | /* I2S2 init function */ |

| p_igmon | 0:dc88722ab141 | 96 | void MX_I2S2_Init(void) |

| p_igmon | 0:dc88722ab141 | 97 | { |

| p_igmon | 0:dc88722ab141 | 98 | |

| p_igmon | 0:dc88722ab141 | 99 | hi2s2.Instance = SPI2; |

| p_igmon | 0:dc88722ab141 | 100 | hi2s2.Init.Mode = I2S_MODE_MASTER_TX; |

| p_igmon | 0:dc88722ab141 | 101 | hi2s2.Init.Standard = I2S_STANDARD_PHILLIPS; |

| p_igmon | 0:dc88722ab141 | 102 | hi2s2.Init.DataFormat = I2S_DATAFORMAT_16B; |

| p_igmon | 0:dc88722ab141 | 103 | hi2s2.Init.MCLKOutput = I2S_MCLKOUTPUT_ENABLE; |

| p_igmon | 0:dc88722ab141 | 104 | hi2s2.Init.AudioFreq = I2S_AUDIOFREQ_44K; |

| p_igmon | 0:dc88722ab141 | 105 | hi2s2.Init.CPOL = I2S_CPOL_LOW; |

| p_igmon | 0:dc88722ab141 | 106 | hi2s2.Init.ClockSource = I2S_CLOCK_PLL; |

| p_igmon | 0:dc88722ab141 | 107 | hi2s2.Init.FullDuplexMode = I2S_FULLDUPLEXMODE_DISABLE; |

| p_igmon | 0:dc88722ab141 | 108 | HAL_I2S_Init(&hi2s2); |

| p_igmon | 0:dc88722ab141 | 109 | |

| p_igmon | 0:dc88722ab141 | 110 | } |

| p_igmon | 0:dc88722ab141 | 111 | |

| p_igmon | 0:dc88722ab141 | 112 | |

| p_igmon | 0:dc88722ab141 | 113 | /** |

| p_igmon | 0:dc88722ab141 | 114 | * Enable DMA controller clock |

| p_igmon | 0:dc88722ab141 | 115 | */ |

| p_igmon | 0:dc88722ab141 | 116 | void MX_DMA_Init(void) |

| p_igmon | 0:dc88722ab141 | 117 | { |

| p_igmon | 0:dc88722ab141 | 118 | /* DMA controller clock enable */ |

| p_igmon | 0:dc88722ab141 | 119 | __DMA1_CLK_ENABLE(); |

| p_igmon | 0:dc88722ab141 | 120 | |

| p_igmon | 0:dc88722ab141 | 121 | /* DMA interrupt init */ |

| p_igmon | 0:dc88722ab141 | 122 | NVIC_SetVector(DMA1_Stream4_IRQn, (uint32_t )&DMA1_Stream4_IRQHandler); |

| p_igmon | 0:dc88722ab141 | 123 | /* Sets the priority grouping field */ |

| p_igmon | 0:dc88722ab141 | 124 | HAL_NVIC_SetPriorityGrouping(NVIC_PRIORITYGROUP_0); |

| p_igmon | 0:dc88722ab141 | 125 | HAL_NVIC_SetPriority(DMA1_Stream4_IRQn, 0, 0); |

| p_igmon | 0:dc88722ab141 | 126 | HAL_NVIC_EnableIRQ(DMA1_Stream4_IRQn); |

| p_igmon | 0:dc88722ab141 | 127 | } |

| p_igmon | 0:dc88722ab141 | 128 | |

| p_igmon | 0:dc88722ab141 | 129 | /** Pinout Configuration |

| p_igmon | 0:dc88722ab141 | 130 | */ |

| p_igmon | 0:dc88722ab141 | 131 | void MX_GPIO_Init(void) |

| p_igmon | 0:dc88722ab141 | 132 | { |

| p_igmon | 0:dc88722ab141 | 133 | |

| p_igmon | 0:dc88722ab141 | 134 | /* GPIO Ports Clock Enable */ |

| p_igmon | 0:dc88722ab141 | 135 | __GPIOC_CLK_ENABLE(); |

| p_igmon | 0:dc88722ab141 | 136 | __GPIOB_CLK_ENABLE(); |

| p_igmon | 0:dc88722ab141 | 137 | __GPIOA_CLK_ENABLE(); |

| p_igmon | 0:dc88722ab141 | 138 | |

| p_igmon | 0:dc88722ab141 | 139 | } |

| p_igmon | 0:dc88722ab141 | 140 | |

| p_igmon | 0:dc88722ab141 | 141 | |

| p_igmon | 0:dc88722ab141 | 142 | #ifdef USE_FULL_ASSERT |

| p_igmon | 0:dc88722ab141 | 143 | |

| p_igmon | 0:dc88722ab141 | 144 | /** |

| p_igmon | 0:dc88722ab141 | 145 | * @brief Reports the name of the source file and the source line number |

| p_igmon | 0:dc88722ab141 | 146 | * where the assert_param error has occurred. |

| p_igmon | 0:dc88722ab141 | 147 | * @param file: pointer to the source file name |

| p_igmon | 0:dc88722ab141 | 148 | * @param line: assert_param error line source number |

| p_igmon | 0:dc88722ab141 | 149 | * @retval None |

| p_igmon | 0:dc88722ab141 | 150 | */ |

| p_igmon | 0:dc88722ab141 | 151 | void assert_failed(uint8_t* file, uint32_t line) |

| p_igmon | 0:dc88722ab141 | 152 | { |

| p_igmon | 0:dc88722ab141 | 153 | /* User can add his own implementation to report the file name and line number, |

| p_igmon | 0:dc88722ab141 | 154 | ex: printf("Wrong parameters value: file %s on line %d\r\n", file, line) */ |

| p_igmon | 0:dc88722ab141 | 155 | |

| p_igmon | 0:dc88722ab141 | 156 | } |

| p_igmon | 0:dc88722ab141 | 157 | |

| p_igmon | 0:dc88722ab141 | 158 | #endif |

| p_igmon | 0:dc88722ab141 | 159 | |

| p_igmon | 0:dc88722ab141 | 160 | |

| p_igmon | 0:dc88722ab141 | 161 | /************************ (C) COPYRIGHT STMicroelectronics *****END OF FILE****/ |

| p_igmon | 0:dc88722ab141 | 162 | |

| p_igmon | 0:dc88722ab141 | 163 | |

| p_igmon | 0:dc88722ab141 | 164 | |

| p_igmon | 0:dc88722ab141 | 165 |