The official mbed C/C SDK provides the software platform and libraries to build your applications.

Fork of mbed by

(01.May.2014) started sales! http://www.switch-science.com/catalog/1717/

(13.March.2014) updated to 0.5.0

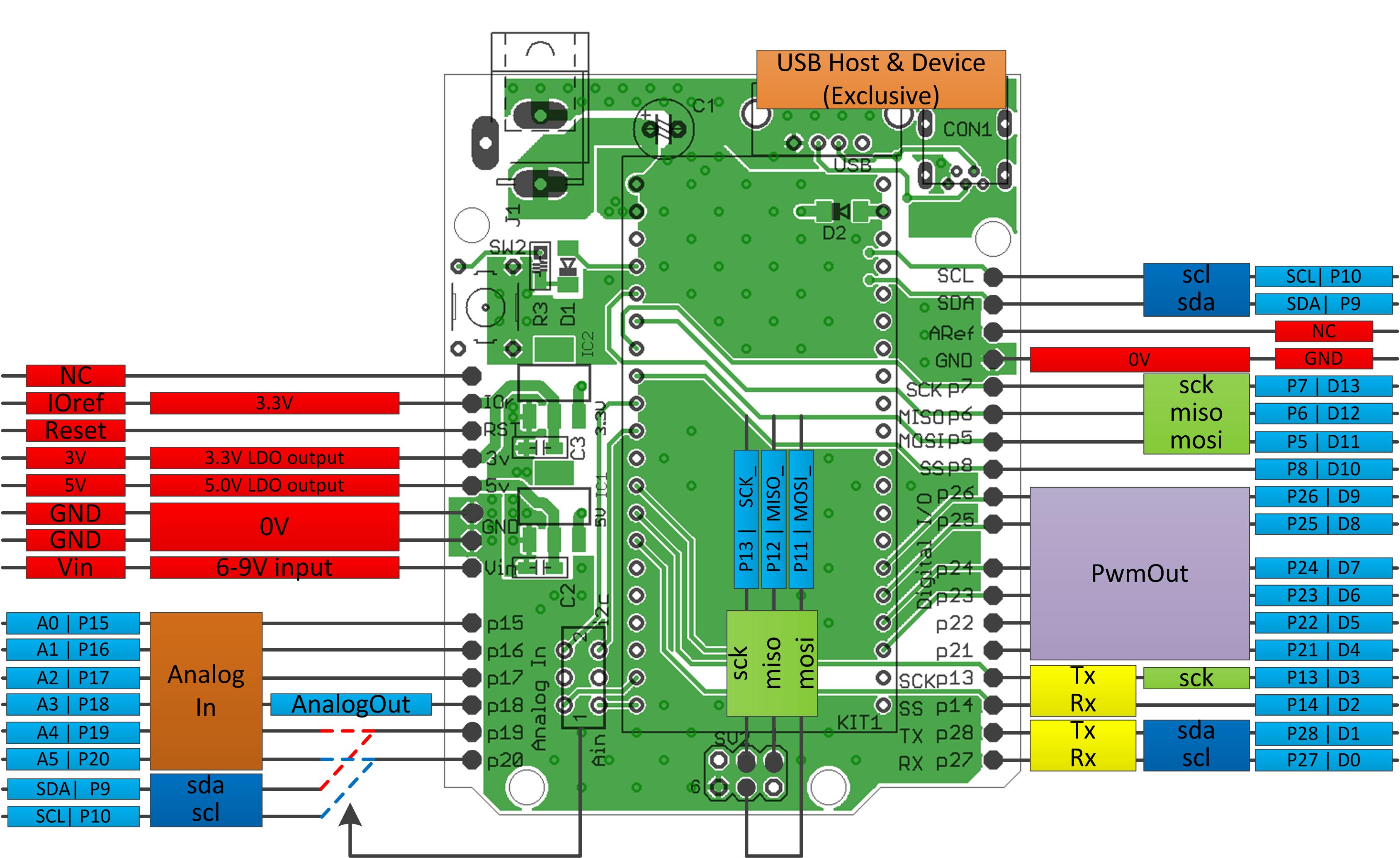

This is a pin conversion PCB from mbed 1768/11U24 to arduino UNO.

- So if you have both mbed and arduino shields, I guess you would be happy with such a conversion board :)

Photos

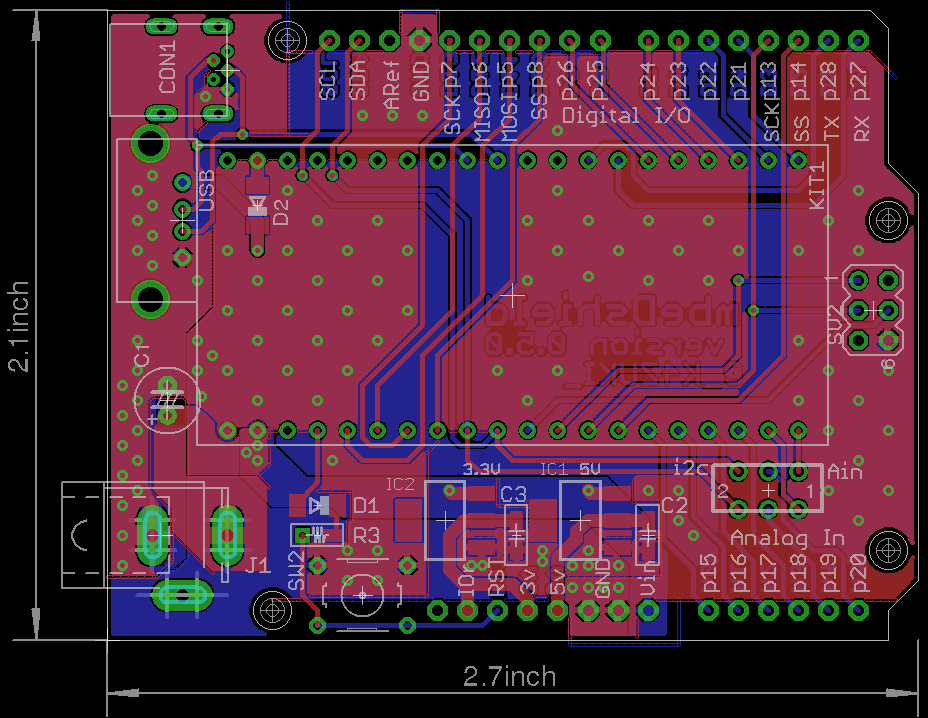

- Board photo vvv

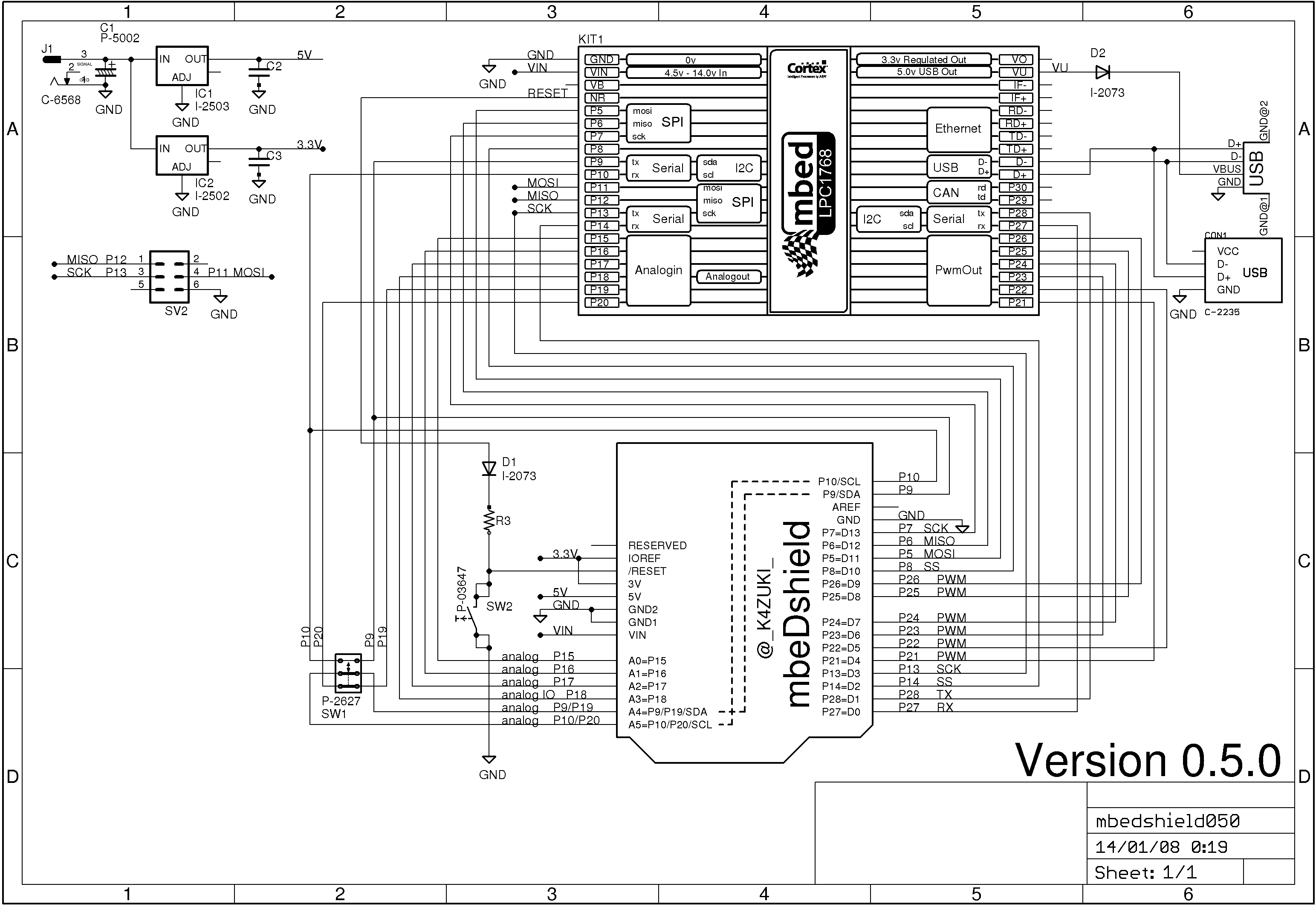

- Schematic photo vvv

- Functionality photo vvv

Latest eagle files

PCB >> /media/uploads/k4zuki/mbedshield050.brd

SCH >> /media/uploads/k4zuki/mbedshield050.sch

BIG changes from previous version

- Ethernet RJ45 connector is removed.

- http://mbed.org/components/Seeed-Ethernet-Shield-V20/ is the biggest hint to use Ethernet!

MostALL of components can be bought at Akizuki http://akizukidenshi.com/- But sorry, they do not send parts to abroad

- Pinout is changed!

| arduino | 0.4.0 | 0.5.0 |

|---|---|---|

| D4 | p12 | p21 |

| D5 | p11 | p22 |

| MOSI_ | none | p11 |

| MISO_ | none | p12 |

| SCK_ | none | p13 |

This design has bug(s)

- I2C functional pin differs between 1768 and 11U24.

Fixed bugs here

- MiniUSB cable cannot be connected on mbed if you solder high-height electrolytic capacitor on C3.

- http://akizukidenshi.com/catalog/g/gP-05002/ is the solution to make this 100% AKIZUKI parts!

- the 6-pin ISP port is not inprimented in version 0.4.0

it will be fixed in later version 0.4.1/0.4.2/0.5.0This has beenfixed

I am doing some porting to use existing arduino shields but it may faster if you do it by yourself...

you can use arduino PinName "A0-A5,D0-D13" plus backside SPI port for easier porting.

To do this you have to edit PinName enum in

- "mbed/TARGET_LPC1768/PinNames.h" or

- "mbed/TARGET_LPC11U24/PinNames.h" as per your target mbed.

here is the actual list: This list includes define switch to switch pin assignment

part_of_PinNames.h

USBTX = P0_2,

USBRX = P0_3,

//from here mbeDshield mod

D0=p27,

D1=p28,

D2=p14,

D3=p13,

#ifdef MBEDSHIELD_050

MOSI_=p11,

MISO_=p12,

SCK_=p13,

D4=p21,

D5=p22,

#else

D4=p12,

D5=p11,

#endif

D6=p23,

D7=p24,

D8=p25,

D9=p26,

D10=p8,

D11=p5,

D12=p6,

D13=p7,

A0=p15,

A1=p16,

A2=p17,

A3=p18,

A4=p19,

A5=p20,

SDA=p9,

SCL=p10,

//mbeDshield mod ends here

// Not connected

NC = (int)0xFFFFFFFF

Diff: TARGET_LPC2368/vector_defns.h

- Revision:

- 66:9c8f0e3462fb

- Parent:

- 65:5798e58a58b1

--- a/TARGET_LPC2368/vector_defns.h Mon Aug 12 13:17:46 2013 +0300 +++ b/TARGET_LPC2368/vector_defns.h Mon Aug 19 13:34:54 2013 +0300 @@ -1,77 +1,77 @@ -/* mbed Microcontroller Library - Vectors - * Copyright (c) 2006-2009 ARM Limited. All rights reserved. - */ - -#ifndef MBED_VECTOR_DEFNS_H -#define MBED_VECTOR_DEFNS_H - -// Assember Macros -#ifdef __ARMCC_VERSION -#define EXPORT(x) EXPORT x -#define WEAK_EXPORT(x) EXPORT x [WEAK] -#define IMPORT(x) IMPORT x -#define LABEL(x) x -#else -#define EXPORT(x) .global x -#define WEAK_EXPORT(x) .weak x -#define IMPORT(x) .global x -#define LABEL(x) x: -#endif - -// RealMonitor -// Requires RAM (0x40000040-0x4000011F) to be allocated by the linker - -// RealMonitor entry points -#define rm_init_entry 0x7fffff91 -#define rm_undef_handler 0x7fffffa0 -#define rm_prefetchabort_handler 0x7fffffb0 -#define rm_dataabort_handler 0x7fffffc0 -#define rm_irqhandler2 0x7fffffe0 -//#define rm_RunningToStopped 0x7ffff808 // ARM - MBED64 -#define rm_RunningToStopped 0x7ffff820 // ARM - PHAT40 - -// Unofficial RealMonitor entry points and variables -#define RM_MSG_SWI 0x00940000 -#define StateP 0x40000040 - -// VIC register addresses -#define VIC_Base 0xfffff000 -#define VICAddress_Offset 0xf00 -#define VICVectAddr0_Offset 0x100 -#define VICVectAddr2_Offset 0x108 -#define VICVectAddr3_Offset 0x10c -#define VICVectAddr31_Offset 0x17c -#define VICIntEnClr_Offset 0x014 -#define VICIntEnClr (*(volatile unsigned long *)(VIC_Base + 0x014)) -#define VICVectAddr2 (*(volatile unsigned long *)(VIC_Base + 0x108)) -#define VICVectAddr3 (*(volatile unsigned long *)(VIC_Base + 0x10C)) - -// ARM Mode bits and Interrupt flags in PSRs -#define Mode_USR 0x10 -#define Mode_FIQ 0x11 -#define Mode_IRQ 0x12 -#define Mode_SVC 0x13 -#define Mode_ABT 0x17 -#define Mode_UND 0x1B -#define Mode_SYS 0x1F -#define I_Bit 0x80 // when I bit is set, IRQ is disabled -#define F_Bit 0x40 // when F bit is set, FIQ is disabled - -// MCU RAM -#define LPC2368_RAM_ADDRESS 0x40000000 // RAM Base -#define LPC2368_RAM_SIZE 0x8000 // 32KB - -// ISR Stack Allocation -#define UND_stack_size 0x00000040 -#define SVC_stack_size 0x00000040 -#define ABT_stack_size 0x00000040 -#define FIQ_stack_size 0x00000000 -#define IRQ_stack_size 0x00000040 - -#define ISR_stack_size (UND_stack_size + SVC_stack_size + ABT_stack_size + FIQ_stack_size + IRQ_stack_size) - -// Full Descending Stack, so top-most stack points to just above the top of RAM -#define LPC2368_STACK_TOP (LPC2368_RAM_ADDRESS + LPC2368_RAM_SIZE) -#define USR_STACK_TOP (LPC2368_STACK_TOP - ISR_stack_size) - -#endif +/* mbed Microcontroller Library - Vectors + * Copyright (c) 2006-2009 ARM Limited. All rights reserved. + */ + +#ifndef MBED_VECTOR_DEFNS_H +#define MBED_VECTOR_DEFNS_H + +// Assember Macros +#ifdef __ARMCC_VERSION +#define EXPORT(x) EXPORT x +#define WEAK_EXPORT(x) EXPORT x [WEAK] +#define IMPORT(x) IMPORT x +#define LABEL(x) x +#else +#define EXPORT(x) .global x +#define WEAK_EXPORT(x) .weak x +#define IMPORT(x) .global x +#define LABEL(x) x: +#endif + +// RealMonitor +// Requires RAM (0x40000040-0x4000011F) to be allocated by the linker + +// RealMonitor entry points +#define rm_init_entry 0x7fffff91 +#define rm_undef_handler 0x7fffffa0 +#define rm_prefetchabort_handler 0x7fffffb0 +#define rm_dataabort_handler 0x7fffffc0 +#define rm_irqhandler2 0x7fffffe0 +//#define rm_RunningToStopped 0x7ffff808 // ARM - MBED64 +#define rm_RunningToStopped 0x7ffff820 // ARM - PHAT40 + +// Unofficial RealMonitor entry points and variables +#define RM_MSG_SWI 0x00940000 +#define StateP 0x40000040 + +// VIC register addresses +#define VIC_Base 0xfffff000 +#define VICAddress_Offset 0xf00 +#define VICVectAddr0_Offset 0x100 +#define VICVectAddr2_Offset 0x108 +#define VICVectAddr3_Offset 0x10c +#define VICVectAddr31_Offset 0x17c +#define VICIntEnClr_Offset 0x014 +#define VICIntEnClr (*(volatile unsigned long *)(VIC_Base + 0x014)) +#define VICVectAddr2 (*(volatile unsigned long *)(VIC_Base + 0x108)) +#define VICVectAddr3 (*(volatile unsigned long *)(VIC_Base + 0x10C)) + +// ARM Mode bits and Interrupt flags in PSRs +#define Mode_USR 0x10 +#define Mode_FIQ 0x11 +#define Mode_IRQ 0x12 +#define Mode_SVC 0x13 +#define Mode_ABT 0x17 +#define Mode_UND 0x1B +#define Mode_SYS 0x1F +#define I_Bit 0x80 // when I bit is set, IRQ is disabled +#define F_Bit 0x40 // when F bit is set, FIQ is disabled + +// MCU RAM +#define LPC2368_RAM_ADDRESS 0x40000000 // RAM Base +#define LPC2368_RAM_SIZE 0x8000 // 32KB + +// ISR Stack Allocation +#define UND_stack_size 0x00000040 +#define SVC_stack_size 0x00000040 +#define ABT_stack_size 0x00000040 +#define FIQ_stack_size 0x00000000 +#define IRQ_stack_size 0x00000040 + +#define ISR_stack_size (UND_stack_size + SVC_stack_size + ABT_stack_size + FIQ_stack_size + IRQ_stack_size) + +// Full Descending Stack, so top-most stack points to just above the top of RAM +#define LPC2368_STACK_TOP (LPC2368_RAM_ADDRESS + LPC2368_RAM_SIZE) +#define USR_STACK_TOP (LPC2368_STACK_TOP - ISR_stack_size) + +#endif