3.5" inch TFT LCD Display Module 480X320 driven with FSMC.

TFT LCD Display Module 480X320 driven with FSMC

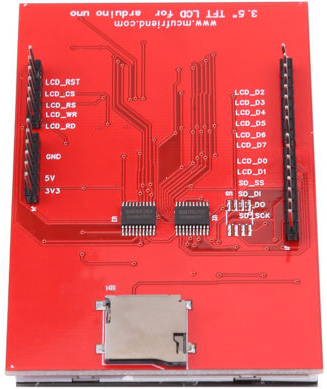

I have recently bought a 3.5" inch TFT LCD Touch Screen Display Module 480X320 with a www.mcufriend.com label on the back side. The display was equipped with an 8bit parallel interface. First I decided to test it with the UniGraphic library using the BUS_8 protocol. The display was very slow but improved when I switched to the PAR_8 protocol. Because I heard about the possibility to use a Flexible Static Memory Controller (FSMC), built into some STM MCU's, to drive LCD's (read/write to LCD's memory rather than to an external SRAM) I thought it would be a fun to try it out.

Below is the brief story of what I did:

- Created a project for my STM32F407VE board in the STM32CubeIDE

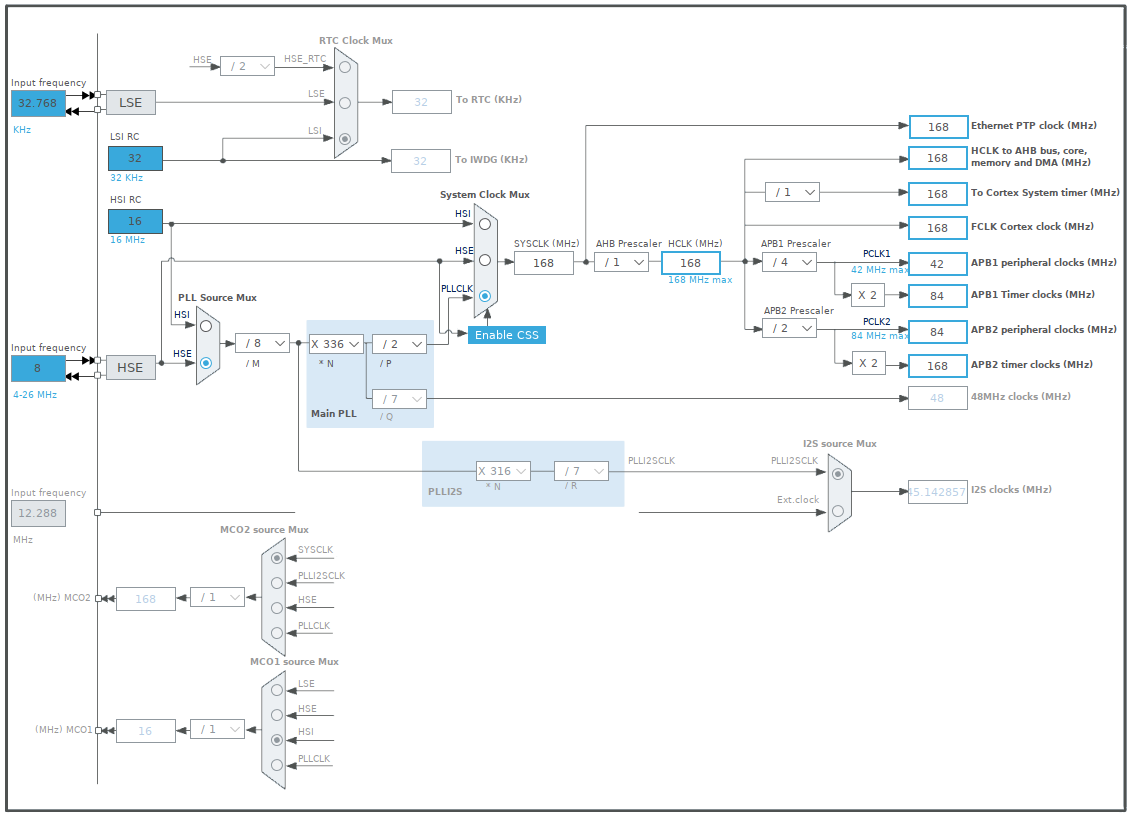

- Set the

Clock Configurationto match the one used by Mbed for the Seeed Arch Max board:

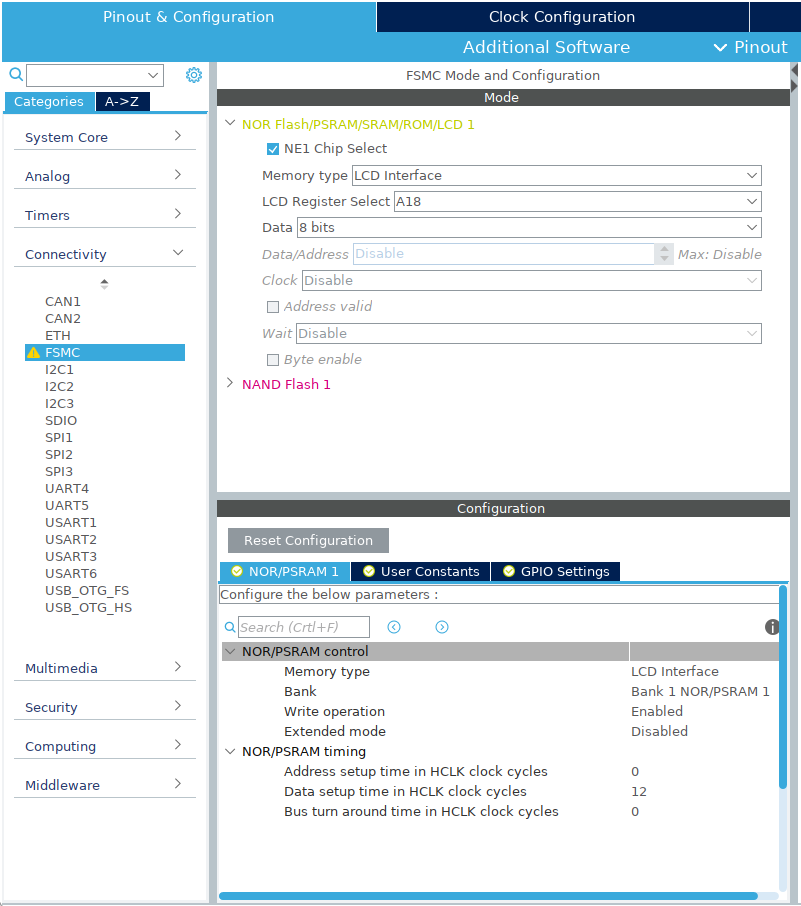

- Selected

FSMCin theConnectivitycategory and configured it as below:

- Let the

STM32CubeIDEgenerate the code (files). - Created a new program for the Seeed Arch Max target in the Mbed Online Compiler by selecting a

mbed os blinkytemplate. - Replaced the

main.cppwith themain.ccontent of theSTM32CubeIDEproject. Copy & Pastedthe other files with codes from theSTM32CubeIDEproject to the online compiler project.- Renamed and modified:

"stm32f4xx_it.h" to "stm32f4xx_it_msp.h"

"stm32f4xx_it.c" to "stm32f4xx_it_msp.c" - Added the UniGraphic library to the online compiler project.

- Extended the

UniGraphiclibrary with aFSMC_8protocol and replaced theTFT::set_orientation(int orient)function with the one used bymcufriendfor arduino. - Modified the

main.cppas needed.

|  |

Wiring

| STM32F407VE | TFT LCD module |

|---|---|

| +3.3V | 3V3 |

| GND | GND |

| PB_12 | LCD_RST |

| GND | LCD_CS |

| PD_13 (RS) | LCD_RS |

| PD_5 (WR) | LCD_WR |

| PD_4 (RD) | LCD_RD |

| PD_14 (DB00) | LCD_D0 |

| PD_15 (DB01) | LCD_D1 |

| PD_0 (DB02) | LCD_D2 |

| PD_1 (DB03) | LCD_D3 |

| PE_7 (DB04) | LCD_D4 |

| PE_8 (DB05) | LCD_D5 |

| PE_9 (DB06) | LCD_D6 |

| PE_10 (DB07) | LCD_D7 |

Results

| Execution times | ||

|---|---|---|

| Used protocol | BUS_8 | FSMC_8 |

| Operation \ Time | ms | ms |

| Clear | 2283.980 | 38.454 |

| Plot | 192.066 | 11.365 |

| 8bit BMP | 63.805 | 41.338 |

| Large Font | 163.872 | 7.895 |

| Sparce pixels | 2072.265/1458.051 | 74.107/52.168 |

| 16bit BMP | 2288.589 | 59.904 |

Diff: UniGraphic/Inits/S6D04D1.cpp

- Revision:

- 0:fa952828e34c

diff -r 000000000000 -r fa952828e34c UniGraphic/Inits/S6D04D1.cpp

--- /dev/null Thu Jan 01 00:00:00 1970 +0000

+++ b/UniGraphic/Inits/S6D04D1.cpp Sun May 10 10:44:31 2020 +0000

@@ -0,0 +1,260 @@

+ /* mbed UniGraphic library - Device specific class

+ * Copyright (c) 2015 Giuliano Dianda

+ * Released under the MIT License: http://mbed.org/license/mit

+ */

+#include "Protocols.h"

+#include "S6D04D1.h"

+

+//////////////////////////////////////////////////////////////////////////////////

+// display settings ///////////////////////////////////////////////////////

+/////////////////////////////////////////////////////////////////////////

+

+// put in constructor

+//#define LCDSIZE_X 240 // display X pixels, TFTs are usually portrait view

+//#define LCDSIZE_Y 400 // display Y pixels

+

+

+

+S6D04D1::S6D04D1(proto_t displayproto, PortName port, PinName CS, PinName reset, PinName DC, PinName WR, PinName RD, const char *name , unsigned int LCDSIZE_X, unsigned int LCDSIZE_Y)

+ : TFT(displayproto, port, CS, reset, DC, WR, RD, LCDSIZE_X, LCDSIZE_Y, name)

+{

+ hw_reset();

+ BusEnable(true);

+ identify(); // will collect tftID, set mipistd flag

+ init();

+ auto_gram_read_format();// try to get read gram pixel format, could be 16bit or 18bit, RGB or BGR. Will set flags accordingly

+// scrollbugfix=1; // when scrolling 1 line, the last line disappears, set to 1 to fix it, for ili9481 is set automatically in identify()

+ set_orientation(0);

+ FastWindow(true); // most but not all controllers support this, even if datasheet tells they should. Give a try

+ cls();

+ locate(0,0);

+}

+S6D04D1::S6D04D1(proto_t displayproto, PinName* buspins, PinName CS, PinName reset, PinName DC, PinName WR, PinName RD, const char *name , unsigned int LCDSIZE_X, unsigned int LCDSIZE_Y)

+ : TFT(displayproto, buspins, CS, reset, DC, WR, RD, LCDSIZE_X, LCDSIZE_Y, name)

+{

+ hw_reset();

+ BusEnable(true);

+ identify(); // will collect tftID, set mipistd flag

+ init();

+ auto_gram_read_format();// try to get read gram pixel format, could be 16bit or 18bit, RGB or BGR. Will set flags accordingly

+// scrollbugfix=1; // when scrolling 1 line, the last line disappears, set to 1 to fix it, for ili9481 is set automatically in identify()

+ set_orientation(0);

+ FastWindow(true); // most but not all controllers support this, even if datasheet tells they should. Give a try

+ cls();

+ locate(0,0);

+}

+S6D04D1::S6D04D1(proto_t displayproto, int Hz, PinName mosi, PinName miso, PinName sclk, PinName CS, PinName reset, PinName DC, const char *name , unsigned int LCDSIZE_X , unsigned int LCDSIZE_Y )

+ : TFT(displayproto, Hz, mosi, miso, sclk, CS, reset, DC, LCDSIZE_X, LCDSIZE_Y, name)

+{

+ hw_reset(); //TFT class forwards to Protocol class

+ BusEnable(true); //TFT class forwards to Protocol class

+ identify(); // will collect tftID and set mipistd flag

+ init(); // per display custom init cmd sequence, implemented here

+ auto_gram_read_format();// try to get read gram pixel format, could be 16bit or 18bit, RGB or BGR. Will set flags accordingly

+ // scrollbugfix=1; // when scrolling 1 line, the last line disappears, set to 1 to fix it, for ili9481 is set automatically in identify()

+ set_orientation(0); //TFT class does for MIPI standard and some ILIxxx

+ FastWindow(true); // most but not all controllers support this, even if datasheet tells they should. Give a try

+ cls();

+ locate(0,0);

+}

+// reset and init the lcd controller

+void S6D04D1::init()

+{

+ /**********************************************

+ TFT1P CODE Initialization of Truly

+

+ ************************************************

+ Panel:3.0 240400

+ Driver IC:S6D04D1X21-BAF8

+

+ ************************************************/

+wr_cmd8(0xE0);

+wr_data8(0x01);

+

+wr_cmd8(0x11);

+wait_ms(150);

+

+wr_cmd8(0xF3);

+wr_data8(0x01);

+wr_data8(0x00);

+wr_data8(0x00);

+wr_data8(0x0C);//Do not set any higher VCI1 level than VCI -0.15V. 0C 0A

+wr_data8(0x03);//VGH和VGL 01 02VGH=6VCI1,VGL=-4VCI1.

+wr_data8(0x75);

+wr_data8(0x75);

+wr_data8(0x30);

+

+wr_cmd8(0xF4);

+wr_data8(0x4C);

+wr_data8(0x4C);

+wr_data8(0x44);

+wr_data8(0x44);

+wr_data8(0x22);

+

+wr_cmd8(0xF5);

+wr_data8(0x10);

+wr_data8(0x22);

+wr_data8(0x05);

+wr_data8(0xF0);

+wr_data8(0x70);

+wr_data8(0x1F);

+wait_ms(30);

+

+wr_cmd8(0xF3);

+wr_data8(0x03);

+wait_ms(30);

+wr_cmd8(0xF3);

+wr_data8(0x07);

+wait_ms(30);

+wr_cmd8(0xF3);

+wr_data8(0x0F);

+wait_ms(30);

+wr_cmd8(0xF3);

+wr_data8(0x1F);

+wait_ms(30);

+wr_cmd8(0xF3);

+wr_data8(0x7F);

+wait_ms(30);

+

+

+wr_cmd8(0xF7);

+wr_data8(0x80);

+wr_data8(0x00);

+wr_data8(0x00);

+wr_data8(0x05);

+wr_data8(0x0D);

+wr_data8(0x1F);

+wr_data8(0x26);

+wr_data8(0x2D);

+wr_data8(0x14);

+wr_data8(0x15);

+wr_data8(0x26);

+wr_data8(0x20);

+wr_data8(0x01);

+wr_data8(0x22);

+wr_data8(0x22);

+

+wr_cmd8(0xF8);

+wr_data8(0x80);

+wr_data8(0x00);

+wr_data8(0x00);

+wr_data8(0x00);

+wr_data8(0x07);

+wr_data8(0x1E);

+wr_data8(0x2A);

+wr_data8(0x32);

+wr_data8(0x10);

+wr_data8(0x16);

+wr_data8(0x36);

+wr_data8(0x3C);

+wr_data8(0x3B);

+wr_data8(0x22);

+wr_data8(0x22);

+

+wr_cmd8(0xF9);

+wr_data8(0x80);

+wr_data8(0x00);

+wr_data8(0x00);

+wr_data8(0x05);

+wr_data8(0x0D);

+wr_data8(0x1F);

+wr_data8(0x26);

+wr_data8(0x2D);

+wr_data8(0x14);

+wr_data8(0x15);

+wr_data8(0x26);

+wr_data8(0x20);

+wr_data8(0x01);

+wr_data8(0x22);

+wr_data8(0x22);

+

+

+wr_cmd8(0xFA);

+wr_data8(0x80);

+wr_data8(0x00);

+wr_data8(0x00);

+wr_data8(0x00);

+wr_data8(0x07);

+wr_data8(0x1E);

+wr_data8(0x2A);

+wr_data8(0x32);

+wr_data8(0x10);

+wr_data8(0x16);

+wr_data8(0x36);

+wr_data8(0x3C);

+wr_data8(0x3B);

+wr_data8(0x22);

+wr_data8(0x22);

+

+

+wr_cmd8(0xFB);

+wr_data8(0x80);

+wr_data8(0x00);

+wr_data8(0x00);

+wr_data8(0x05);

+wr_data8(0x0D);

+wr_data8(0x1F);

+wr_data8(0x26);

+wr_data8(0x2D);

+wr_data8(0x14);

+wr_data8(0x15);

+wr_data8(0x26);

+wr_data8(0x20);

+wr_data8(0x01);

+wr_data8(0x22);

+wr_data8(0x22);

+

+wr_cmd8(0xFC);

+wr_data8(0x80);

+wr_data8(0x00);

+wr_data8(0x00);

+wr_data8(0x00);

+wr_data8(0x07);

+wr_data8(0x1E);

+wr_data8(0x2A);

+wr_data8(0x32);

+wr_data8(0x10);

+wr_data8(0x16);

+wr_data8(0x36);

+wr_data8(0x3C);

+wr_data8(0x3B);

+wr_data8(0x22);

+wr_data8(0x22);

+

+//wr_cmd8(0x35);

+wr_cmd8(0x34); // tearing effect line off

+

+wr_cmd8(0x36);

+wr_data8(0x48);//08

+

+wr_cmd8(0x3A);

+wr_data8(0x05);

+

+wr_cmd8(0xF2);

+wr_data8(0x17);

+wr_data8(0x17);

+wr_data8(0x0F);

+wr_data8(0x08);

+wr_data8(0x08);

+wr_data8(0x00);

+wr_data8(0x00);

+wr_data8(0x00);

+wr_data8(0x00);

+wr_data8(0x13);

+wr_data8(0x00);

+

+wr_cmd8(0xF6);

+wr_data8(0x00);

+wr_data8(0x08);

+wr_data8(0x00);

+wr_data8(0x00);

+

+wr_cmd8(0xFD);

+wr_data8(0x02);

+wr_data8(0x01);//240*400

+

+wait_ms(20);

+wr_cmd8(0x29); // display on

+wait_ms(20);

+

+}