3.5" inch TFT LCD Display Module 480X320 driven with FSMC.

TFT LCD Display Module 480X320 driven with FSMC

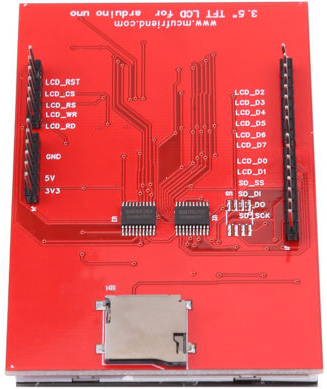

I have recently bought a 3.5" inch TFT LCD Touch Screen Display Module 480X320 with a www.mcufriend.com label on the back side. The display was equipped with an 8bit parallel interface. First I decided to test it with the UniGraphic library using the BUS_8 protocol. The display was very slow but improved when I switched to the PAR_8 protocol. Because I heard about the possibility to use a Flexible Static Memory Controller (FSMC), built into some STM MCU's, to drive LCD's (read/write to LCD's memory rather than to an external SRAM) I thought it would be a fun to try it out.

Below is the brief story of what I did:

- Created a project for my STM32F407VE board in the STM32CubeIDE

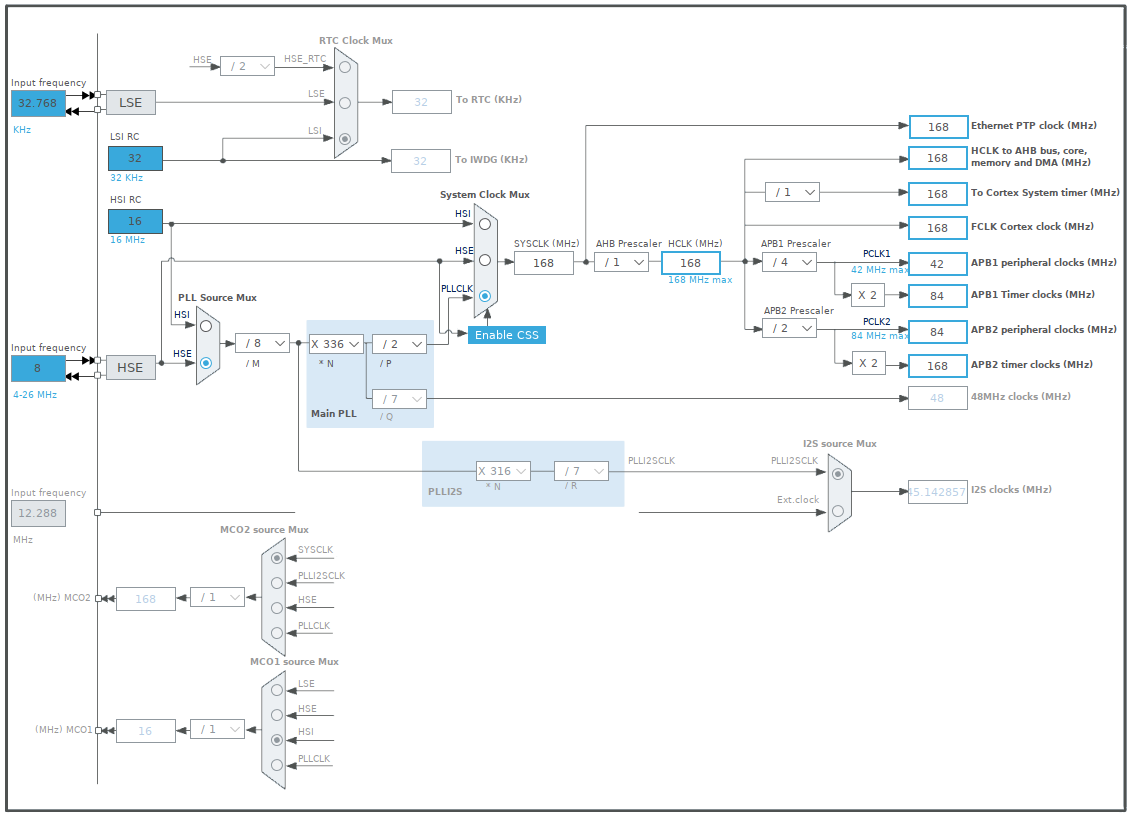

- Set the

Clock Configurationto match the one used by Mbed for the Seeed Arch Max board:

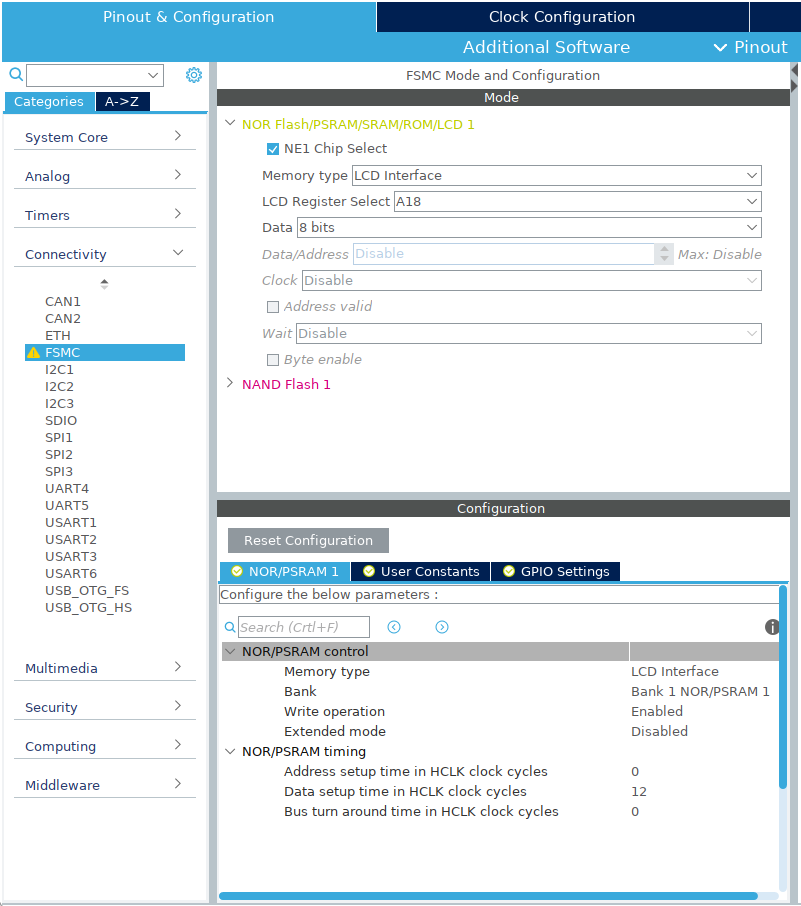

- Selected

FSMCin theConnectivitycategory and configured it as below:

- Let the

STM32CubeIDEgenerate the code (files). - Created a new program for the Seeed Arch Max target in the Mbed Online Compiler by selecting a

mbed os blinkytemplate. - Replaced the

main.cppwith themain.ccontent of theSTM32CubeIDEproject. Copy & Pastedthe other files with codes from theSTM32CubeIDEproject to the online compiler project.- Renamed and modified:

"stm32f4xx_it.h" to "stm32f4xx_it_msp.h"

"stm32f4xx_it.c" to "stm32f4xx_it_msp.c" - Added the UniGraphic library to the online compiler project.

- Extended the

UniGraphiclibrary with aFSMC_8protocol and replaced theTFT::set_orientation(int orient)function with the one used bymcufriendfor arduino. - Modified the

main.cppas needed.

|  |

Wiring

| STM32F407VE | TFT LCD module |

|---|---|

| +3.3V | 3V3 |

| GND | GND |

| PB_12 | LCD_RST |

| GND | LCD_CS |

| PD_13 (RS) | LCD_RS |

| PD_5 (WR) | LCD_WR |

| PD_4 (RD) | LCD_RD |

| PD_14 (DB00) | LCD_D0 |

| PD_15 (DB01) | LCD_D1 |

| PD_0 (DB02) | LCD_D2 |

| PD_1 (DB03) | LCD_D3 |

| PE_7 (DB04) | LCD_D4 |

| PE_8 (DB05) | LCD_D5 |

| PE_9 (DB06) | LCD_D6 |

| PE_10 (DB07) | LCD_D7 |

Results

| Execution times | ||

|---|---|---|

| Used protocol | BUS_8 | FSMC_8 |

| Operation \ Time | ms | ms |

| Clear | 2283.980 | 38.454 |

| Plot | 192.066 | 11.365 |

| 8bit BMP | 63.805 | 41.338 |

| Large Font | 163.872 | 7.895 |

| Sparce pixels | 2072.265/1458.051 | 74.107/52.168 |

| 16bit BMP | 2288.589 | 59.904 |

UniGraphic/Protocols/BUS16.cpp@1:47c996032a9e, 2020-09-25 (annotated)

- Committer:

- hudakz

- Date:

- Fri Sep 25 14:52:27 2020 +0000

- Revision:

- 1:47c996032a9e

- Parent:

- 0:fa952828e34c

3.5" inch TFT LCD Display Module 480X320 driven with FSMC.

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| hudakz | 0:fa952828e34c | 1 | /* mbed UniGraphic library - BUS16 protocol class |

| hudakz | 0:fa952828e34c | 2 | * Copyright (c) 2015 Giuliano Dianda |

| hudakz | 0:fa952828e34c | 3 | * Released under the MIT License: http://mbed.org/license/mit |

| hudakz | 0:fa952828e34c | 4 | * |

| hudakz | 0:fa952828e34c | 5 | * Derived work of: |

| hudakz | 0:fa952828e34c | 6 | * |

| hudakz | 0:fa952828e34c | 7 | * mbed library for 240*320 pixel display TFT based on ILI9341 LCD Controller |

| hudakz | 0:fa952828e34c | 8 | * Copyright (c) 2013 Peter Drescher - DC2PD |

| hudakz | 0:fa952828e34c | 9 | * |

| hudakz | 0:fa952828e34c | 10 | * THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR |

| hudakz | 0:fa952828e34c | 11 | * IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, |

| hudakz | 0:fa952828e34c | 12 | * FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE |

| hudakz | 0:fa952828e34c | 13 | * AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER |

| hudakz | 0:fa952828e34c | 14 | * LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, |

| hudakz | 0:fa952828e34c | 15 | * OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN |

| hudakz | 0:fa952828e34c | 16 | * THE SOFTWARE. |

| hudakz | 0:fa952828e34c | 17 | */ |

| hudakz | 0:fa952828e34c | 18 | #include "BUS16.h" |

| hudakz | 0:fa952828e34c | 19 | |

| hudakz | 0:fa952828e34c | 20 | BUS16::BUS16(PinName* buspins, PinName CS, PinName reset, PinName DC, PinName WR, PinName RD) |

| hudakz | 0:fa952828e34c | 21 | : _bus(buspins), _CS(CS), _reset(reset), _DC(DC), _WR(WR), _RD(RD) |

| hudakz | 0:fa952828e34c | 22 | { |

| hudakz | 0:fa952828e34c | 23 | _reset = 1; |

| hudakz | 0:fa952828e34c | 24 | _DC=1; |

| hudakz | 0:fa952828e34c | 25 | _WR=1; |

| hudakz | 0:fa952828e34c | 26 | _RD=1; |

| hudakz | 0:fa952828e34c | 27 | _CS=1; |

| hudakz | 0:fa952828e34c | 28 | _bus.mode(PullNone); |

| hudakz | 0:fa952828e34c | 29 | _bus.output(); // will re-enable our GPIO port |

| hudakz | 0:fa952828e34c | 30 | hw_reset(); |

| hudakz | 0:fa952828e34c | 31 | } |

| hudakz | 0:fa952828e34c | 32 | |

| hudakz | 0:fa952828e34c | 33 | void BUS16::wr_cmd8(unsigned char cmd) |

| hudakz | 0:fa952828e34c | 34 | { |

| hudakz | 0:fa952828e34c | 35 | _DC = 0; // 0=cmd |

| hudakz | 0:fa952828e34c | 36 | _bus.write(cmd); // write 8bit |

| hudakz | 0:fa952828e34c | 37 | _WR=0; |

| hudakz | 0:fa952828e34c | 38 | _WR=1; |

| hudakz | 0:fa952828e34c | 39 | _DC = 1; // 1=data next |

| hudakz | 0:fa952828e34c | 40 | } |

| hudakz | 0:fa952828e34c | 41 | void BUS16::wr_data8(unsigned char data) |

| hudakz | 0:fa952828e34c | 42 | { |

| hudakz | 0:fa952828e34c | 43 | _bus.write(data); // write 8bit |

| hudakz | 0:fa952828e34c | 44 | _WR=0; |

| hudakz | 0:fa952828e34c | 45 | _WR=1; |

| hudakz | 0:fa952828e34c | 46 | } |

| hudakz | 0:fa952828e34c | 47 | void BUS16::wr_cmd16(unsigned short cmd) |

| hudakz | 0:fa952828e34c | 48 | { |

| hudakz | 0:fa952828e34c | 49 | _DC = 0; // 0=cmd |

| hudakz | 0:fa952828e34c | 50 | _bus.write(cmd>>8); // write 8bit |

| hudakz | 0:fa952828e34c | 51 | _WR=0; |

| hudakz | 0:fa952828e34c | 52 | _WR=1; |

| hudakz | 0:fa952828e34c | 53 | _bus.write(cmd&0xFF); // write 8bit |

| hudakz | 0:fa952828e34c | 54 | _WR=0; |

| hudakz | 0:fa952828e34c | 55 | _WR=1; |

| hudakz | 0:fa952828e34c | 56 | _DC = 1; // 1=data next |

| hudakz | 0:fa952828e34c | 57 | } |

| hudakz | 0:fa952828e34c | 58 | void BUS16::wr_data16(unsigned short data) |

| hudakz | 0:fa952828e34c | 59 | { |

| hudakz | 0:fa952828e34c | 60 | _bus.write(data>>8); // write 8bit |

| hudakz | 0:fa952828e34c | 61 | _WR=0; |

| hudakz | 0:fa952828e34c | 62 | _WR=1; |

| hudakz | 0:fa952828e34c | 63 | _bus.write(data&0xFF); // write 8bit |

| hudakz | 0:fa952828e34c | 64 | _WR=0; |

| hudakz | 0:fa952828e34c | 65 | _WR=1; |

| hudakz | 0:fa952828e34c | 66 | } |

| hudakz | 0:fa952828e34c | 67 | void BUS16::wr_gram(unsigned short data) |

| hudakz | 0:fa952828e34c | 68 | { |

| hudakz | 0:fa952828e34c | 69 | _bus.write(data); // write 16bit |

| hudakz | 0:fa952828e34c | 70 | _WR=0; |

| hudakz | 0:fa952828e34c | 71 | _WR=1; |

| hudakz | 0:fa952828e34c | 72 | } |

| hudakz | 0:fa952828e34c | 73 | void BUS16::wr_gram(unsigned short data, unsigned int count) |

| hudakz | 0:fa952828e34c | 74 | { |

| hudakz | 0:fa952828e34c | 75 | while(count) |

| hudakz | 0:fa952828e34c | 76 | { |

| hudakz | 0:fa952828e34c | 77 | _bus.write(data); // rewrite even if same data, otherwise too much fast |

| hudakz | 0:fa952828e34c | 78 | _WR=0; |

| hudakz | 0:fa952828e34c | 79 | _WR=1; |

| hudakz | 0:fa952828e34c | 80 | count--; |

| hudakz | 0:fa952828e34c | 81 | } |

| hudakz | 0:fa952828e34c | 82 | } |

| hudakz | 0:fa952828e34c | 83 | void BUS16::wr_grambuf(unsigned short* data, unsigned int lenght) |

| hudakz | 0:fa952828e34c | 84 | { |

| hudakz | 0:fa952828e34c | 85 | while(lenght) |

| hudakz | 0:fa952828e34c | 86 | { |

| hudakz | 0:fa952828e34c | 87 | _bus.write(*data); // write 16bit |

| hudakz | 0:fa952828e34c | 88 | _WR=0; |

| hudakz | 0:fa952828e34c | 89 | _WR=1; |

| hudakz | 0:fa952828e34c | 90 | data++; |

| hudakz | 0:fa952828e34c | 91 | lenght--; |

| hudakz | 0:fa952828e34c | 92 | } |

| hudakz | 0:fa952828e34c | 93 | } |

| hudakz | 0:fa952828e34c | 94 | unsigned short BUS16::rd_gram(bool convert) |

| hudakz | 0:fa952828e34c | 95 | { |

| hudakz | 0:fa952828e34c | 96 | unsigned int r=0; |

| hudakz | 0:fa952828e34c | 97 | _bus.input(); |

| hudakz | 0:fa952828e34c | 98 | |

| hudakz | 0:fa952828e34c | 99 | _RD = 0; |

| hudakz | 0:fa952828e34c | 100 | _bus.read(); //dummy read |

| hudakz | 0:fa952828e34c | 101 | _RD = 1; |

| hudakz | 0:fa952828e34c | 102 | |

| hudakz | 0:fa952828e34c | 103 | _RD = 0; |

| hudakz | 0:fa952828e34c | 104 | // _RD = 0; // add wait |

| hudakz | 0:fa952828e34c | 105 | r |= _bus.read(); |

| hudakz | 0:fa952828e34c | 106 | _RD = 1; |

| hudakz | 0:fa952828e34c | 107 | if(convert) |

| hudakz | 0:fa952828e34c | 108 | { |

| hudakz | 0:fa952828e34c | 109 | r <<= 8; |

| hudakz | 0:fa952828e34c | 110 | _RD = 0; |

| hudakz | 0:fa952828e34c | 111 | // _RD = 0; // add wait |

| hudakz | 0:fa952828e34c | 112 | r |= _bus.read()>>8; //MSB of port read is blue, LSB is red of next pixel |

| hudakz | 0:fa952828e34c | 113 | _RD = 1; |

| hudakz | 0:fa952828e34c | 114 | // gram is 18bit/pixel, if you set 16bit/pixel (cmd 3A), during writing the 16bits are expanded to 18bit |

| hudakz | 0:fa952828e34c | 115 | // during reading, you read the raw 18bit gram |

| hudakz | 0:fa952828e34c | 116 | r = RGB24to16((r&0xFF0000)>>16, (r&0xFF00)>>8, r&0xFF);// 18bit pixel padded to 24bits, rrrrrr00_gggggg00_bbbbbb00, converted to 16bit |

| hudakz | 0:fa952828e34c | 117 | } |

| hudakz | 0:fa952828e34c | 118 | _bus.output(); |

| hudakz | 0:fa952828e34c | 119 | return (unsigned short)r; |

| hudakz | 0:fa952828e34c | 120 | } |

| hudakz | 0:fa952828e34c | 121 | unsigned int BUS16::rd_reg_data32(unsigned char reg) |

| hudakz | 0:fa952828e34c | 122 | { |

| hudakz | 0:fa952828e34c | 123 | wr_cmd8(reg); |

| hudakz | 0:fa952828e34c | 124 | unsigned int r=0; |

| hudakz | 0:fa952828e34c | 125 | // _DC = 1; // 1=data |

| hudakz | 0:fa952828e34c | 126 | _bus.input(); |

| hudakz | 0:fa952828e34c | 127 | |

| hudakz | 0:fa952828e34c | 128 | _RD = 0; |

| hudakz | 0:fa952828e34c | 129 | _bus.read(); //dummy read |

| hudakz | 0:fa952828e34c | 130 | _RD = 1; |

| hudakz | 0:fa952828e34c | 131 | |

| hudakz | 0:fa952828e34c | 132 | _RD = 0; |

| hudakz | 0:fa952828e34c | 133 | // _RD = 0; // add wait |

| hudakz | 0:fa952828e34c | 134 | r |= (_bus.read()&0xFF); |

| hudakz | 0:fa952828e34c | 135 | r <<= 8; |

| hudakz | 0:fa952828e34c | 136 | _RD = 1; |

| hudakz | 0:fa952828e34c | 137 | |

| hudakz | 0:fa952828e34c | 138 | _RD = 0; |

| hudakz | 0:fa952828e34c | 139 | // _RD = 0; // add wait |

| hudakz | 0:fa952828e34c | 140 | r |= (_bus.read()&0xFF); |

| hudakz | 0:fa952828e34c | 141 | r <<= 8; |

| hudakz | 0:fa952828e34c | 142 | _RD = 1; |

| hudakz | 0:fa952828e34c | 143 | |

| hudakz | 0:fa952828e34c | 144 | _RD = 0; |

| hudakz | 0:fa952828e34c | 145 | // _RD = 0; // add wait |

| hudakz | 0:fa952828e34c | 146 | r |= (_bus.read()&0xFF); |

| hudakz | 0:fa952828e34c | 147 | r <<= 8; |

| hudakz | 0:fa952828e34c | 148 | _RD = 1; |

| hudakz | 0:fa952828e34c | 149 | |

| hudakz | 0:fa952828e34c | 150 | _RD = 0; |

| hudakz | 0:fa952828e34c | 151 | // _RD = 0; // add wait |

| hudakz | 0:fa952828e34c | 152 | r |= (_bus.read()&0xFF); |

| hudakz | 0:fa952828e34c | 153 | _RD = 1; |

| hudakz | 0:fa952828e34c | 154 | |

| hudakz | 0:fa952828e34c | 155 | _CS = 1; // toggle CS to interupt the cmd in case was not supported |

| hudakz | 0:fa952828e34c | 156 | _CS = 0; |

| hudakz | 0:fa952828e34c | 157 | |

| hudakz | 0:fa952828e34c | 158 | _bus.output(); |

| hudakz | 0:fa952828e34c | 159 | return r; |

| hudakz | 0:fa952828e34c | 160 | } |

| hudakz | 0:fa952828e34c | 161 | // in Par mode EXTC regs (0xB0-0xFF) can be directly read |

| hudakz | 0:fa952828e34c | 162 | unsigned int BUS16::rd_extcreg_data32(unsigned char reg, unsigned char SPIreadenablecmd) |

| hudakz | 0:fa952828e34c | 163 | { |

| hudakz | 0:fa952828e34c | 164 | return rd_reg_data32(reg); |

| hudakz | 0:fa952828e34c | 165 | } |

| hudakz | 0:fa952828e34c | 166 | // ILI932x specific |

| hudakz | 0:fa952828e34c | 167 | void BUS16::dummyread() |

| hudakz | 0:fa952828e34c | 168 | { |

| hudakz | 0:fa952828e34c | 169 | _bus.input(); |

| hudakz | 0:fa952828e34c | 170 | _RD = 0; |

| hudakz | 0:fa952828e34c | 171 | _bus.read(); // dummy read |

| hudakz | 0:fa952828e34c | 172 | _RD=1; |

| hudakz | 0:fa952828e34c | 173 | // _bus.output(); |

| hudakz | 0:fa952828e34c | 174 | } |

| hudakz | 0:fa952828e34c | 175 | // ILI932x specific |

| hudakz | 0:fa952828e34c | 176 | void BUS16::reg_select(unsigned char reg, bool forread) |

| hudakz | 0:fa952828e34c | 177 | { |

| hudakz | 0:fa952828e34c | 178 | _DC = 0; |

| hudakz | 0:fa952828e34c | 179 | _bus.write(reg); // write 16bit |

| hudakz | 0:fa952828e34c | 180 | _WR=0; |

| hudakz | 0:fa952828e34c | 181 | _WR=1; |

| hudakz | 0:fa952828e34c | 182 | _DC = 1; // 1=data next |

| hudakz | 0:fa952828e34c | 183 | } |

| hudakz | 0:fa952828e34c | 184 | // ILI932x specific |

| hudakz | 0:fa952828e34c | 185 | void BUS16::reg_write(unsigned char reg, unsigned short data) |

| hudakz | 0:fa952828e34c | 186 | { |

| hudakz | 0:fa952828e34c | 187 | _DC = 0; |

| hudakz | 0:fa952828e34c | 188 | _bus.write(reg); // write 16bit |

| hudakz | 0:fa952828e34c | 189 | _WR=0; |

| hudakz | 0:fa952828e34c | 190 | _WR=1; |

| hudakz | 0:fa952828e34c | 191 | _DC = 1; |

| hudakz | 0:fa952828e34c | 192 | _bus.write(data); // write 16bit |

| hudakz | 0:fa952828e34c | 193 | _WR=0; |

| hudakz | 0:fa952828e34c | 194 | _WR=1; |

| hudakz | 0:fa952828e34c | 195 | } |

| hudakz | 0:fa952828e34c | 196 | // ILI932x specific |

| hudakz | 0:fa952828e34c | 197 | unsigned short BUS16::reg_read(unsigned char reg) |

| hudakz | 0:fa952828e34c | 198 | { |

| hudakz | 0:fa952828e34c | 199 | unsigned short r=0; |

| hudakz | 0:fa952828e34c | 200 | _DC = 0; |

| hudakz | 0:fa952828e34c | 201 | _bus.write(reg); // write 16bit |

| hudakz | 0:fa952828e34c | 202 | _WR=0; |

| hudakz | 0:fa952828e34c | 203 | _WR=1; |

| hudakz | 0:fa952828e34c | 204 | _DC = 1; |

| hudakz | 0:fa952828e34c | 205 | _bus.input(); |

| hudakz | 0:fa952828e34c | 206 | _RD=0; |

| hudakz | 0:fa952828e34c | 207 | r |= _bus.read(); // read 16bit |

| hudakz | 0:fa952828e34c | 208 | _RD=1; |

| hudakz | 0:fa952828e34c | 209 | _bus.output(); |

| hudakz | 0:fa952828e34c | 210 | return r; |

| hudakz | 0:fa952828e34c | 211 | } |

| hudakz | 0:fa952828e34c | 212 | void BUS16::hw_reset() |

| hudakz | 0:fa952828e34c | 213 | { |

| hudakz | 0:fa952828e34c | 214 | wait_ms(15); |

| hudakz | 0:fa952828e34c | 215 | _DC = 1; |

| hudakz | 0:fa952828e34c | 216 | _CS = 1; |

| hudakz | 0:fa952828e34c | 217 | _WR = 1; |

| hudakz | 0:fa952828e34c | 218 | _RD = 1; |

| hudakz | 0:fa952828e34c | 219 | _reset = 0; // display reset |

| hudakz | 0:fa952828e34c | 220 | wait_ms(2); |

| hudakz | 0:fa952828e34c | 221 | _reset = 1; // end reset |

| hudakz | 0:fa952828e34c | 222 | wait_ms(100); |

| hudakz | 0:fa952828e34c | 223 | } |

| hudakz | 0:fa952828e34c | 224 | void BUS16::BusEnable(bool enable) |

| hudakz | 0:fa952828e34c | 225 | { |

| hudakz | 0:fa952828e34c | 226 | _CS = enable ? 0:1; |

| hudakz | 0:fa952828e34c | 227 | } |