3.5" inch TFT LCD Display Module 480X320 driven with FSMC.

TFT LCD Display Module 480X320 driven with FSMC

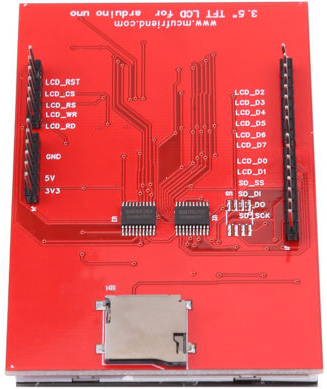

I have recently bought a 3.5" inch TFT LCD Touch Screen Display Module 480X320 with a www.mcufriend.com label on the back side. The display was equipped with an 8bit parallel interface. First I decided to test it with the UniGraphic library using the BUS_8 protocol. The display was very slow but improved when I switched to the PAR_8 protocol. Because I heard about the possibility to use a Flexible Static Memory Controller (FSMC), built into some STM MCU's, to drive LCD's (read/write to LCD's memory rather than to an external SRAM) I thought it would be a fun to try it out.

Below is the brief story of what I did:

- Created a project for my STM32F407VE board in the STM32CubeIDE

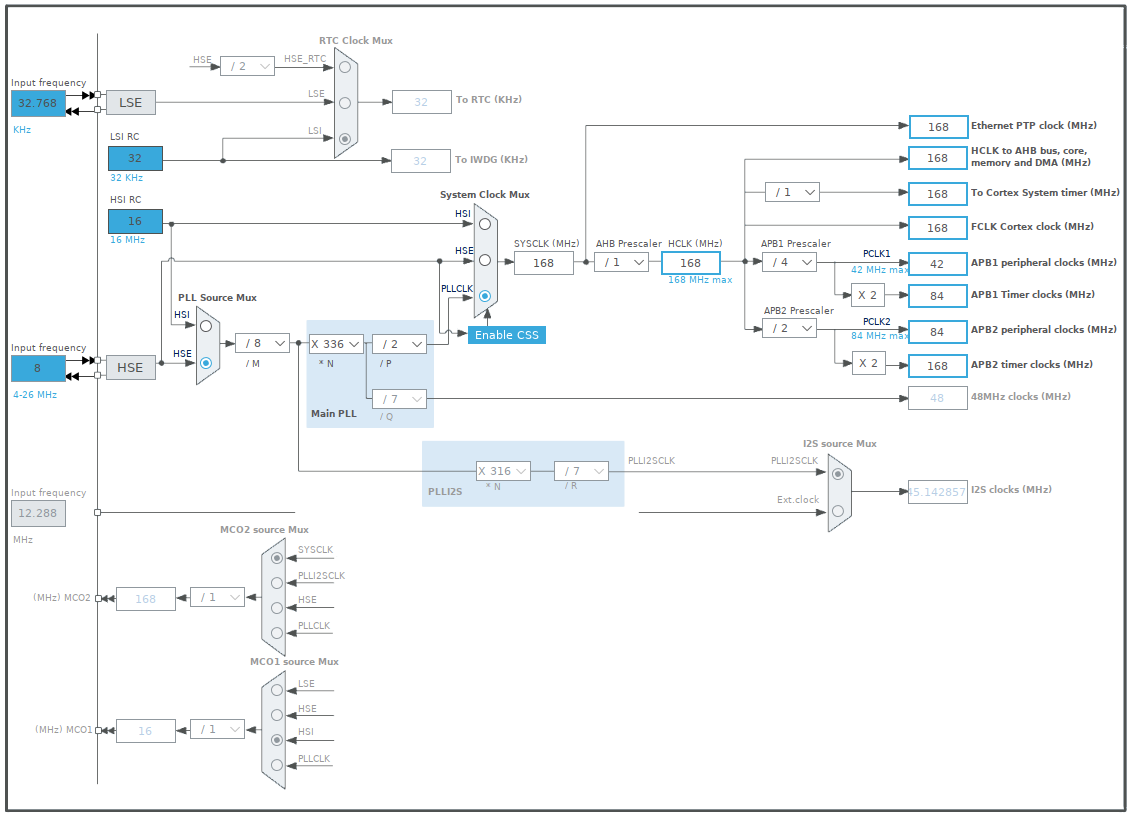

- Set the

Clock Configurationto match the one used by Mbed for the Seeed Arch Max board:

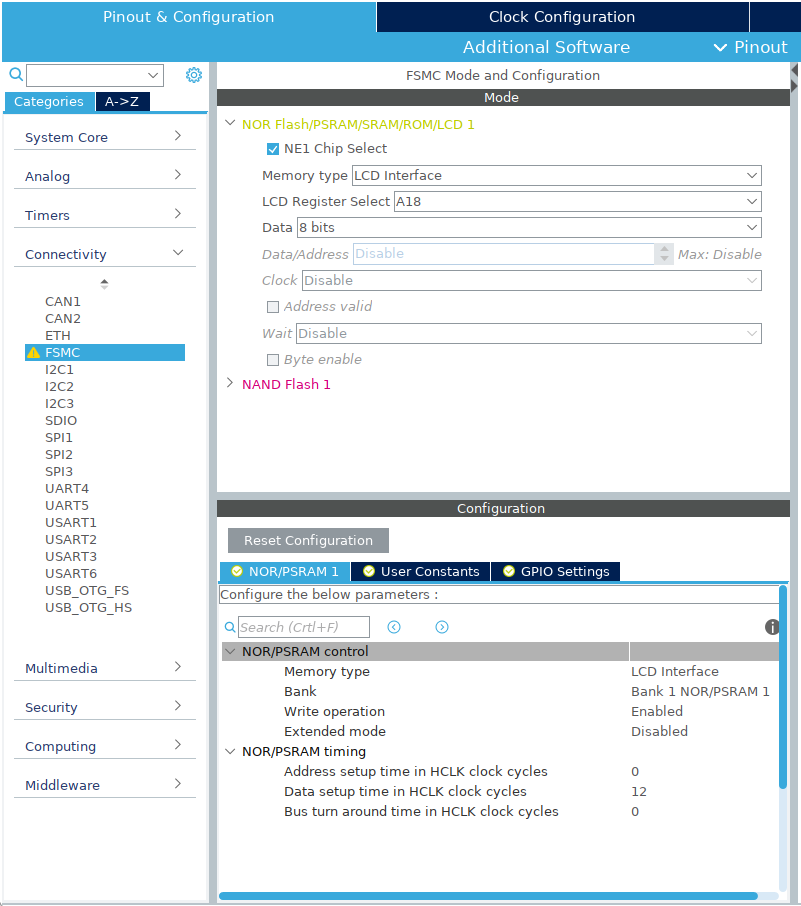

- Selected

FSMCin theConnectivitycategory and configured it as below:

- Let the

STM32CubeIDEgenerate the code (files). - Created a new program for the Seeed Arch Max target in the Mbed Online Compiler by selecting a

mbed os blinkytemplate. - Replaced the

main.cppwith themain.ccontent of theSTM32CubeIDEproject. Copy & Pastedthe other files with codes from theSTM32CubeIDEproject to the online compiler project.- Renamed and modified:

"stm32f4xx_it.h" to "stm32f4xx_it_msp.h"

"stm32f4xx_it.c" to "stm32f4xx_it_msp.c" - Added the UniGraphic library to the online compiler project.

- Extended the

UniGraphiclibrary with aFSMC_8protocol and replaced theTFT::set_orientation(int orient)function with the one used bymcufriendfor arduino. - Modified the

main.cppas needed.

|  |

Wiring

| STM32F407VE | TFT LCD module |

|---|---|

| +3.3V | 3V3 |

| GND | GND |

| PB_12 | LCD_RST |

| GND | LCD_CS |

| PD_13 (RS) | LCD_RS |

| PD_5 (WR) | LCD_WR |

| PD_4 (RD) | LCD_RD |

| PD_14 (DB00) | LCD_D0 |

| PD_15 (DB01) | LCD_D1 |

| PD_0 (DB02) | LCD_D2 |

| PD_1 (DB03) | LCD_D3 |

| PE_7 (DB04) | LCD_D4 |

| PE_8 (DB05) | LCD_D5 |

| PE_9 (DB06) | LCD_D6 |

| PE_10 (DB07) | LCD_D7 |

Results

| Execution times | ||

|---|---|---|

| Used protocol | BUS_8 | FSMC_8 |

| Operation \ Time | ms | ms |

| Clear | 2283.980 | 38.454 |

| Plot | 192.066 | 11.365 |

| 8bit BMP | 63.805 | 41.338 |

| Large Font | 163.872 | 7.895 |

| Sparce pixels | 2072.265/1458.051 | 74.107/52.168 |

| 16bit BMP | 2288.589 | 59.904 |

UniGraphic/Inits/SEPS225.cpp@1:47c996032a9e, 2020-09-25 (annotated)

- Committer:

- hudakz

- Date:

- Fri Sep 25 14:52:27 2020 +0000

- Revision:

- 1:47c996032a9e

- Parent:

- 0:fa952828e34c

3.5" inch TFT LCD Display Module 480X320 driven with FSMC.

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| hudakz | 0:fa952828e34c | 1 | #include "mbed.h" |

| hudakz | 0:fa952828e34c | 2 | |

| hudakz | 0:fa952828e34c | 3 | #include "SEPS225.h" |

| hudakz | 0:fa952828e34c | 4 | |

| hudakz | 0:fa952828e34c | 5 | #ifndef OLED_LCD_REG_H_ |

| hudakz | 0:fa952828e34c | 6 | #define OLED_LCD_REG_H_ |

| hudakz | 0:fa952828e34c | 7 | |

| hudakz | 0:fa952828e34c | 8 | #define CMD_INDEX 0x00 |

| hudakz | 0:fa952828e34c | 9 | #define CMD_STATUS_RD 0x01 |

| hudakz | 0:fa952828e34c | 10 | #define CMD_OSC_CTL 0x02 |

| hudakz | 0:fa952828e34c | 11 | #define CMD_CLOCK_DIV 0x03 |

| hudakz | 0:fa952828e34c | 12 | #define CMD_REDUCE_CURRENT 0x04 |

| hudakz | 0:fa952828e34c | 13 | #define CMD_SOFT_RST 0x05 |

| hudakz | 0:fa952828e34c | 14 | #define CMD_DISP_ON_OFF 0x06 |

| hudakz | 0:fa952828e34c | 15 | #define CMD_PRECHARGE_TIME_R 0x08 |

| hudakz | 0:fa952828e34c | 16 | #define CMD_PRECHARGE_TIME_G 0x09 |

| hudakz | 0:fa952828e34c | 17 | #define CMD_PRECHARGE_TIME_B 0x0A |

| hudakz | 0:fa952828e34c | 18 | #define CMD_PRECHARGE_CURRENT_R 0x0B |

| hudakz | 0:fa952828e34c | 19 | #define CMD_PRECHARGE_CURRENT_G 0x0C |

| hudakz | 0:fa952828e34c | 20 | #define CMD_PRECHARGE_CURRENT_B 0x0D |

| hudakz | 0:fa952828e34c | 21 | #define CMD_DRIVING_CURRENT_R 0x10 |

| hudakz | 0:fa952828e34c | 22 | #define CMD_DRIVING_CURRENT_G 0x11 |

| hudakz | 0:fa952828e34c | 23 | #define CMD_DRIVING_CURRENT_B 0x12 |

| hudakz | 0:fa952828e34c | 24 | #define CMD_DISPLAY_MODE_SET 0x13 |

| hudakz | 0:fa952828e34c | 25 | #define CMD_RGB_IF 0x14 |

| hudakz | 0:fa952828e34c | 26 | #define CMD_RGB_POL 0x15 |

| hudakz | 0:fa952828e34c | 27 | #define CMD_MEMORY_WRITE_MODE 0x16 |

| hudakz | 0:fa952828e34c | 28 | #define CMD_MX1_ADDR 0x17 |

| hudakz | 0:fa952828e34c | 29 | #define CMD_MX2_ADDR 0x18 |

| hudakz | 0:fa952828e34c | 30 | #define CMD_MY1_ADDR 0x19 |

| hudakz | 0:fa952828e34c | 31 | #define CMD_MY2_ADDR 0x1A |

| hudakz | 0:fa952828e34c | 32 | #define CMD_MEMORY_ACCESS_POINTER_X 0x20 |

| hudakz | 0:fa952828e34c | 33 | #define CMD_MEMORY_ACCESS_POINTER_Y 0x21 |

| hudakz | 0:fa952828e34c | 34 | #define CMD_DDRAM_DATA_ACCESS_PORT 0x22 |

| hudakz | 0:fa952828e34c | 35 | #define CMD_DUTY 0x28 |

| hudakz | 0:fa952828e34c | 36 | #define CMD_DSL 0x29 |

| hudakz | 0:fa952828e34c | 37 | #define CMD_D1_DDRAM_FAC 0x2E |

| hudakz | 0:fa952828e34c | 38 | #define CMD_D1_DDRAM_FAR 0x2F |

| hudakz | 0:fa952828e34c | 39 | #define CMD_D2_DDRAM_SAC 0x31 |

| hudakz | 0:fa952828e34c | 40 | #define CMD_D2_DDRAM_SAR 0x32 |

| hudakz | 0:fa952828e34c | 41 | #define CMD_SCR1_FX1 0x33 |

| hudakz | 0:fa952828e34c | 42 | #define CMD_SCR1_FX2 0x34 |

| hudakz | 0:fa952828e34c | 43 | #define CMD_SCR1_FY1 0x35 |

| hudakz | 0:fa952828e34c | 44 | #define CMD_SCR1_FY2 0x36 |

| hudakz | 0:fa952828e34c | 45 | #define CMD_SCR2_SX1 0x37 |

| hudakz | 0:fa952828e34c | 46 | #define CMD_SCR2_SX2 0x38 |

| hudakz | 0:fa952828e34c | 47 | #define CMD_SCR2_SY1 0x39 |

| hudakz | 0:fa952828e34c | 48 | #define CMD_SCR2_SY2 0x3A |

| hudakz | 0:fa952828e34c | 49 | #define CMD_SCREEN_SAVER_CONTEROL 0x3B |

| hudakz | 0:fa952828e34c | 50 | #define CMD_SS_SLEEP_TIMER 0x3C |

| hudakz | 0:fa952828e34c | 51 | #define CMD_SCREEN_SAVER_MODE 0x3D |

| hudakz | 0:fa952828e34c | 52 | #define CMD_SS_SCR1_FU 0x3E |

| hudakz | 0:fa952828e34c | 53 | #define CMD_SS_SCR1_MXY 0x3F |

| hudakz | 0:fa952828e34c | 54 | #define CMD_SS_SCR2_FU 0x40 |

| hudakz | 0:fa952828e34c | 55 | #define CMD_SS_SCR2_MXY 0x41 |

| hudakz | 0:fa952828e34c | 56 | #define CMD_MOVING_DIRECTION 0x42 |

| hudakz | 0:fa952828e34c | 57 | #define CMD_SS_SCR2_SX1 0x47 |

| hudakz | 0:fa952828e34c | 58 | #define CMD_SS_SCR2_SX2 0x48 |

| hudakz | 0:fa952828e34c | 59 | #define CMD_SS_SCR2_SY1 0x49 |

| hudakz | 0:fa952828e34c | 60 | #define CMD_SS_SCR2_SY2 0x4A |

| hudakz | 0:fa952828e34c | 61 | #define CMD_IREF 0x80 |

| hudakz | 0:fa952828e34c | 62 | |

| hudakz | 0:fa952828e34c | 63 | |

| hudakz | 0:fa952828e34c | 64 | #define LCD_RESET 0 |

| hudakz | 0:fa952828e34c | 65 | #define LCD_CLEAR 1 |

| hudakz | 0:fa952828e34c | 66 | #define LCD_PRINT 2 |

| hudakz | 0:fa952828e34c | 67 | |

| hudakz | 0:fa952828e34c | 68 | |

| hudakz | 0:fa952828e34c | 69 | #define COLOR_RED 0xF100 |

| hudakz | 0:fa952828e34c | 70 | #define COLOR_GREEN 0x07E0 |

| hudakz | 0:fa952828e34c | 71 | #define COLOR_BLUE 0x001F |

| hudakz | 0:fa952828e34c | 72 | #define COLOR_CYAN 0x07FF |

| hudakz | 0:fa952828e34c | 73 | #define COLOR_MAGENTA 0xF11F |

| hudakz | 0:fa952828e34c | 74 | #define COLOR_YELLOW 0xFFE0 |

| hudakz | 0:fa952828e34c | 75 | #define COLOR_BLACK 0x0000 |

| hudakz | 0:fa952828e34c | 76 | #define COLOR_WHITE 0xFFFF |

| hudakz | 0:fa952828e34c | 77 | |

| hudakz | 0:fa952828e34c | 78 | #define OLED_WIDTH 0x80 |

| hudakz | 0:fa952828e34c | 79 | #define OLED_HEIGHT 0x80 |

| hudakz | 0:fa952828e34c | 80 | |

| hudakz | 0:fa952828e34c | 81 | #endif /* OLED_LCD_REG_H_ */ |

| hudakz | 0:fa952828e34c | 82 | |

| hudakz | 0:fa952828e34c | 83 | SEPS225::SEPS225(proto_t displayproto, PortName port, PinName CS, PinName reset, PinName DC, PinName WR, PinName RD, const char *name, unsigned int LCDSIZE_X, unsigned int LCDSIZE_Y) |

| hudakz | 0:fa952828e34c | 84 | : TFT(displayproto, port, CS, reset, DC, WR, RD, LCDSIZE_X, LCDSIZE_Y, name) |

| hudakz | 0:fa952828e34c | 85 | { |

| hudakz | 0:fa952828e34c | 86 | hw_reset(); |

| hudakz | 0:fa952828e34c | 87 | BusEnable(true); |

| hudakz | 0:fa952828e34c | 88 | identify(); // will collect tftID and set mipistd flag |

| hudakz | 0:fa952828e34c | 89 | init(); |

| hudakz | 0:fa952828e34c | 90 | auto_gram_read_format(); |

| hudakz | 0:fa952828e34c | 91 | set_orientation(0); |

| hudakz | 0:fa952828e34c | 92 | cls(); |

| hudakz | 0:fa952828e34c | 93 | FastWindow(true); // most but not all controllers support this, even if datasheet tells they should. |

| hudakz | 0:fa952828e34c | 94 | locate(0,0); |

| hudakz | 0:fa952828e34c | 95 | } |

| hudakz | 0:fa952828e34c | 96 | SEPS225::SEPS225(proto_t displayproto, PinName* buspins, PinName CS, PinName reset, PinName DC, PinName WR, PinName RD, const char *name, unsigned int LCDSIZE_X, unsigned int LCDSIZE_Y) |

| hudakz | 0:fa952828e34c | 97 | : TFT(displayproto, buspins, CS, reset, DC, WR, RD, LCDSIZE_X, LCDSIZE_Y, name) |

| hudakz | 0:fa952828e34c | 98 | { |

| hudakz | 0:fa952828e34c | 99 | hw_reset(); |

| hudakz | 0:fa952828e34c | 100 | BusEnable(true); |

| hudakz | 0:fa952828e34c | 101 | identify(); // will collect tftID and set mipistd flag |

| hudakz | 0:fa952828e34c | 102 | init(); |

| hudakz | 0:fa952828e34c | 103 | auto_gram_read_format(); |

| hudakz | 0:fa952828e34c | 104 | set_orientation(0); |

| hudakz | 0:fa952828e34c | 105 | cls(); |

| hudakz | 0:fa952828e34c | 106 | FastWindow(true); // most but not all controllers support this, even if datasheet tells they should. |

| hudakz | 0:fa952828e34c | 107 | locate(0,0); |

| hudakz | 0:fa952828e34c | 108 | } |

| hudakz | 0:fa952828e34c | 109 | SEPS225::SEPS225(proto_t displayproto, int Hz, PinName mosi, PinName miso, PinName sclk, PinName CS, PinName reset, PinName DC, const char *name, unsigned int LCDSIZE_X , unsigned int LCDSIZE_Y) |

| hudakz | 0:fa952828e34c | 110 | : TFT(displayproto, Hz, mosi, miso, sclk, CS, reset, DC, LCDSIZE_X, LCDSIZE_Y, name) |

| hudakz | 0:fa952828e34c | 111 | { |

| hudakz | 0:fa952828e34c | 112 | _cs = new DigitalOut(CS, 1) ; |

| hudakz | 0:fa952828e34c | 113 | _rs = new DigitalOut(DC, 1) ; |

| hudakz | 0:fa952828e34c | 114 | |

| hudakz | 0:fa952828e34c | 115 | hw_reset(); //TFT class forwards to Protocol class |

| hudakz | 0:fa952828e34c | 116 | BusEnable(true); //TFT class forwards to Protocol class |

| hudakz | 0:fa952828e34c | 117 | identify(); // will collect tftID and set mipistd flag |

| hudakz | 0:fa952828e34c | 118 | init(); // per display custom init cmd sequence, implemented here |

| hudakz | 0:fa952828e34c | 119 | auto_gram_read_format();// try to get read gram pixel format, could be 16bit or 18bit, RGB or BGR. Will set flags accordingly |

| hudakz | 0:fa952828e34c | 120 | set_orientation(0); //TFT class does for MIPI standard and some ILIxxx |

| hudakz | 0:fa952828e34c | 121 | FastWindow(true); // most but not all controllers support this, even if datasheet tells they should. |

| hudakz | 0:fa952828e34c | 122 | cls(); |

| hudakz | 0:fa952828e34c | 123 | locate(0,0); |

| hudakz | 0:fa952828e34c | 124 | } |

| hudakz | 0:fa952828e34c | 125 | |

| hudakz | 0:fa952828e34c | 126 | // reset and init the lcd controller |

| hudakz | 0:fa952828e34c | 127 | void SEPS225::init() |

| hudakz | 0:fa952828e34c | 128 | { |

| hudakz | 0:fa952828e34c | 129 | #if 0 |

| hudakz | 0:fa952828e34c | 130 | oled = new SPI(PIN_OLED_MOSI, PIN_OLED_MISO, PIN_OLED_SCLK) ; |

| hudakz | 0:fa952828e34c | 131 | oled_cs = new DigitalOut(PIN_OLED_CS, 1) ; |

| hudakz | 0:fa952828e34c | 132 | oled_rs = new DigitalOut(PIN_OLED_RS, 1) ; |

| hudakz | 0:fa952828e34c | 133 | oled->format(8, 0) ; |

| hudakz | 0:fa952828e34c | 134 | oled->frequency(1000000) ; |

| hudakz | 0:fa952828e34c | 135 | #endif |

| hudakz | 0:fa952828e34c | 136 | |

| hudakz | 0:fa952828e34c | 137 | reg_write(CMD_REDUCE_CURRENT, 0x01) ; wait(0.01) ; // oled_delay(100000) ; |

| hudakz | 0:fa952828e34c | 138 | reg_write(CMD_REDUCE_CURRENT, 0x00) ; wait(0.01) ; // oled_delay(100000) ; |

| hudakz | 0:fa952828e34c | 139 | |

| hudakz | 0:fa952828e34c | 140 | reg_write(CMD_OSC_CTL, 0x01) ; |

| hudakz | 0:fa952828e34c | 141 | reg_write(CMD_CLOCK_DIV, 0x30) ; |

| hudakz | 0:fa952828e34c | 142 | // reg_write(CMD_PRECHARGE_TIME_R, 0x03) ; |

| hudakz | 0:fa952828e34c | 143 | // reg_write(CMD_PRECHARGE_TIME_G, 0x04) ; |

| hudakz | 0:fa952828e34c | 144 | // reg_write(CMD_PRECHARGE_TIME_B, 0x05) ; |

| hudakz | 0:fa952828e34c | 145 | reg_write(CMD_PRECHARGE_TIME_R, 0x0E) ; |

| hudakz | 0:fa952828e34c | 146 | reg_write(CMD_PRECHARGE_TIME_G, 0x0E) ; |

| hudakz | 0:fa952828e34c | 147 | reg_write(CMD_PRECHARGE_TIME_B, 0x0E) ; |

| hudakz | 0:fa952828e34c | 148 | // reg_write(CMD_PRECHARGE_CURRENT_R, 0x0B) ; |

| hudakz | 0:fa952828e34c | 149 | // reg_write(CMD_PRECHARGE_CURRENT_G, 0x0B) ; |

| hudakz | 0:fa952828e34c | 150 | // reg_write(CMD_PRECHARGE_CURRENT_B, 0x0B) ; |

| hudakz | 0:fa952828e34c | 151 | reg_write(CMD_PRECHARGE_CURRENT_R, 0x3E) ; |

| hudakz | 0:fa952828e34c | 152 | reg_write(CMD_PRECHARGE_CURRENT_G, 0x32) ; |

| hudakz | 0:fa952828e34c | 153 | reg_write(CMD_PRECHARGE_CURRENT_B, 0x3D) ; |

| hudakz | 0:fa952828e34c | 154 | reg_write(CMD_DRIVING_CURRENT_R, 0x3E) ; |

| hudakz | 0:fa952828e34c | 155 | reg_write(CMD_DRIVING_CURRENT_G, 0x32) ; |

| hudakz | 0:fa952828e34c | 156 | reg_write(CMD_DRIVING_CURRENT_B, 0x3D) ; |

| hudakz | 0:fa952828e34c | 157 | // reg_write(CMD_DRIVING_CURRENT_R, 0x0B) ; |

| hudakz | 0:fa952828e34c | 158 | // reg_write(CMD_DRIVING_CURRENT_G, 0x0B) ; |

| hudakz | 0:fa952828e34c | 159 | // reg_write(CMD_DRIVING_CURRENT_B, 0x0B) ; |

| hudakz | 0:fa952828e34c | 160 | // Memory Write Mode |

| hudakz | 0:fa952828e34c | 161 | // 16bit * 1 transfer mode, R[5], G[6], B[5] |

| hudakz | 0:fa952828e34c | 162 | // H:Inc, V:Inc, Method:V |

| hudakz | 0:fa952828e34c | 163 | // reg_write(CMD_MEMORY_WRITE_MODE, 0x27) ; |

| hudakz | 0:fa952828e34c | 164 | reg_write(CMD_RGB_IF, 0x11) ; |

| hudakz | 0:fa952828e34c | 165 | // reg_write(CMD_MEMORY_WRITE_MODE, 0x66) ; |

| hudakz | 0:fa952828e34c | 166 | reg_write(CMD_MEMORY_WRITE_MODE, 0x26) ; |

| hudakz | 0:fa952828e34c | 167 | reg_write(CMD_IREF, 0x01) ; // Voltage ctrl by internal |

| hudakz | 0:fa952828e34c | 168 | // |

| hudakz | 0:fa952828e34c | 169 | reg_write(CMD_MX1_ADDR, 0x00) ; |

| hudakz | 0:fa952828e34c | 170 | reg_write(CMD_MX2_ADDR, 0x7F) ; |

| hudakz | 0:fa952828e34c | 171 | reg_write(CMD_MY1_ADDR, 0x00) ; |

| hudakz | 0:fa952828e34c | 172 | reg_write(CMD_MY2_ADDR, 0x7F) ; |

| hudakz | 0:fa952828e34c | 173 | reg_write(CMD_SCR1_FX1, 0x00) ; |

| hudakz | 0:fa952828e34c | 174 | reg_write(CMD_SCR1_FX2, 0x7F) ; |

| hudakz | 0:fa952828e34c | 175 | reg_write(CMD_SCR1_FY1, 0x00) ; |

| hudakz | 0:fa952828e34c | 176 | reg_write(CMD_SCR1_FY2, 0x7F) ; |

| hudakz | 0:fa952828e34c | 177 | reg_write(CMD_DSL, 0x00) ; // display start line |

| hudakz | 0:fa952828e34c | 178 | reg_write(CMD_DUTY, 0x7F) ; // |

| hudakz | 0:fa952828e34c | 179 | reg_write(CMD_DISPLAY_MODE_SET, 0x04) ; // was 0x00 |

| hudakz | 0:fa952828e34c | 180 | // reg_write(CMD_DISPLAY_MODE_SET, 0x00) ; // was 0x00 |

| hudakz | 0:fa952828e34c | 181 | reg_write(CMD_D1_DDRAM_FAC, 0x00) ; |

| hudakz | 0:fa952828e34c | 182 | reg_write(CMD_D1_DDRAM_FAR, 0x00) ; |

| hudakz | 0:fa952828e34c | 183 | // Clear |

| hudakz | 0:fa952828e34c | 184 | // oled_lcd_clear() ; |

| hudakz | 0:fa952828e34c | 185 | cls() ; |

| hudakz | 0:fa952828e34c | 186 | |

| hudakz | 0:fa952828e34c | 187 | // DISP_ON_OFF |

| hudakz | 0:fa952828e34c | 188 | // reg_write(CMD_DISP_ON_OFF, 0x01) ; |

| hudakz | 0:fa952828e34c | 189 | } |

| hudakz | 0:fa952828e34c | 190 | |

| hudakz | 0:fa952828e34c | 191 | /** Draw a pixel in the specified color. |

| hudakz | 0:fa952828e34c | 192 | * @param x is the horizontal offset to this pixel. |

| hudakz | 0:fa952828e34c | 193 | * @param y is the vertical offset to this pixel. |

| hudakz | 0:fa952828e34c | 194 | * @param color defines the color for the pixel. |

| hudakz | 0:fa952828e34c | 195 | */ |

| hudakz | 0:fa952828e34c | 196 | void SEPS225::pixel(int x, int y, unsigned short color) |

| hudakz | 0:fa952828e34c | 197 | { |

| hudakz | 0:fa952828e34c | 198 | unsigned char data[2] ; |

| hudakz | 0:fa952828e34c | 199 | data[0] = (unsigned char)((color & 0xFF00) >> 8) ; |

| hudakz | 0:fa952828e34c | 200 | data[1] = (unsigned char)(color & 0x00FF) ; |

| hudakz | 0:fa952828e34c | 201 | |

| hudakz | 0:fa952828e34c | 202 | reg_write(CMD_MEMORY_ACCESS_POINTER_X, x) ; |

| hudakz | 0:fa952828e34c | 203 | reg_write(CMD_MEMORY_ACCESS_POINTER_Y, y) ; |

| hudakz | 0:fa952828e34c | 204 | *_cs = 0 ; |

| hudakz | 0:fa952828e34c | 205 | *_rs = 0 ; |

| hudakz | 0:fa952828e34c | 206 | wr_cmd8(CMD_DDRAM_DATA_ACCESS_PORT) ; |

| hudakz | 0:fa952828e34c | 207 | *_rs = 1 ; |

| hudakz | 0:fa952828e34c | 208 | |

| hudakz | 0:fa952828e34c | 209 | wr_data8(data[0]) ; |

| hudakz | 0:fa952828e34c | 210 | wr_data8(data[1]) ; |

| hudakz | 0:fa952828e34c | 211 | *_cs = 1 ; |

| hudakz | 0:fa952828e34c | 212 | } |

| hudakz | 0:fa952828e34c | 213 | |

| hudakz | 0:fa952828e34c | 214 | void SEPS225::window(int x, int y, int w, int h) |

| hudakz | 0:fa952828e34c | 215 | { |

| hudakz | 0:fa952828e34c | 216 | reg_write(CMD_MX1_ADDR, x) ; |

| hudakz | 0:fa952828e34c | 217 | reg_write(CMD_MX2_ADDR, x+w-1) ; |

| hudakz | 0:fa952828e34c | 218 | reg_write(CMD_MY1_ADDR, y) ; |

| hudakz | 0:fa952828e34c | 219 | reg_write(CMD_MY2_ADDR, y+h-1) ; |

| hudakz | 0:fa952828e34c | 220 | reg_write(CMD_MEMORY_ACCESS_POINTER_X, x) ; |

| hudakz | 0:fa952828e34c | 221 | reg_write(CMD_MEMORY_ACCESS_POINTER_Y, y) ; |

| hudakz | 0:fa952828e34c | 222 | } |

| hudakz | 0:fa952828e34c | 223 | |

| hudakz | 0:fa952828e34c | 224 | void SEPS225::cls(void) |

| hudakz | 0:fa952828e34c | 225 | { |

| hudakz | 0:fa952828e34c | 226 | window(0, 0, OLED_WIDTH, OLED_HEIGHT) ; |

| hudakz | 0:fa952828e34c | 227 | reg_write(CMD_MEMORY_ACCESS_POINTER_X, 0) ; |

| hudakz | 0:fa952828e34c | 228 | reg_write(CMD_MEMORY_ACCESS_POINTER_Y, 0) ; |

| hudakz | 0:fa952828e34c | 229 | *_cs = 0 ; |

| hudakz | 0:fa952828e34c | 230 | *_rs = 0 ; |

| hudakz | 0:fa952828e34c | 231 | wr_cmd8(CMD_DDRAM_DATA_ACCESS_PORT) ; |

| hudakz | 0:fa952828e34c | 232 | *_rs = 1 ; |

| hudakz | 0:fa952828e34c | 233 | for (int i = 0 ; i < OLED_WIDTH * OLED_HEIGHT ; i++ ) { |

| hudakz | 0:fa952828e34c | 234 | write16(COLOR_BLACK) ; |

| hudakz | 0:fa952828e34c | 235 | } |

| hudakz | 0:fa952828e34c | 236 | *_cs = 1 ; |

| hudakz | 0:fa952828e34c | 237 | } |

| hudakz | 0:fa952828e34c | 238 | |

| hudakz | 0:fa952828e34c | 239 | unsigned short SEPS225::pixelread(int x, int y) |

| hudakz | 0:fa952828e34c | 240 | { |

| hudakz | 0:fa952828e34c | 241 | unsigned short value = 0x0000 ; |

| hudakz | 0:fa952828e34c | 242 | //printf("SEPS225::pixelread not implemented\n\r") ; |

| hudakz | 0:fa952828e34c | 243 | return(value) ; |

| hudakz | 0:fa952828e34c | 244 | } |

| hudakz | 0:fa952828e34c | 245 | |

| hudakz | 0:fa952828e34c | 246 | void SEPS225::rect(int x0, int y0, int x1, int y1, unsigned short color) |

| hudakz | 0:fa952828e34c | 247 | { |

| hudakz | 0:fa952828e34c | 248 | float interval = 0.01 ; |

| hudakz | 0:fa952828e34c | 249 | // window(x0, y0, x1-x0+1, y1-y0+1) ; |

| hudakz | 0:fa952828e34c | 250 | *_cs = 0 ; |

| hudakz | 0:fa952828e34c | 251 | wait(interval) ; |

| hudakz | 0:fa952828e34c | 252 | line(x0, y0, x1, y0, color) ; |

| hudakz | 0:fa952828e34c | 253 | *_cs = 1 ; |

| hudakz | 0:fa952828e34c | 254 | wait(interval) ; |

| hudakz | 0:fa952828e34c | 255 | *_cs = 0 ; |

| hudakz | 0:fa952828e34c | 256 | line(x1, y0, x1, y1, color) ; |

| hudakz | 0:fa952828e34c | 257 | *_cs = 1 ; |

| hudakz | 0:fa952828e34c | 258 | wait(interval) ; |

| hudakz | 0:fa952828e34c | 259 | *_cs = 0 ; |

| hudakz | 0:fa952828e34c | 260 | line(x0, y0, x0, y1, color) ; |

| hudakz | 0:fa952828e34c | 261 | *_cs = 1 ; |

| hudakz | 0:fa952828e34c | 262 | wait(interval) ; |

| hudakz | 0:fa952828e34c | 263 | *_cs = 0 ; |

| hudakz | 0:fa952828e34c | 264 | line(x0, y1, x1, y1, color) ; |

| hudakz | 0:fa952828e34c | 265 | wait(interval) ; |

| hudakz | 0:fa952828e34c | 266 | *_cs = 1 ; |

| hudakz | 0:fa952828e34c | 267 | // *_cs = 1 ; |

| hudakz | 0:fa952828e34c | 268 | } |

| hudakz | 0:fa952828e34c | 269 | |

| hudakz | 0:fa952828e34c | 270 | void SEPS225::window4read(int x, int y, int w, int h) |

| hudakz | 0:fa952828e34c | 271 | { |

| hudakz | 0:fa952828e34c | 272 | //printf("SEPS225::window4read not implemented\n\r") ; |

| hudakz | 0:fa952828e34c | 273 | } |

| hudakz | 0:fa952828e34c | 274 | |

| hudakz | 0:fa952828e34c | 275 | void SEPS225::window_pushpixel(unsigned short color) |

| hudakz | 0:fa952828e34c | 276 | { |

| hudakz | 0:fa952828e34c | 277 | //printf("SEPS225::window_pushpixel(unsigned short color) not implemented\n\r") ; |

| hudakz | 0:fa952828e34c | 278 | *_cs = 0 ; |

| hudakz | 0:fa952828e34c | 279 | *_rs = 0 ; |

| hudakz | 0:fa952828e34c | 280 | wr_cmd8(CMD_DDRAM_DATA_ACCESS_PORT) ; |

| hudakz | 0:fa952828e34c | 281 | *_rs = 1 ; |

| hudakz | 0:fa952828e34c | 282 | wr_data16(color) ; |

| hudakz | 0:fa952828e34c | 283 | // write16(color) ; |

| hudakz | 0:fa952828e34c | 284 | *_cs = 1 ; |

| hudakz | 0:fa952828e34c | 285 | } |

| hudakz | 0:fa952828e34c | 286 | |

| hudakz | 0:fa952828e34c | 287 | void SEPS225::window_pushpixel(unsigned short color, unsigned int count) |

| hudakz | 0:fa952828e34c | 288 | { |

| hudakz | 0:fa952828e34c | 289 | //printf("SEPS225::window_pushpixel(unsigned short color, unsigned int count) not implemented\n\r") ; |

| hudakz | 0:fa952828e34c | 290 | *_cs = 0 ; |

| hudakz | 0:fa952828e34c | 291 | *_rs = 0 ; |

| hudakz | 0:fa952828e34c | 292 | wr_cmd8(CMD_DDRAM_DATA_ACCESS_PORT) ; |

| hudakz | 0:fa952828e34c | 293 | *_rs = 1 ; |

| hudakz | 0:fa952828e34c | 294 | for (unsigned int i = 0 ; i < count ; i++ ) { |

| hudakz | 0:fa952828e34c | 295 | // write16(color) ; |

| hudakz | 0:fa952828e34c | 296 | wr_data16(color) ; |

| hudakz | 0:fa952828e34c | 297 | } |

| hudakz | 0:fa952828e34c | 298 | *_cs = 1 ; |

| hudakz | 0:fa952828e34c | 299 | } |

| hudakz | 0:fa952828e34c | 300 | |

| hudakz | 0:fa952828e34c | 301 | void SEPS225::window_pushpixelbuf(unsigned short* color, unsigned int lenght) |

| hudakz | 0:fa952828e34c | 302 | { |

| hudakz | 0:fa952828e34c | 303 | //printf("SEPS225::window_pushpixelbuf(unsigned short color, unsigned int length) not implemented\n\r") ; |

| hudakz | 0:fa952828e34c | 304 | *_cs = 0 ; |

| hudakz | 0:fa952828e34c | 305 | *_rs = 0 ; |

| hudakz | 0:fa952828e34c | 306 | wr_cmd8(CMD_DDRAM_DATA_ACCESS_PORT) ; |

| hudakz | 0:fa952828e34c | 307 | *_rs = 1 ; |

| hudakz | 0:fa952828e34c | 308 | for (unsigned int i = 0 ; i < lenght ; i++ ) { |

| hudakz | 0:fa952828e34c | 309 | // write16(color[i]) ; |

| hudakz | 0:fa952828e34c | 310 | wr_data16(color[i]) ; |

| hudakz | 0:fa952828e34c | 311 | } |

| hudakz | 0:fa952828e34c | 312 | *_cs = 1 ; |

| hudakz | 0:fa952828e34c | 313 | } |

| hudakz | 0:fa952828e34c | 314 | |

| hudakz | 0:fa952828e34c | 315 | void SEPS225::reg_write(unsigned char cmd, unsigned char data) |

| hudakz | 0:fa952828e34c | 316 | { |

| hudakz | 0:fa952828e34c | 317 | *_cs = 0 ; |

| hudakz | 0:fa952828e34c | 318 | *_rs = 0 ; |

| hudakz | 0:fa952828e34c | 319 | wr_cmd8(cmd) ; |

| hudakz | 0:fa952828e34c | 320 | *_rs = 1 ; |

| hudakz | 0:fa952828e34c | 321 | wr_data8(data) ; |

| hudakz | 0:fa952828e34c | 322 | *_cs = 1 ; |

| hudakz | 0:fa952828e34c | 323 | } |

| hudakz | 0:fa952828e34c | 324 | |

| hudakz | 0:fa952828e34c | 325 | void SEPS225::display(int onoff) |

| hudakz | 0:fa952828e34c | 326 | { |

| hudakz | 0:fa952828e34c | 327 | reg_write(CMD_DISP_ON_OFF, onoff) ; |

| hudakz | 0:fa952828e34c | 328 | } |

| hudakz | 0:fa952828e34c | 329 | |

| hudakz | 0:fa952828e34c | 330 | void SEPS225::cmd_write(unsigned char cmd) |

| hudakz | 0:fa952828e34c | 331 | { |

| hudakz | 0:fa952828e34c | 332 | *_cs = 0 ; |

| hudakz | 0:fa952828e34c | 333 | *_rs = 0 ; |

| hudakz | 0:fa952828e34c | 334 | wr_cmd8(cmd) ; |

| hudakz | 0:fa952828e34c | 335 | *_rs = 1 ; |

| hudakz | 0:fa952828e34c | 336 | *_cs = 1 ; |

| hudakz | 0:fa952828e34c | 337 | } |

| hudakz | 0:fa952828e34c | 338 | |

| hudakz | 0:fa952828e34c | 339 | void SEPS225::data_write(unsigned char data) |

| hudakz | 0:fa952828e34c | 340 | { |

| hudakz | 0:fa952828e34c | 341 | *_cs = 0 ; |

| hudakz | 0:fa952828e34c | 342 | wr_data8(data) ; |

| hudakz | 0:fa952828e34c | 343 | *_cs = 1 ; |

| hudakz | 0:fa952828e34c | 344 | } |

| hudakz | 0:fa952828e34c | 345 | |

| hudakz | 0:fa952828e34c | 346 | void SEPS225::write8(unsigned char data) |

| hudakz | 0:fa952828e34c | 347 | { |

| hudakz | 0:fa952828e34c | 348 | wr_data8(data) ; |

| hudakz | 0:fa952828e34c | 349 | } |

| hudakz | 0:fa952828e34c | 350 | |

| hudakz | 0:fa952828e34c | 351 | void SEPS225::write16(unsigned short sdata) |

| hudakz | 0:fa952828e34c | 352 | { |

| hudakz | 0:fa952828e34c | 353 | wr_data8((sdata >> 8)&0xFF) ; |

| hudakz | 0:fa952828e34c | 354 | wr_data8(sdata & 0xFF) ; |

| hudakz | 0:fa952828e34c | 355 | } |

| hudakz | 0:fa952828e34c | 356 | |

| hudakz | 0:fa952828e34c | 357 | void SEPS225::bufwrite8(unsigned char *data, unsigned long len) |

| hudakz | 0:fa952828e34c | 358 | { |

| hudakz | 0:fa952828e34c | 359 | unsigned long i; |

| hudakz | 0:fa952828e34c | 360 | for (i = 0 ; i < len ; i++ ) { |

| hudakz | 0:fa952828e34c | 361 | wr_data8(data[i]) ; |

| hudakz | 0:fa952828e34c | 362 | } |

| hudakz | 0:fa952828e34c | 363 | } |

| hudakz | 0:fa952828e34c | 364 | |

| hudakz | 0:fa952828e34c | 365 | void SEPS225::bufwrite16(unsigned short *sdata, unsigned long len) |

| hudakz | 0:fa952828e34c | 366 | { |

| hudakz | 0:fa952828e34c | 367 | unsigned long i ; |

| hudakz | 0:fa952828e34c | 368 | for (i = 0 ; i < len ; i++) { |

| hudakz | 0:fa952828e34c | 369 | write8((*sdata >> 8)&0xFF) ; |

| hudakz | 0:fa952828e34c | 370 | write8(*sdata & 0xFF) ; |

| hudakz | 0:fa952828e34c | 371 | } |

| hudakz | 0:fa952828e34c | 372 | } |