Lib to change the clock speed of the ST Nucleo L152RE board to 32 MHz.

The ST Nucleo L152 board is running on 16 MHz out of the box. To speed up the cpu to the maximum 32MHz speed we have to change the clock setting. Simply add the lib and :

#include "ST_L152_32MHZ.h"

L152_init32 myinit(0); // use the internal oscillator

in front of your program. This should be the first line in main to ensure the frequency is changed before other objects are initialised.

This frequency is generated out of the internal RC oscillator. The frequency is not so stable like a crystal. The PLL is switched to 96MHz to enable the use of the USB interface.

If you need a more precise timing source, you have to add a external crystal.

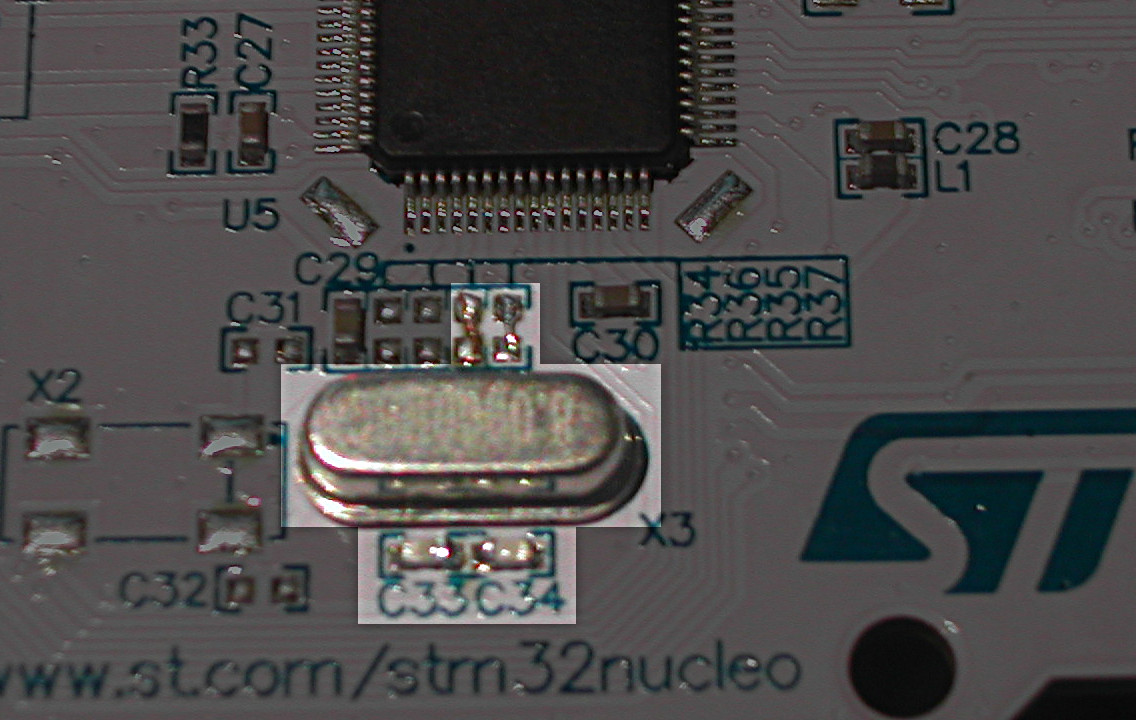

You need : X3 8MHz crystal , C33 and C34 18pF 0603 , R35 and R37 have to be short with a small piece of wire.

#include "ST_L152_32MHZ.h"

L152_init32 myinit(1); // use external crystal oscillator

ST_L152_32MHZ.cpp@3:1e82f1f333ad, 2014-04-08 (annotated)

- Committer:

- dreschpe

- Date:

- Tue Apr 08 17:17:56 2014 +0000

- Revision:

- 3:1e82f1f333ad

- Parent:

- 2:9e2ba1d93567

We have to reset the clock setting to change the pll

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| dreschpe | 1:bdeac50afe1a | 1 | /* mbed library for the ST NUCLEO board L152RE |

| dreschpe | 1:bdeac50afe1a | 2 | * to change the CPU clock to 32 MHz |

| dreschpe | 1:bdeac50afe1a | 3 | * A pll clock of 96 MHz is used to enable USB |

| dreschpe | 1:bdeac50afe1a | 4 | * |

| dreschpe | 1:bdeac50afe1a | 5 | * Copyright (c) 2014 Peter Drescher - DC2PD |

| dreschpe | 1:bdeac50afe1a | 6 | * Released under the MIT License: http://mbed.org/license/mit |

| dreschpe | 1:bdeac50afe1a | 7 | * |

| dreschpe | 1:bdeac50afe1a | 8 | * THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR |

| dreschpe | 1:bdeac50afe1a | 9 | * IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, |

| dreschpe | 1:bdeac50afe1a | 10 | * FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE |

| dreschpe | 1:bdeac50afe1a | 11 | * AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER |

| dreschpe | 1:bdeac50afe1a | 12 | * LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, |

| dreschpe | 1:bdeac50afe1a | 13 | * OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN |

| dreschpe | 1:bdeac50afe1a | 14 | * THE SOFTWARE. |

| dreschpe | 1:bdeac50afe1a | 15 | */ |

| dreschpe | 1:bdeac50afe1a | 16 | |

| dreschpe | 0:84e23a19e37d | 17 | #include "stm32l1xx.h" |

| dreschpe | 0:84e23a19e37d | 18 | #include "stm32l1xx_flash.h" |

| dreschpe | 0:84e23a19e37d | 19 | #include "stm32l1xx_rcc.h" |

| dreschpe | 0:84e23a19e37d | 20 | #include "ST_L152_32MHZ.h" |

| dreschpe | 0:84e23a19e37d | 21 | |

| dreschpe | 1:bdeac50afe1a | 22 | // only the constructor |

| dreschpe | 0:84e23a19e37d | 23 | L152_init32::L152_init32(unsigned int external){ |

| dreschpe | 1:bdeac50afe1a | 24 | Status = setup_clock_32MHZ(external); |

| dreschpe | 0:84e23a19e37d | 25 | } |

| dreschpe | 0:84e23a19e37d | 26 | |

| dreschpe | 0:84e23a19e37d | 27 | #define PLL_STARTUP_TIMEOUT 0x5000 |

| dreschpe | 0:84e23a19e37d | 28 | |

| dreschpe | 1:bdeac50afe1a | 29 | ClockStatus L152_init32::setup_clock_32MHZ(int external) |

| dreschpe | 0:84e23a19e37d | 30 | { |

| dreschpe | 0:84e23a19e37d | 31 | uint32_t PLLStartUpCounter = 0,PLLStatus = 0,error; |

| dreschpe | 0:84e23a19e37d | 32 | |

| dreschpe | 3:1e82f1f333ad | 33 | RCC_DeInit(); // we have to reset the clock settings ! |

| dreschpe | 2:9e2ba1d93567 | 34 | /* Enable 64-bit access */ |

| dreschpe | 2:9e2ba1d93567 | 35 | FLASH->ACR |= FLASH_ACR_ACC64; |

| dreschpe | 2:9e2ba1d93567 | 36 | |

| dreschpe | 2:9e2ba1d93567 | 37 | /* Enable Prefetch Buffer */ |

| dreschpe | 2:9e2ba1d93567 | 38 | FLASH->ACR |= FLASH_ACR_PRFTEN; |

| dreschpe | 2:9e2ba1d93567 | 39 | |

| dreschpe | 2:9e2ba1d93567 | 40 | /* Flash 1 wait state */ |

| dreschpe | 2:9e2ba1d93567 | 41 | FLASH->ACR |= FLASH_ACR_LATENCY; |

| dreschpe | 2:9e2ba1d93567 | 42 | |

| dreschpe | 2:9e2ba1d93567 | 43 | /* Power enable */ |

| dreschpe | 2:9e2ba1d93567 | 44 | RCC->APB1ENR |= RCC_APB1ENR_PWREN; |

| dreschpe | 2:9e2ba1d93567 | 45 | |

| dreschpe | 2:9e2ba1d93567 | 46 | /* Select the Voltage Range 1 (1.8 V) */ |

| dreschpe | 2:9e2ba1d93567 | 47 | PWR->CR = PWR_CR_VOS_0; |

| dreschpe | 2:9e2ba1d93567 | 48 | |

| dreschpe | 2:9e2ba1d93567 | 49 | /* Wait Until the Voltage Regulator is ready */ |

| dreschpe | 2:9e2ba1d93567 | 50 | while((PWR->CSR & PWR_CSR_VOSF) != RESET) |

| dreschpe | 2:9e2ba1d93567 | 51 | { |

| dreschpe | 2:9e2ba1d93567 | 52 | } |

| dreschpe | 2:9e2ba1d93567 | 53 | |

| dreschpe | 2:9e2ba1d93567 | 54 | /* HCLK = SYSCLK /1*/ |

| dreschpe | 2:9e2ba1d93567 | 55 | RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1; |

| dreschpe | 2:9e2ba1d93567 | 56 | /* PCLK2 = HCLK /1*/ |

| dreschpe | 2:9e2ba1d93567 | 57 | RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1; |

| dreschpe | 2:9e2ba1d93567 | 58 | |

| dreschpe | 2:9e2ba1d93567 | 59 | /* PCLK1 = HCLK /1*/ |

| dreschpe | 2:9e2ba1d93567 | 60 | RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV1; |

| dreschpe | 2:9e2ba1d93567 | 61 | |

| dreschpe | 2:9e2ba1d93567 | 62 | /* PLL configuration */ |

| dreschpe | 2:9e2ba1d93567 | 63 | RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLMUL | |

| dreschpe | 2:9e2ba1d93567 | 64 | RCC_CFGR_PLLDIV)); |

| dreschpe | 2:9e2ba1d93567 | 65 | |

| dreschpe | 2:9e2ba1d93567 | 66 | if(external == 0){ |

| dreschpe | 2:9e2ba1d93567 | 67 | RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSI | RCC_CFGR_PLLMUL6 | RCC_CFGR_PLLDIV3); |

| dreschpe | 2:9e2ba1d93567 | 68 | } |

| dreschpe | 2:9e2ba1d93567 | 69 | else{ |

| dreschpe | 2:9e2ba1d93567 | 70 | RCC_HSEConfig(RCC_HSE_ON); // start external crystal osc. |

| dreschpe | 0:84e23a19e37d | 71 | error = RCC_WaitForHSEStartUp(); |

| dreschpe | 0:84e23a19e37d | 72 | if(error == ERROR ) { // no external crystal |

| dreschpe | 1:bdeac50afe1a | 73 | return(EXT_ERR); |

| dreschpe | 2:9e2ba1d93567 | 74 | } |

| dreschpe | 2:9e2ba1d93567 | 75 | RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMUL12 | RCC_CFGR_PLLDIV3); |

| dreschpe | 2:9e2ba1d93567 | 76 | } |

| dreschpe | 2:9e2ba1d93567 | 77 | |

| dreschpe | 2:9e2ba1d93567 | 78 | /* Enable PLL */ |

| dreschpe | 2:9e2ba1d93567 | 79 | RCC->CR |= RCC_CR_PLLON; |

| dreschpe | 2:9e2ba1d93567 | 80 | |

| dreschpe | 2:9e2ba1d93567 | 81 | /* Wait till PLL is ready */ |

| dreschpe | 0:84e23a19e37d | 82 | do { |

| dreschpe | 0:84e23a19e37d | 83 | PLLStatus = RCC->CR & RCC_CR_PLLRDY; |

| dreschpe | 0:84e23a19e37d | 84 | } while((PLLStatus == 0) && (PLLStartUpCounter < PLL_STARTUP_TIMEOUT)); // wait for pll |

| dreschpe | 0:84e23a19e37d | 85 | if(PLLStatus == 0) { |

| dreschpe | 1:bdeac50afe1a | 86 | return(PLL_ERR); |

| dreschpe | 0:84e23a19e37d | 87 | } |

| dreschpe | 2:9e2ba1d93567 | 88 | |

| dreschpe | 2:9e2ba1d93567 | 89 | /* Select PLL as system clock source */ |

| dreschpe | 2:9e2ba1d93567 | 90 | RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW)); |

| dreschpe | 2:9e2ba1d93567 | 91 | RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL; |

| dreschpe | 2:9e2ba1d93567 | 92 | |

| dreschpe | 2:9e2ba1d93567 | 93 | /* Wait till PLL is used as system clock source */ |

| dreschpe | 2:9e2ba1d93567 | 94 | while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)RCC_CFGR_SWS_PLL) |

| dreschpe | 2:9e2ba1d93567 | 95 | { |

| dreschpe | 2:9e2ba1d93567 | 96 | } |

| dreschpe | 0:84e23a19e37d | 97 | SystemCoreClockUpdate(); // update SystemCoreClock var |

| dreschpe | 1:bdeac50afe1a | 98 | return(OK); |

| dreschpe | 2:9e2ba1d93567 | 99 | } |

| dreschpe | 2:9e2ba1d93567 | 100 |