Lib for FTDI FT800 graphic controller "EVE" The API is changed from the FTDI original names. It use smaller names now. DL() will add something to the display list instead of Ft_App_WrCoCmd_Buffer ... The FTDI programmer Guide is also using this commands.

Dependents: FT800_RGB_demo FT800_RGB_demo2 FT800_demo_for_habr Temp_&_RH_at_TFT-demo ... more

Fork of FT800 by

The mbed is talking thru the SPI interface with the graphic engine. We have to set up a list of Commands and send them to the FT800 to get graphics.

Hardware

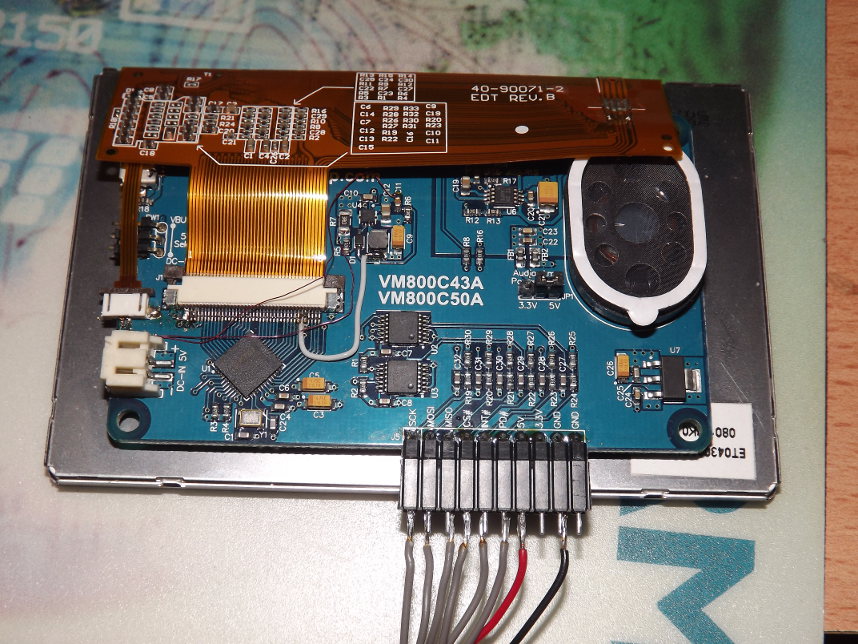

1. VM800C development modules from FTDI : http://www.ftdichip.com/Products/Modules/VM800C.html

The modules come with different size lcd. 3.5", 4.3" or 5" or without.

The picture shows a modified board, because my lcd had a different pinout. The mbed is connected to the pin header on the bottom.

The picture shows a modified board, because my lcd had a different pinout. The mbed is connected to the pin header on the bottom.

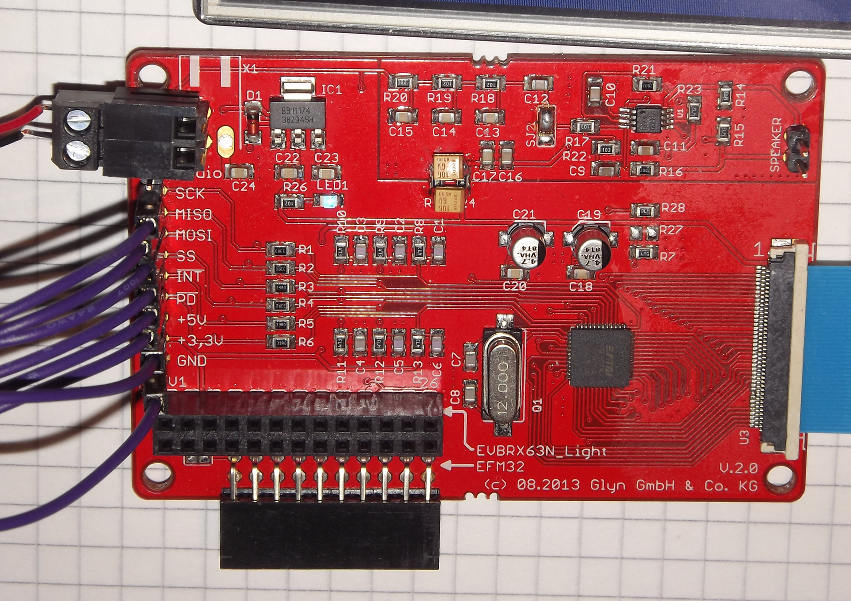

2. EVBEVE-FT800 board from GLYN: http://www.glyn.com/News-Events/Newsletter/Newsletter-2013/October-2013/A-quick-start-for-EVE-Requires-no-basic-knowledge-graphics-sound-and-touch-can-all-be-learned-in-minutes

The module has a 40 pin flex cable connector to connect a display out of the EDT series.

The mbed is connected via the pin header on the left. If you use this board with a EDT display you have to uncomment the #define Inv_Backlite in FT_LCD_Type.h, because the backlight dimming is inverted.

3. ConnectEVE board from MikroElektronika http://www.mikroe.com/add-on-boards/display/connecteve/#headers_10 The board has also a pin header to connect the mbed. - not tested, but it looks like the other boards.

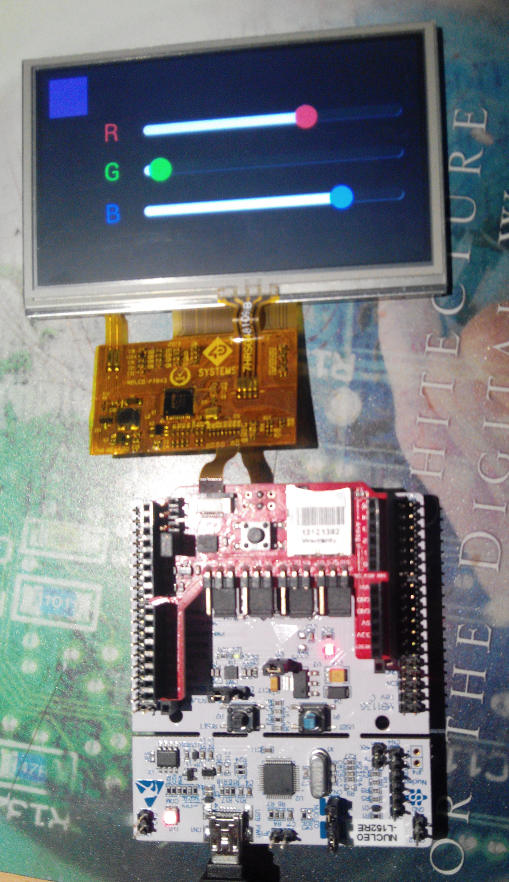

4. ADAM arduino shield http://www.4dsystems.com.au/product/4DLCD_FT843/ Component page : http://mbed.org/components/ADAM/

Works with the NUCLEO boards, but you have to patch three wires.

Connection

We need 5 signals to connect to the mbed. SCK, MOSI and MISO are connected to a SPI channel. SS is the chip select signal and PD work as powerdown. The additional INT signal is not used at the moment. It is possible to generate a interrupt signal, but at the moment you have to poll the status register of the FT800 to see if a command is finished.

Software

This lib is based on the demo code from FTDI. If you want to use it, you have to read the programming manual : http://www.ftdichip.com/Support/Documents/ProgramGuides/FT800%20Programmers%20Guide.pdf

See my demo : http://mbed.org/users/dreschpe/code/FT800_RGB_demo/

FT_Gpu_Hal.h@2:ab74a9a05970, 2014-01-04 (annotated)

- Committer:

- dreschpe

- Date:

- Sat Jan 04 13:56:38 2014 +0000

- Revision:

- 2:ab74a9a05970

- Parent:

- 1:bd671a31e765

- Child:

- 3:392d2c733c68

add doku

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| dreschpe | 0:5e013296b353 | 1 | /*! |

| dreschpe | 0:5e013296b353 | 2 | * \file FT_GPU_HAL.h |

| dreschpe | 0:5e013296b353 | 3 | * |

| dreschpe | 0:5e013296b353 | 4 | * \author FTDI |

| dreschpe | 0:5e013296b353 | 5 | * \date 2013.04.24 |

| dreschpe | 0:5e013296b353 | 6 | * |

| dreschpe | 0:5e013296b353 | 7 | * Copyright 2013 Future Technology Devices International Limited |

| dreschpe | 0:5e013296b353 | 8 | * |

| dreschpe | 0:5e013296b353 | 9 | * Project: FT800 or EVE compatible silicon |

| dreschpe | 0:5e013296b353 | 10 | * File Description: |

| dreschpe | 0:5e013296b353 | 11 | * This file defines the generic APIs of host access layer for the FT800 or EVE compatible silicon. |

| dreschpe | 2:ab74a9a05970 | 12 | * Application shall access FT800 or EVE resources over these APIs. In addition, there are |

| dreschpe | 0:5e013296b353 | 13 | * some helper functions defined for FT800 coprocessor engine as well as host commands. |

| dreschpe | 0:5e013296b353 | 14 | * Rivision History: |

| dreschpe | 2:ab74a9a05970 | 15 | * ported to mbed by Peter Drescher, DC2PD 2014 |

| dreschpe | 0:5e013296b353 | 16 | */ |

| dreschpe | 2:ab74a9a05970 | 17 | |

| dreschpe | 0:5e013296b353 | 18 | #ifndef FT_GPU_HAL_H |

| dreschpe | 0:5e013296b353 | 19 | #define FT_GPU_HAL_H |

| dreschpe | 0:5e013296b353 | 20 | |

| dreschpe | 0:5e013296b353 | 21 | #include "mbed.h" |

| dreschpe | 0:5e013296b353 | 22 | #include "FT_DataTypes.h" |

| dreschpe | 0:5e013296b353 | 23 | |

| dreschpe | 0:5e013296b353 | 24 | typedef enum { |

| dreschpe | 0:5e013296b353 | 25 | FT_GPU_I2C_MODE = 0, |

| dreschpe | 0:5e013296b353 | 26 | FT_GPU_SPI_MODE, |

| dreschpe | 0:5e013296b353 | 27 | |

| dreschpe | 0:5e013296b353 | 28 | FT_GPU_MODE_COUNT, |

| dreschpe | 0:5e013296b353 | 29 | FT_GPU_MODE_UNKNOWN = FT_GPU_MODE_COUNT |

| dreschpe | 0:5e013296b353 | 30 | } FT_GPU_HAL_MODE_E; |

| dreschpe | 0:5e013296b353 | 31 | |

| dreschpe | 0:5e013296b353 | 32 | typedef enum { |

| dreschpe | 0:5e013296b353 | 33 | FT_GPU_HAL_OPENED, |

| dreschpe | 0:5e013296b353 | 34 | FT_GPU_HAL_READING, |

| dreschpe | 0:5e013296b353 | 35 | FT_GPU_HAL_WRITING, |

| dreschpe | 0:5e013296b353 | 36 | FT_GPU_HAL_CLOSED, |

| dreschpe | 0:5e013296b353 | 37 | |

| dreschpe | 0:5e013296b353 | 38 | FT_GPU_HAL_STATUS_COUNT, |

| dreschpe | 0:5e013296b353 | 39 | FT_GPU_HAL_STATUS_ERROR = FT_GPU_HAL_STATUS_COUNT |

| dreschpe | 0:5e013296b353 | 40 | } FT_GPU_HAL_STATUS_E; |

| dreschpe | 0:5e013296b353 | 41 | |

| dreschpe | 0:5e013296b353 | 42 | typedef struct { |

| dreschpe | 0:5e013296b353 | 43 | ft_uint8_t reserved; |

| dreschpe | 0:5e013296b353 | 44 | } Ft_Gpu_App_Context_t; |

| dreschpe | 0:5e013296b353 | 45 | |

| dreschpe | 0:5e013296b353 | 46 | typedef struct { |

| dreschpe | 0:5e013296b353 | 47 | /* Total number channels for libmpsse */ |

| dreschpe | 0:5e013296b353 | 48 | ft_uint32_t TotalChannelNum; |

| dreschpe | 0:5e013296b353 | 49 | } Ft_Gpu_HalInit_t; |

| dreschpe | 0:5e013296b353 | 50 | |

| dreschpe | 0:5e013296b353 | 51 | typedef enum { |

| dreschpe | 0:5e013296b353 | 52 | FT_GPU_READ = 0, |

| dreschpe | 0:5e013296b353 | 53 | FT_GPU_WRITE, |

| dreschpe | 0:5e013296b353 | 54 | } FT_GPU_TRANSFERDIR_T; |

| dreschpe | 0:5e013296b353 | 55 | |

| dreschpe | 0:5e013296b353 | 56 | |

| dreschpe | 0:5e013296b353 | 57 | typedef struct { |

| dreschpe | 0:5e013296b353 | 58 | ft_uint32_t length; //IN and OUT |

| dreschpe | 0:5e013296b353 | 59 | ft_uint32_t address; |

| dreschpe | 0:5e013296b353 | 60 | ft_uint8_t *buffer; |

| dreschpe | 0:5e013296b353 | 61 | } Ft_Gpu_App_Transfer_t; |

| dreschpe | 0:5e013296b353 | 62 | |

| dreschpe | 0:5e013296b353 | 63 | class FT800 |

| dreschpe | 0:5e013296b353 | 64 | { |

| dreschpe | 0:5e013296b353 | 65 | public: |

| dreschpe | 0:5e013296b353 | 66 | FT800(PinName mosi, |

| dreschpe | 0:5e013296b353 | 67 | PinName miso, |

| dreschpe | 0:5e013296b353 | 68 | PinName sck, |

| dreschpe | 0:5e013296b353 | 69 | PinName ss, |

| dreschpe | 0:5e013296b353 | 70 | PinName intr, |

| dreschpe | 0:5e013296b353 | 71 | PinName pd); |

| dreschpe | 0:5e013296b353 | 72 | |

| dreschpe | 0:5e013296b353 | 73 | private: |

| dreschpe | 0:5e013296b353 | 74 | SPI _spi; |

| dreschpe | 0:5e013296b353 | 75 | DigitalOut _ss; |

| dreschpe | 0:5e013296b353 | 76 | DigitalOut _pd; |

| dreschpe | 0:5e013296b353 | 77 | InterruptIn _f800_isr; |

| dreschpe | 0:5e013296b353 | 78 | public: |

| dreschpe | 0:5e013296b353 | 79 | /* Global used for buffer optimization */ |

| dreschpe | 0:5e013296b353 | 80 | //Ft_Gpu_Hal_Context_t host,*phost; |

| dreschpe | 0:5e013296b353 | 81 | Ft_Gpu_App_Context_t app_header; |

| dreschpe | 0:5e013296b353 | 82 | ft_uint16_t ft_cmd_fifo_wp; //coprocessor fifo write pointer |

| dreschpe | 0:5e013296b353 | 83 | ft_uint16_t ft_dl_buff_wp; //display command memory write pointer |

| dreschpe | 0:5e013296b353 | 84 | FT_GPU_HAL_STATUS_E status; //OUT |

| dreschpe | 0:5e013296b353 | 85 | ft_void_t* hal_handle; //IN/OUT |

| dreschpe | 0:5e013296b353 | 86 | ft_uint32_t Ft_CmdBuffer_Index; |

| dreschpe | 0:5e013296b353 | 87 | ft_uint32_t Ft_DlBuffer_Index; |

| dreschpe | 0:5e013296b353 | 88 | ft_int16_t FT_DispWidth; |

| dreschpe | 0:5e013296b353 | 89 | ft_int16_t FT_DispHeight; |

| dreschpe | 0:5e013296b353 | 90 | ft_int16_t FT_DispHCycle; |

| dreschpe | 0:5e013296b353 | 91 | ft_int16_t FT_DispHOffset; |

| dreschpe | 0:5e013296b353 | 92 | ft_int16_t FT_DispHSync0; |

| dreschpe | 0:5e013296b353 | 93 | ft_int16_t FT_DispHSync1; |

| dreschpe | 0:5e013296b353 | 94 | ft_int16_t FT_DispVCycle; |

| dreschpe | 0:5e013296b353 | 95 | ft_int16_t FT_DispVOffset; |

| dreschpe | 0:5e013296b353 | 96 | ft_int16_t FT_DispVSync0; |

| dreschpe | 0:5e013296b353 | 97 | ft_int16_t FT_DispVSync1; |

| dreschpe | 0:5e013296b353 | 98 | ft_uint8_t FT_DispPCLK; |

| dreschpe | 0:5e013296b353 | 99 | ft_char8_t FT_DispSwizzle; |

| dreschpe | 0:5e013296b353 | 100 | ft_char8_t FT_DispPCLKPol; |

| dreschpe | 0:5e013296b353 | 101 | |

| dreschpe | 0:5e013296b353 | 102 | |

| dreschpe | 0:5e013296b353 | 103 | ft_void_t BootupConfig(void); |

| dreschpe | 0:5e013296b353 | 104 | ft_bool_t Bootup(void); |

| dreschpe | 0:5e013296b353 | 105 | |

| dreschpe | 0:5e013296b353 | 106 | |

| dreschpe | 0:5e013296b353 | 107 | /*The basic APIs Level 1*/ |

| dreschpe | 0:5e013296b353 | 108 | ft_bool_t Ft_Gpu_Hal_Init( ); |

| dreschpe | 0:5e013296b353 | 109 | ft_bool_t Ft_Gpu_Hal_Open( ); |

| dreschpe | 0:5e013296b353 | 110 | |

| dreschpe | 0:5e013296b353 | 111 | /*The APIs for reading/writing transfer continuously only with small buffer system*/ |

| dreschpe | 0:5e013296b353 | 112 | ft_void_t Ft_Gpu_Hal_StartTransfer(FT_GPU_TRANSFERDIR_T rw,ft_uint32_t addr); |

| dreschpe | 0:5e013296b353 | 113 | ft_uint8_t Ft_Gpu_Hal_Transfer8(ft_uint8_t value); |

| dreschpe | 0:5e013296b353 | 114 | ft_uint16_t Ft_Gpu_Hal_Transfer16(ft_uint16_t value); |

| dreschpe | 0:5e013296b353 | 115 | ft_uint32_t Ft_Gpu_Hal_Transfer32(ft_uint32_t value); |

| dreschpe | 0:5e013296b353 | 116 | ft_void_t Ft_Gpu_Hal_EndTransfer( ); |

| dreschpe | 0:5e013296b353 | 117 | |

| dreschpe | 0:5e013296b353 | 118 | /*Read & Write APIs for both burst and single transfer,depending on buffer size*/ |

| dreschpe | 0:5e013296b353 | 119 | ft_void_t Ft_Gpu_Hal_Read(Ft_Gpu_App_Transfer_t *transfer); |

| dreschpe | 0:5e013296b353 | 120 | ft_void_t Ft_Gpu_Hal_Write(Ft_Gpu_App_Transfer_t *transfer); |

| dreschpe | 0:5e013296b353 | 121 | |

| dreschpe | 0:5e013296b353 | 122 | ft_void_t Ft_Gpu_Hal_Close(); |

| dreschpe | 0:5e013296b353 | 123 | ft_void_t Ft_Gpu_Hal_DeInit(); |

| dreschpe | 0:5e013296b353 | 124 | |

| dreschpe | 0:5e013296b353 | 125 | /*Helper function APIs Read*/ |

| dreschpe | 0:5e013296b353 | 126 | ft_uint8_t Ft_Gpu_Hal_Rd8(ft_uint32_t addr); |

| dreschpe | 0:5e013296b353 | 127 | ft_uint16_t Ft_Gpu_Hal_Rd16(ft_uint32_t addr); |

| dreschpe | 0:5e013296b353 | 128 | ft_uint32_t Ft_Gpu_Hal_Rd32(ft_uint32_t addr); |

| dreschpe | 0:5e013296b353 | 129 | |

| dreschpe | 0:5e013296b353 | 130 | /*Helper function APIs Write*/ |

| dreschpe | 0:5e013296b353 | 131 | ft_void_t Ft_Gpu_Hal_Wr8(ft_uint32_t addr, ft_uint8_t v); |

| dreschpe | 0:5e013296b353 | 132 | ft_void_t Ft_Gpu_Hal_Wr16(ft_uint32_t addr, ft_uint16_t v); |

| dreschpe | 0:5e013296b353 | 133 | ft_void_t Ft_Gpu_Hal_Wr32(ft_uint32_t addr, ft_uint32_t v); |

| dreschpe | 0:5e013296b353 | 134 | |

| dreschpe | 0:5e013296b353 | 135 | /*******************************************************************************/ |

| dreschpe | 0:5e013296b353 | 136 | /*******************************************************************************/ |

| dreschpe | 0:5e013296b353 | 137 | /*APIs for coprocessor Fifo read/write and space management*/ |

| dreschpe | 0:5e013296b353 | 138 | ft_void_t Ft_Gpu_Hal_Updatecmdfifo(ft_uint16_t count); |

| dreschpe | 0:5e013296b353 | 139 | ft_void_t Ft_Gpu_Hal_WrCmd32(ft_uint32_t cmd); |

| dreschpe | 0:5e013296b353 | 140 | ft_void_t Ft_Gpu_Hal_WrCmdBuf(ft_uint8_t *buffer,ft_uint16_t count); |

| dreschpe | 0:5e013296b353 | 141 | ft_void_t Ft_Gpu_Hal_WaitCmdfifo_empty(); |

| dreschpe | 0:5e013296b353 | 142 | ft_void_t Ft_Gpu_Hal_ResetCmdFifo(); |

| dreschpe | 0:5e013296b353 | 143 | ft_void_t Ft_Gpu_Hal_CheckCmdBuffer(ft_uint16_t count); |

| dreschpe | 0:5e013296b353 | 144 | ft_void_t Ft_Gpu_Hal_ResetDLBuffer(); |

| dreschpe | 0:5e013296b353 | 145 | |

| dreschpe | 0:5e013296b353 | 146 | ft_void_t Ft_Gpu_Hal_StartCmdTransfer(FT_GPU_TRANSFERDIR_T rw, ft_uint16_t count); |

| dreschpe | 0:5e013296b353 | 147 | ft_void_t Ft_Gpu_Hal_Powercycle(ft_bool_t up); |

| dreschpe | 0:5e013296b353 | 148 | |

| dreschpe | 0:5e013296b353 | 149 | |

| dreschpe | 0:5e013296b353 | 150 | /*******************************************************************************/ |

| dreschpe | 0:5e013296b353 | 151 | /*******************************************************************************/ |

| dreschpe | 0:5e013296b353 | 152 | /*APIs for Host Commands*/ |

| dreschpe | 0:5e013296b353 | 153 | typedef enum { |

| dreschpe | 0:5e013296b353 | 154 | FT_GPU_INTERNAL_OSC = 0x48, //default |

| dreschpe | 0:5e013296b353 | 155 | FT_GPU_EXTERNAL_OSC = 0x44, |

| dreschpe | 0:5e013296b353 | 156 | } FT_GPU_PLL_SOURCE_T; |

| dreschpe | 0:5e013296b353 | 157 | typedef enum { |

| dreschpe | 0:5e013296b353 | 158 | FT_GPU_PLL_48M = 0x62, //default |

| dreschpe | 0:5e013296b353 | 159 | FT_GPU_PLL_36M = 0x61, |

| dreschpe | 0:5e013296b353 | 160 | FT_GPU_PLL_24M = 0x64, |

| dreschpe | 0:5e013296b353 | 161 | } FT_GPU_PLL_FREQ_T; |

| dreschpe | 0:5e013296b353 | 162 | |

| dreschpe | 0:5e013296b353 | 163 | typedef enum { |

| dreschpe | 0:5e013296b353 | 164 | FT_GPU_ACTIVE_M = 0x00, |

| dreschpe | 0:5e013296b353 | 165 | FT_GPU_STANDBY_M = 0x41,//default |

| dreschpe | 0:5e013296b353 | 166 | FT_GPU_SLEEP_M = 0x42, |

| dreschpe | 0:5e013296b353 | 167 | FT_GPU_POWERDOWN_M = 0x50, |

| dreschpe | 0:5e013296b353 | 168 | } FT_GPU_POWER_MODE_T; |

| dreschpe | 0:5e013296b353 | 169 | |

| dreschpe | 0:5e013296b353 | 170 | #define FT_GPU_CORE_RESET (0x68) |

| dreschpe | 0:5e013296b353 | 171 | |

| dreschpe | 0:5e013296b353 | 172 | ft_int32_t hal_strlen(const ft_char8_t *s); |

| dreschpe | 0:5e013296b353 | 173 | ft_void_t Ft_Gpu_Hal_Sleep(ft_uint16_t ms); |

| dreschpe | 0:5e013296b353 | 174 | ft_void_t Ft_Gpu_ClockSelect(FT_GPU_PLL_SOURCE_T pllsource); |

| dreschpe | 0:5e013296b353 | 175 | ft_void_t Ft_Gpu_PLL_FreqSelect(FT_GPU_PLL_FREQ_T freq); |

| dreschpe | 0:5e013296b353 | 176 | ft_void_t Ft_Gpu_PowerModeSwitch(FT_GPU_POWER_MODE_T pwrmode); |

| dreschpe | 0:5e013296b353 | 177 | ft_void_t Ft_Gpu_CoreReset(); |

| dreschpe | 0:5e013296b353 | 178 | //ft_void_t Ft_Gpu_Hal_StartTransfer( ,FT_GPU_TRANSFERDIR_T rw,ft_uint32_t addr); |

| dreschpe | 0:5e013296b353 | 179 | ft_void_t Ft_Gpu_Hal_WrMem(ft_uint32_t addr, const ft_uint8_t *buffer, ft_uint32_t length); |

| dreschpe | 0:5e013296b353 | 180 | ft_void_t Ft_Gpu_Hal_WrMemFromFlash(ft_uint32_t addr,const ft_prog_uchar8_t *buffer, ft_uint32_t length); |

| dreschpe | 0:5e013296b353 | 181 | ft_void_t Ft_Gpu_Hal_WrCmdBufFromFlash(FT_PROGMEM ft_prog_uchar8_t *buffer,ft_uint16_t count); |

| dreschpe | 0:5e013296b353 | 182 | ft_void_t Ft_Gpu_Hal_RdMem(ft_uint32_t addr, ft_uint8_t *buffer, ft_uint32_t length); |

| dreschpe | 0:5e013296b353 | 183 | ft_void_t Ft_Gpu_Hal_WaitLogo_Finish(); |

| dreschpe | 0:5e013296b353 | 184 | ft_uint8_t Ft_Gpu_Hal_TransferString(const ft_char8_t *string); |

| dreschpe | 0:5e013296b353 | 185 | ft_void_t Ft_Gpu_HostCommand(ft_uint8_t cmd); |

| dreschpe | 0:5e013296b353 | 186 | ft_int32_t Ft_Gpu_Hal_Dec2Ascii(ft_char8_t *pSrc,ft_int32_t value); |

| dreschpe | 0:5e013296b353 | 187 | |

| dreschpe | 0:5e013296b353 | 188 | ft_void_t Ft_Gpu_CoCmd_Text(ft_int16_t x, ft_int16_t y, ft_int16_t font, ft_uint16_t options, const ft_char8_t* s); |

| dreschpe | 0:5e013296b353 | 189 | ft_void_t Ft_Gpu_CoCmd_Number(ft_int16_t x, ft_int16_t y, ft_int16_t font, ft_uint16_t options, ft_int32_t n); |

| dreschpe | 0:5e013296b353 | 190 | ft_void_t Ft_Gpu_CoCmd_LoadIdentity(); |

| dreschpe | 0:5e013296b353 | 191 | ft_void_t Ft_Gpu_CoCmd_Toggle(ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t font, ft_uint16_t options, ft_uint16_t state, const ft_char8_t* s); |

| dreschpe | 0:5e013296b353 | 192 | ft_void_t Ft_Gpu_CoCmd_Gauge(ft_int16_t x, ft_int16_t y, ft_int16_t r, ft_uint16_t options, ft_uint16_t major, ft_uint16_t minor, ft_uint16_t val, ft_uint16_t range); |

| dreschpe | 0:5e013296b353 | 193 | ft_void_t Ft_Gpu_CoCmd_RegRead(ft_uint32_t ptr, ft_uint32_t result); |

| dreschpe | 0:5e013296b353 | 194 | ft_void_t Ft_Gpu_CoCmd_GetProps(ft_uint32_t ptr, ft_uint32_t w, ft_uint32_t h); |

| dreschpe | 0:5e013296b353 | 195 | ft_void_t Ft_Gpu_CoCmd_Memcpy(ft_uint32_t dest, ft_uint32_t src, ft_uint32_t num); |

| dreschpe | 0:5e013296b353 | 196 | ft_void_t Ft_Gpu_CoCmd_Spinner(ft_int16_t x, ft_int16_t y, ft_uint16_t style, ft_uint16_t scale); |

| dreschpe | 0:5e013296b353 | 197 | ft_void_t Ft_Gpu_CoCmd_BgColor(ft_uint32_t c); |

| dreschpe | 0:5e013296b353 | 198 | ft_void_t Ft_Gpu_CoCmd_Swap(); |

| dreschpe | 0:5e013296b353 | 199 | ft_void_t Ft_Gpu_CoCmd_Inflate(ft_uint32_t ptr); |

| dreschpe | 0:5e013296b353 | 200 | ft_void_t Ft_Gpu_CoCmd_Translate(ft_int32_t tx, ft_int32_t ty); |

| dreschpe | 0:5e013296b353 | 201 | ft_void_t Ft_Gpu_CoCmd_Stop(); |

| dreschpe | 0:5e013296b353 | 202 | ft_void_t Ft_Gpu_CoCmd_Slider(ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_uint16_t options, ft_uint16_t val, ft_uint16_t range); |

| dreschpe | 0:5e013296b353 | 203 | ft_void_t Ft_Gpu_CoCmd_Interrupt(ft_uint32_t ms); |

| dreschpe | 0:5e013296b353 | 204 | ft_void_t Ft_Gpu_CoCmd_FgColor(ft_uint32_t c); |

| dreschpe | 0:5e013296b353 | 205 | ft_void_t Ft_Gpu_CoCmd_Rotate(ft_int32_t a); |

| dreschpe | 0:5e013296b353 | 206 | ft_void_t Ft_Gpu_CoCmd_Button(ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_int16_t font, ft_uint16_t options, const ft_char8_t* s); |

| dreschpe | 0:5e013296b353 | 207 | ft_void_t Ft_Gpu_CoCmd_MemWrite(ft_uint32_t ptr, ft_uint32_t num); |

| dreschpe | 0:5e013296b353 | 208 | ft_void_t Ft_Gpu_CoCmd_Scrollbar(ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_uint16_t options, ft_uint16_t val, ft_uint16_t size, ft_uint16_t range); |

| dreschpe | 0:5e013296b353 | 209 | ft_void_t Ft_Gpu_CoCmd_GetMatrix(ft_int32_t a, ft_int32_t b, ft_int32_t c, ft_int32_t d, ft_int32_t e, ft_int32_t f); |

| dreschpe | 0:5e013296b353 | 210 | ft_void_t Ft_Gpu_CoCmd_Sketch(ft_int16_t x, ft_int16_t y, ft_uint16_t w, ft_uint16_t h, ft_uint32_t ptr, ft_uint16_t format); |

| dreschpe | 0:5e013296b353 | 211 | ft_void_t Ft_Gpu_CoCmd_MemSet(ft_uint32_t ptr, ft_uint32_t value, ft_uint32_t num); |

| dreschpe | 0:5e013296b353 | 212 | ft_void_t Ft_Gpu_CoCmd_Calibrate(ft_uint32_t result); |

| dreschpe | 0:5e013296b353 | 213 | ft_void_t Ft_Gpu_CoCmd_SetFont(ft_uint32_t font, ft_uint32_t ptr); |

| dreschpe | 0:5e013296b353 | 214 | ft_void_t Ft_Gpu_CoCmd_Bitmap_Transform(ft_int32_t x0, ft_int32_t y0, ft_int32_t x1, ft_int32_t y1, ft_int32_t x2, ft_int32_t y2, ft_int32_t tx0, ft_int32_t ty0, ft_int32_t tx1, ft_int32_t ty1, ft_int32_t tx2, ft_int32_t ty2, ft_uint16_t result); |

| dreschpe | 0:5e013296b353 | 215 | ft_void_t Ft_Gpu_CoCmd_GradColor(ft_uint32_t c); |

| dreschpe | 0:5e013296b353 | 216 | ft_void_t Ft_Gpu_CoCmd_Append(ft_uint32_t ptr, ft_uint32_t num); |

| dreschpe | 0:5e013296b353 | 217 | ft_void_t Ft_Gpu_CoCmd_MemZero(ft_uint32_t ptr, ft_uint32_t num); |

| dreschpe | 0:5e013296b353 | 218 | ft_void_t Ft_Gpu_CoCmd_Scale(ft_int32_t sx, ft_int32_t sy); |

| dreschpe | 0:5e013296b353 | 219 | ft_void_t Ft_Gpu_CoCmd_Clock(ft_int16_t x, ft_int16_t y, ft_int16_t r, ft_uint16_t options, ft_uint16_t h, ft_uint16_t m, ft_uint16_t s, ft_uint16_t ms); |

| dreschpe | 0:5e013296b353 | 220 | ft_void_t Ft_Gpu_CoCmd_Gradient(ft_int16_t x0, ft_int16_t y0, ft_uint32_t rgb0, ft_int16_t x1, ft_int16_t y1, ft_uint32_t rgb1); |

| dreschpe | 0:5e013296b353 | 221 | ft_void_t Ft_Gpu_CoCmd_SetMatrix(); |

| dreschpe | 0:5e013296b353 | 222 | ft_void_t Ft_Gpu_CoCmd_Track(ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_int16_t tag); |

| dreschpe | 0:5e013296b353 | 223 | ft_void_t Ft_Gpu_CoCmd_GetPtr(ft_uint32_t result); |

| dreschpe | 0:5e013296b353 | 224 | ft_void_t Ft_Gpu_CoCmd_Progress(ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_uint16_t options, ft_uint16_t val, ft_uint16_t range); |

| dreschpe | 0:5e013296b353 | 225 | ft_void_t Ft_Gpu_CoCmd_ColdStart(); |

| dreschpe | 0:5e013296b353 | 226 | ft_void_t Ft_Gpu_CoCmd_Keys(ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_int16_t font, ft_uint16_t options, const ft_char8_t* s); |

| dreschpe | 0:5e013296b353 | 227 | ft_void_t Ft_Gpu_CoCmd_Dial(ft_int16_t x, ft_int16_t y, ft_int16_t r, ft_uint16_t options, ft_uint16_t val); |

| dreschpe | 0:5e013296b353 | 228 | ft_void_t Ft_Gpu_CoCmd_LoadImage(ft_uint32_t ptr, ft_uint32_t options); |

| dreschpe | 0:5e013296b353 | 229 | ft_void_t Ft_Gpu_CoCmd_Dlstart(); |

| dreschpe | 0:5e013296b353 | 230 | ft_void_t Ft_Gpu_CoCmd_Snapshot(ft_uint32_t ptr); |

| dreschpe | 0:5e013296b353 | 231 | ft_void_t Ft_Gpu_CoCmd_ScreenSaver(); |

| dreschpe | 0:5e013296b353 | 232 | ft_void_t Ft_Gpu_CoCmd_Memcrc(ft_uint32_t ptr, ft_uint32_t num, ft_uint32_t result); |

| dreschpe | 0:5e013296b353 | 233 | |

| dreschpe | 0:5e013296b353 | 234 | ft_void_t Ft_Gpu_CoCmd_Logo(); |

| dreschpe | 0:5e013296b353 | 235 | |

| dreschpe | 0:5e013296b353 | 236 | ft_void_t Ft_Gpu_Copro_SendCmd( ft_uint32_t cmd); |

| dreschpe | 0:5e013296b353 | 237 | ft_void_t Ft_Gpu_CoCmd_SendStr( const ft_char8_t *s); |

| dreschpe | 0:5e013296b353 | 238 | ft_void_t Ft_Gpu_CoCmd_StartFunc( ft_uint16_t count); |

| dreschpe | 0:5e013296b353 | 239 | ft_void_t Ft_Gpu_CoCmd_EndFunc( ft_uint16_t count); |

| dreschpe | 0:5e013296b353 | 240 | ft_void_t Ft_Gpu_CoCmd_TouchTransform( ft_int32_t x0, ft_int32_t y0, ft_int32_t x1, ft_int32_t y1, ft_int32_t x2, ft_int32_t y2, ft_int32_t tx0, ft_int32_t ty0, ft_int32_t tx1, ft_int32_t ty1, ft_int32_t tx2, ft_int32_t ty2, ft_uint16_t result); |

| dreschpe | 0:5e013296b353 | 241 | ft_void_t Ft_Gpu_CoCmd_BitmapTransform( ft_int32_t x0, ft_int32_t y0, ft_int32_t x1, ft_int32_t y1, ft_int32_t x2, ft_int32_t y2, ft_int32_t tx0, ft_int32_t ty0, ft_int32_t tx1, ft_int32_t ty1, ft_int32_t tx2, ft_int32_t ty2, ft_uint16_t result); |

| dreschpe | 0:5e013296b353 | 242 | ft_void_t Ft_Gpu_CoCmd_MemCrc( ft_uint32_t ptr, ft_uint32_t num, ft_uint32_t result); |

| dreschpe | 0:5e013296b353 | 243 | |

| dreschpe | 0:5e013296b353 | 244 | ft_uint16_t Ft_Gpu_Cmdfifo_Freespace( ); |

| dreschpe | 0:5e013296b353 | 245 | |

| dreschpe | 0:5e013296b353 | 246 | ft_void_t Ft_App_WrCoCmd_Buffer(ft_uint32_t cmd); |

| dreschpe | 0:5e013296b353 | 247 | ft_void_t Ft_App_WrDlCmd_Buffer(ft_uint32_t cmd); |

| dreschpe | 0:5e013296b353 | 248 | ft_void_t Ft_App_Flush_DL_Buffer(); |

| dreschpe | 0:5e013296b353 | 249 | ft_void_t Ft_App_Flush_Co_Buffer(); |

| dreschpe | 0:5e013296b353 | 250 | ft_void_t TFT_fadeout(); |

| dreschpe | 0:5e013296b353 | 251 | ft_void_t TFT_fadein(); |

| dreschpe | 0:5e013296b353 | 252 | ft_void_t GPU_DLSwap(ft_uint8_t DL_Swap_Type); |

| dreschpe | 0:5e013296b353 | 253 | |

| dreschpe | 1:bd671a31e765 | 254 | ft_void_t Ft_Sound_ON(); |

| dreschpe | 1:bd671a31e765 | 255 | ft_void_t Ft_Sound_OFF(); |

| dreschpe | 0:5e013296b353 | 256 | |

| dreschpe | 0:5e013296b353 | 257 | }; // end of class |

| dreschpe | 0:5e013296b353 | 258 | |

| dreschpe | 0:5e013296b353 | 259 | #endif /*FT_GPU_HAL_H*/ |

| dreschpe | 0:5e013296b353 | 260 | |

| dreschpe | 0:5e013296b353 | 261 | |

| dreschpe | 0:5e013296b353 | 262 |

EVE FT800

EVE FT800

ADAM

ADAM