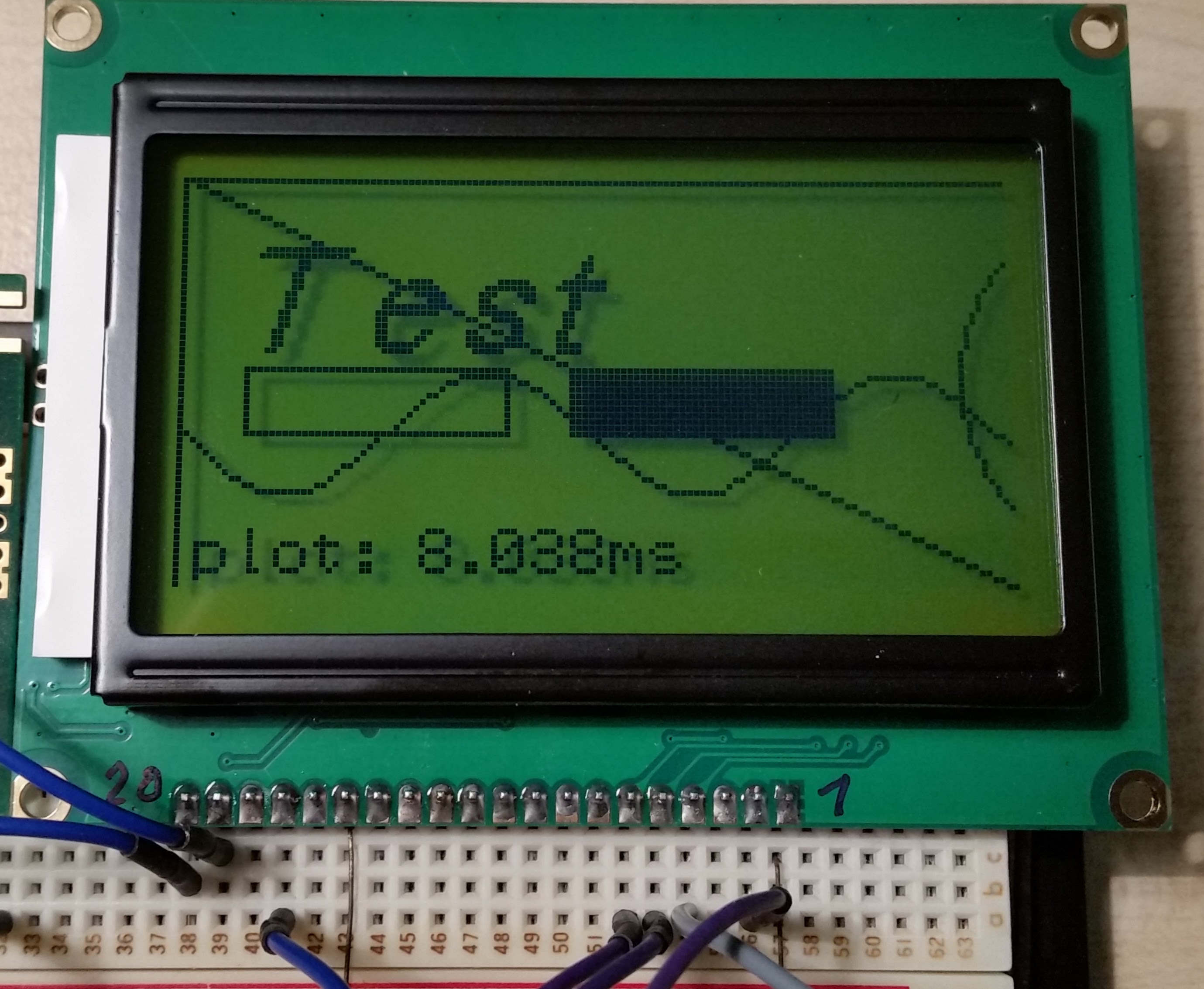

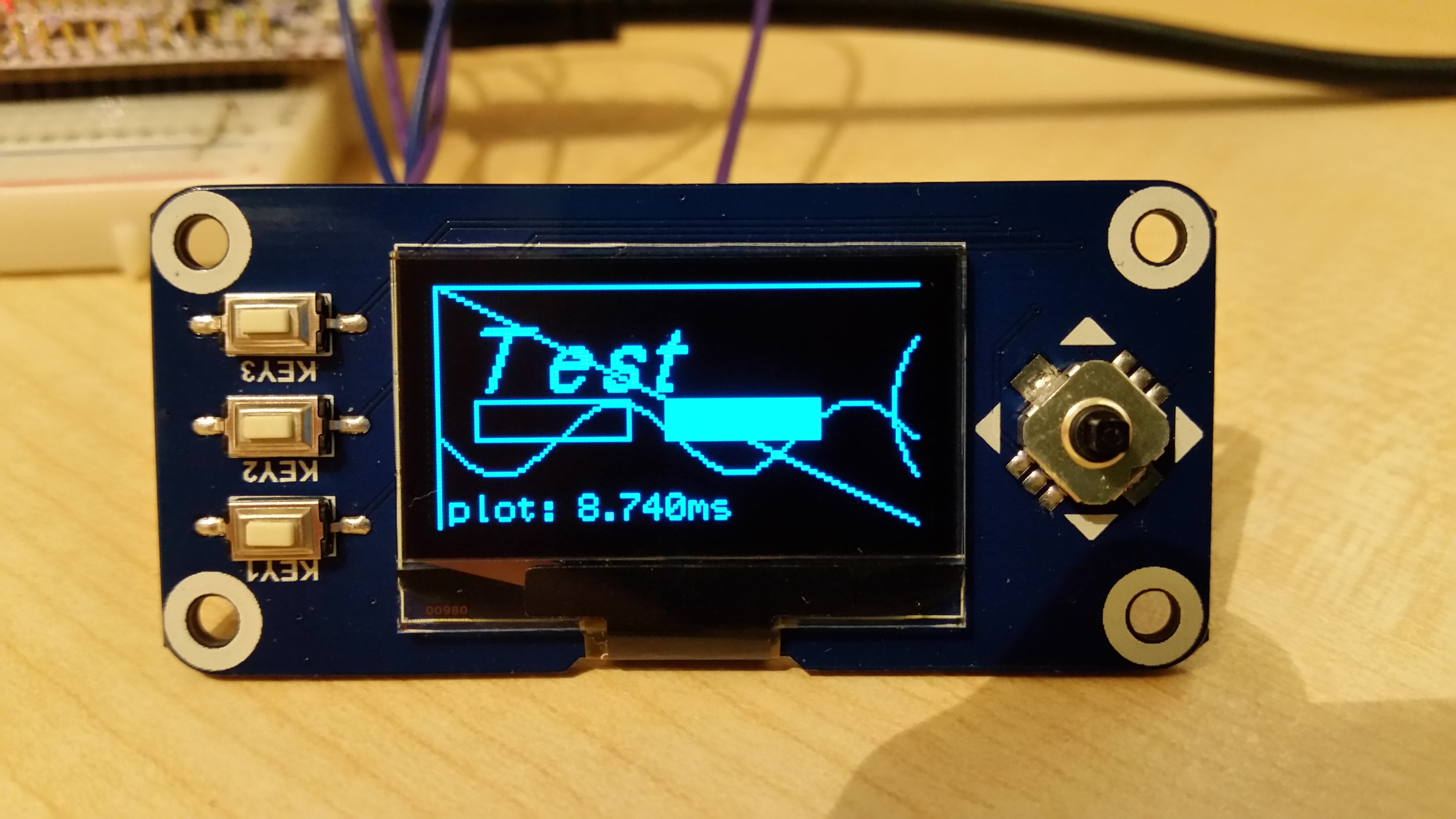

UniGraphic-Fork for ST7920-LCD-controller and SH1106. Tested with 128x64 LCD with SPI and 128x64-OLED with IIC

Dependents: UniGraphic-St7920-Test AfficheurUTILECO

Fork of UniGraphic by

Fork of the UniGraphic-Library for monochrome LCDs with ST7920 controller and 128x64-IIC-OLED-Display with SH1106-Controller

Had to adapt LCD for following reasons:

- Give access to screenbuffer buffer[] to parent class

- pixel() and pixel_read() as they are hardware-dependent

- added reset-pin to IIC-Interface

GraphicDisplay:: sends buffer to LCD when auto_update is set to true.

Testprogram for ST7920 can be found here:

https://developer.mbed.org/users/charly/code/UniGraphic-St7920-Test/

Protocols/I2C_bus.cpp@36:668396f861d2, 2018-04-22 (annotated)

- Committer:

- charly

- Date:

- Sun Apr 22 21:41:24 2018 +0000

- Revision:

- 36:668396f861d2

- Parent:

- 33:f87f06292637

Added SH1106 for OLED Display 128x64 via IIC

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| dreschpe | 33:f87f06292637 | 1 | /* mbed UniGraphic library - I2C protocol class |

| dreschpe | 33:f87f06292637 | 2 | * Copyright (c) 2017 Peter Drescher |

| dreschpe | 33:f87f06292637 | 3 | * Released under the MIT License: http://mbed.org/license/mit |

| dreschpe | 33:f87f06292637 | 4 | * |

| dreschpe | 33:f87f06292637 | 5 | * THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR |

| dreschpe | 33:f87f06292637 | 6 | * IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, |

| dreschpe | 33:f87f06292637 | 7 | * FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE |

| dreschpe | 33:f87f06292637 | 8 | * AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER |

| dreschpe | 33:f87f06292637 | 9 | * LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, |

| dreschpe | 33:f87f06292637 | 10 | * OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN |

| dreschpe | 33:f87f06292637 | 11 | * THE SOFTWARE. |

| dreschpe | 33:f87f06292637 | 12 | */ |

| dreschpe | 33:f87f06292637 | 13 | |

| dreschpe | 33:f87f06292637 | 14 | #include "I2C_bus.h" |

| dreschpe | 33:f87f06292637 | 15 | |

| charly | 36:668396f861d2 | 16 | I2C_bus::I2C_bus(int Hz, int address, PinName sda, PinName scl, PinName reset) |

| charly | 36:668396f861d2 | 17 | : _i2c(sda,scl), _reset(reset) |

| dreschpe | 33:f87f06292637 | 18 | { |

| dreschpe | 33:f87f06292637 | 19 | _i2c.frequency(Hz); |

| dreschpe | 33:f87f06292637 | 20 | _address = address; |

| charly | 36:668396f861d2 | 21 | _reset = 1; |

| charly | 36:668396f861d2 | 22 | hw_reset(); |

| dreschpe | 33:f87f06292637 | 23 | } |

| dreschpe | 33:f87f06292637 | 24 | |

| dreschpe | 33:f87f06292637 | 25 | void I2C_bus::wr_cmd8(unsigned char cmd) |

| dreschpe | 33:f87f06292637 | 26 | { |

| dreschpe | 33:f87f06292637 | 27 | char tmp[2]; |

| dreschpe | 33:f87f06292637 | 28 | tmp[0] = 0x00; //command |

| dreschpe | 33:f87f06292637 | 29 | tmp[1] = cmd; |

| dreschpe | 33:f87f06292637 | 30 | _i2c.write(_address,tmp,2); |

| dreschpe | 33:f87f06292637 | 31 | } |

| dreschpe | 33:f87f06292637 | 32 | void I2C_bus::wr_data8(unsigned char data) |

| dreschpe | 33:f87f06292637 | 33 | { |

| charly | 36:668396f861d2 | 34 | char tmp[2]; |

| charly | 36:668396f861d2 | 35 | tmp[0] = 0x40; //data mode |

| charly | 36:668396f861d2 | 36 | tmp[1] = data; |

| charly | 36:668396f861d2 | 37 | _i2c.write(_address,tmp,2); // write |

| dreschpe | 33:f87f06292637 | 38 | } |

| dreschpe | 33:f87f06292637 | 39 | void I2C_bus::wr_cmd16(unsigned short cmd) |

| dreschpe | 33:f87f06292637 | 40 | { |

| dreschpe | 33:f87f06292637 | 41 | char tmp[3]; |

| dreschpe | 33:f87f06292637 | 42 | tmp[0] = 00; //command |

| dreschpe | 33:f87f06292637 | 43 | tmp[1] = cmd>>8; |

| dreschpe | 33:f87f06292637 | 44 | tmp[2] = cmd&0xFF; |

| dreschpe | 33:f87f06292637 | 45 | |

| dreschpe | 33:f87f06292637 | 46 | _i2c.write(_address,tmp,3); |

| dreschpe | 33:f87f06292637 | 47 | } |

| dreschpe | 33:f87f06292637 | 48 | void I2C_bus::wr_data16(unsigned short data) |

| dreschpe | 33:f87f06292637 | 49 | { |

| dreschpe | 33:f87f06292637 | 50 | _i2c.write(data>>8); // write 8bit |

| dreschpe | 33:f87f06292637 | 51 | _i2c.write(data&0xFF); // write 8bit |

| dreschpe | 33:f87f06292637 | 52 | } |

| dreschpe | 33:f87f06292637 | 53 | void I2C_bus::wr_gram(unsigned short data) |

| dreschpe | 33:f87f06292637 | 54 | { |

| dreschpe | 33:f87f06292637 | 55 | _i2c.write(data>>8); // write 8bit |

| dreschpe | 33:f87f06292637 | 56 | _i2c.write(data&0xFF); // write 8bit |

| dreschpe | 33:f87f06292637 | 57 | } |

| dreschpe | 33:f87f06292637 | 58 | void I2C_bus::wr_gram(unsigned short data, unsigned int count) |

| dreschpe | 33:f87f06292637 | 59 | { |

| dreschpe | 33:f87f06292637 | 60 | _i2c.start(); |

| dreschpe | 33:f87f06292637 | 61 | _i2c.write(_address); |

| dreschpe | 33:f87f06292637 | 62 | _i2c.write(0x40); // data continue |

| dreschpe | 33:f87f06292637 | 63 | if((data>>8)==(data&0xFF)) |

| dreschpe | 33:f87f06292637 | 64 | { |

| dreschpe | 33:f87f06292637 | 65 | count<<=1; |

| dreschpe | 33:f87f06292637 | 66 | while(count) |

| dreschpe | 33:f87f06292637 | 67 | { |

| dreschpe | 33:f87f06292637 | 68 | _i2c.write(data); // write 8bit |

| dreschpe | 33:f87f06292637 | 69 | count--; |

| dreschpe | 33:f87f06292637 | 70 | } |

| dreschpe | 33:f87f06292637 | 71 | } |

| dreschpe | 33:f87f06292637 | 72 | else |

| dreschpe | 33:f87f06292637 | 73 | { |

| dreschpe | 33:f87f06292637 | 74 | while(count) |

| dreschpe | 33:f87f06292637 | 75 | { |

| dreschpe | 33:f87f06292637 | 76 | _i2c.write(data>>8); // write 8bit |

| dreschpe | 33:f87f06292637 | 77 | _i2c.write(data&0xFF); // write 8bit |

| dreschpe | 33:f87f06292637 | 78 | count--; |

| dreschpe | 33:f87f06292637 | 79 | } |

| dreschpe | 33:f87f06292637 | 80 | } |

| dreschpe | 33:f87f06292637 | 81 | _i2c.stop(); |

| dreschpe | 33:f87f06292637 | 82 | } |

| dreschpe | 33:f87f06292637 | 83 | void I2C_bus::wr_grambuf(unsigned short* data, unsigned int lenght) |

| dreschpe | 33:f87f06292637 | 84 | { |

| dreschpe | 33:f87f06292637 | 85 | _i2c.start(); |

| dreschpe | 33:f87f06292637 | 86 | _i2c.write(_address); |

| dreschpe | 33:f87f06292637 | 87 | _i2c.write(0x40); // data continue |

| dreschpe | 33:f87f06292637 | 88 | while(lenght) |

| dreschpe | 33:f87f06292637 | 89 | { |

| charly | 36:668396f861d2 | 90 | //_i2c.write((*data)>>8); // write high 8bit |

| charly | 36:668396f861d2 | 91 | _i2c.write((*data)&0xFF); // write low 8bit |

| charly | 36:668396f861d2 | 92 | _i2c.write((*data)>>8); // write high 8bit |

| dreschpe | 33:f87f06292637 | 93 | data++; |

| dreschpe | 33:f87f06292637 | 94 | lenght--; |

| dreschpe | 33:f87f06292637 | 95 | } |

| dreschpe | 33:f87f06292637 | 96 | _i2c.stop(); |

| dreschpe | 33:f87f06292637 | 97 | } |

| dreschpe | 33:f87f06292637 | 98 | |

| dreschpe | 33:f87f06292637 | 99 | void I2C_bus::hw_reset() |

| dreschpe | 33:f87f06292637 | 100 | { |

| charly | 36:668396f861d2 | 101 | wait_ms(15); |

| charly | 36:668396f861d2 | 102 | _reset = 0; // display reset |

| charly | 36:668396f861d2 | 103 | wait_ms(2); |

| charly | 36:668396f861d2 | 104 | _reset = 1; // end reset |

| charly | 36:668396f861d2 | 105 | wait_ms(100); |

| dreschpe | 33:f87f06292637 | 106 | } |

| dreschpe | 33:f87f06292637 | 107 | void I2C_bus::BusEnable(bool enable) |

| dreschpe | 33:f87f06292637 | 108 | { |

| dreschpe | 33:f87f06292637 | 109 | } |

| dreschpe | 33:f87f06292637 | 110 | |

| dreschpe | 33:f87f06292637 | 111 | void I2C_bus::reg_select(unsigned char reg, bool forread) |

| dreschpe | 33:f87f06292637 | 112 | { |

| dreschpe | 33:f87f06292637 | 113 | } |

| dreschpe | 33:f87f06292637 | 114 | |

| dreschpe | 33:f87f06292637 | 115 | unsigned int I2C_bus::rd_reg_data32(unsigned char reg) |

| dreschpe | 33:f87f06292637 | 116 | { |

| dreschpe | 33:f87f06292637 | 117 | return 0; |

| dreschpe | 33:f87f06292637 | 118 | } |

| dreschpe | 33:f87f06292637 | 119 | |

| dreschpe | 33:f87f06292637 | 120 | unsigned int I2C_bus::rd_extcreg_data32(unsigned char reg, unsigned char SPIreadenablecmd) |

| dreschpe | 33:f87f06292637 | 121 | { |

| dreschpe | 33:f87f06292637 | 122 | return 0; |

| dreschpe | 33:f87f06292637 | 123 | } |

| dreschpe | 33:f87f06292637 | 124 | |

| dreschpe | 33:f87f06292637 | 125 | void I2C_bus::dummyread() |

| dreschpe | 33:f87f06292637 | 126 | { |

| dreschpe | 33:f87f06292637 | 127 | } |

| dreschpe | 33:f87f06292637 | 128 | |

| dreschpe | 33:f87f06292637 | 129 | unsigned short I2C_bus::rd_gram(bool convert) |

| dreschpe | 33:f87f06292637 | 130 | { |

| dreschpe | 33:f87f06292637 | 131 | return (0); |

| dreschpe | 33:f87f06292637 | 132 | } |

| dreschpe | 33:f87f06292637 | 133 | |

| dreschpe | 33:f87f06292637 | 134 | unsigned short I2C_bus::reg_read(unsigned char reg) |

| dreschpe | 33:f87f06292637 | 135 | { |

| dreschpe | 33:f87f06292637 | 136 | return (0); |

| dreschpe | 33:f87f06292637 | 137 | } |

| dreschpe | 33:f87f06292637 | 138 | |

| dreschpe | 33:f87f06292637 | 139 | void I2C_bus::reg_write(unsigned char reg, unsigned short data) |

| dreschpe | 33:f87f06292637 | 140 | { |

| dreschpe | 33:f87f06292637 | 141 | } |